在一个PCB的设计过程中,原理图是底层建筑,而PCB是上层建筑。在生成网络表导入到PCB前,必须要保证原理图的正确性。

在绘制完原理图后,我们可以使用一些常规的查错方式避免一些低级的错误。

首先进行工程的编译检查设置:

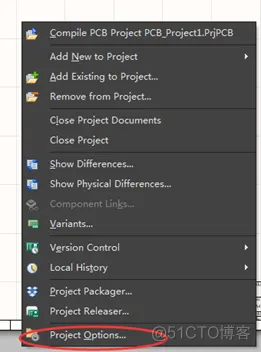

1:可以在工程树中右键工程文件进行设置:

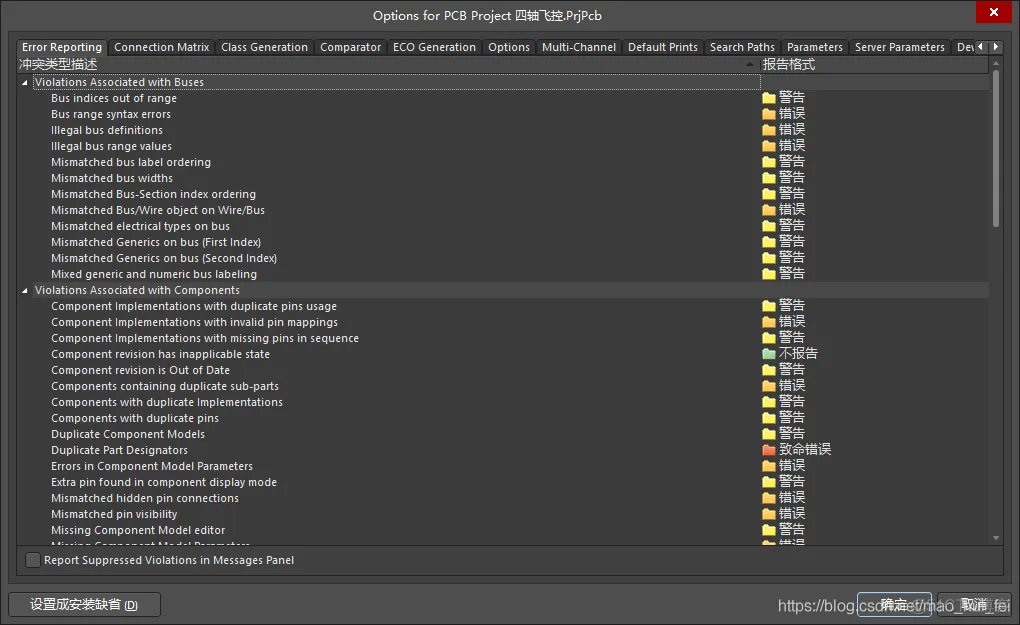

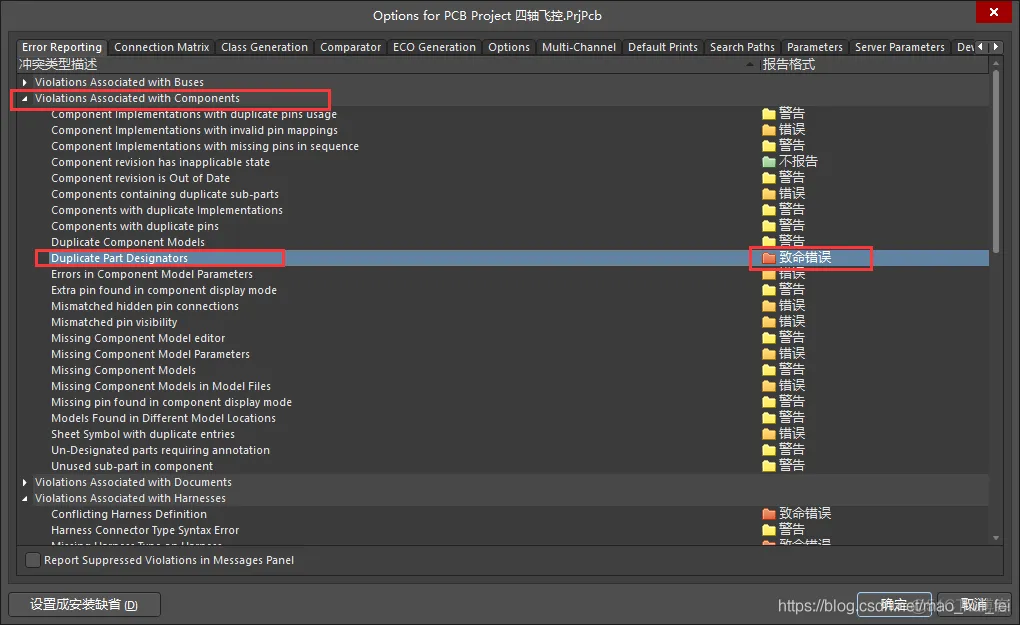

打开后的界面如下: 一、元件标识位不能相同

一、元件标识位不能相同

首先原理图中不可有元件标识位相同,在元件相关冲突栏中,将其用最高优先级错误标出(用红色错误标识)。 二、网络(net)的检查

二、网络(net)的检查

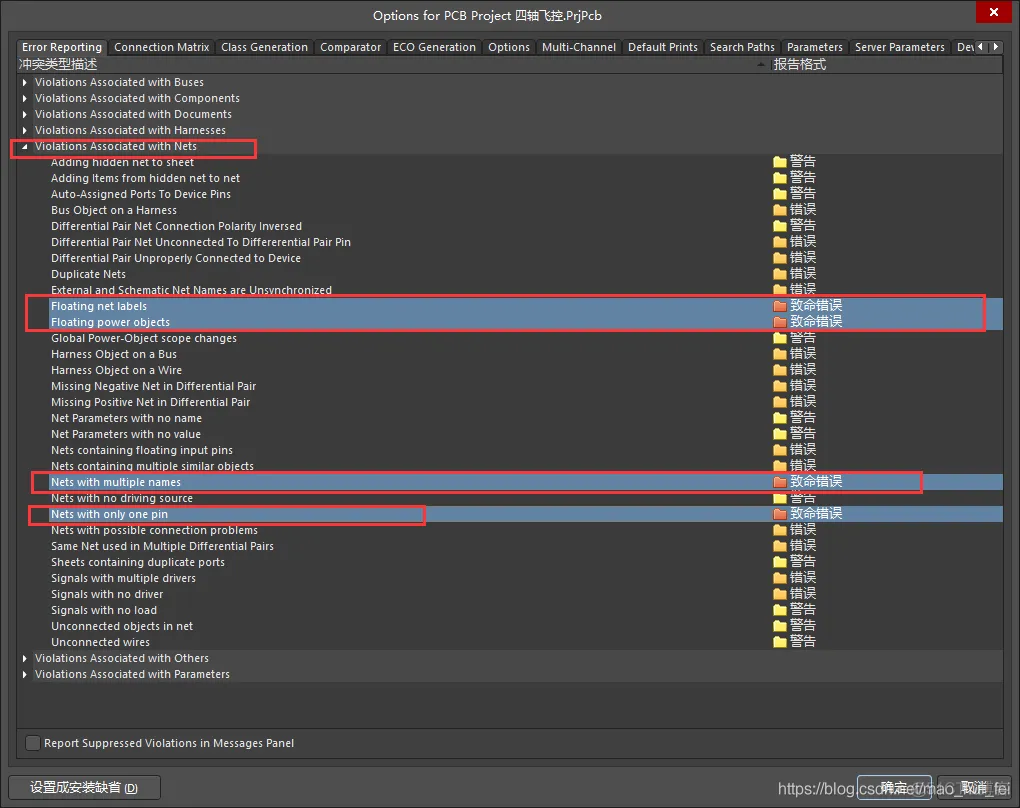

新手,甚至老手,常常会在网络上犯错,有时候两个网络标号名字大致相同,但是却没有连接上,这样导入到PCB图时,就不会有线连接。

在网络连接处,不允许有悬浮网络出现,避免因失误而未将网络放置在引线上,相对应的也将单端网络检查出来,相关设置在网络相关冲突栏中。

对于网络的重复命名和单点网络也需要注意检查

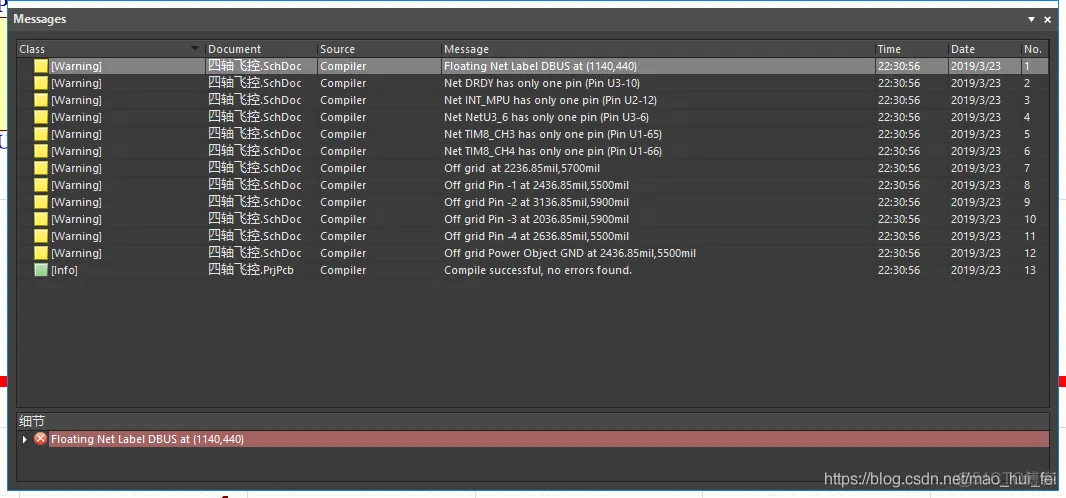

设置完成后,可以使用快捷键”C+C”进行编译(Compile + Compile),在右侧的Message窗口会显示报错内容,双击某一项报错可以跳转到原理图相对应的位置进行检查,尤其是Fatal Error请一一校对。

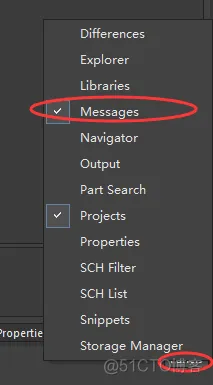

如若没有弹出这个窗口,可以在右下角Panels面板命令将Message浮动窗口调出并拖动到后侧吸附。

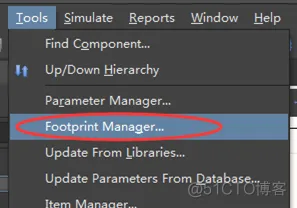

在保证原理图连接无误后,打开工具菜单栏中的封装管理器Tools-Footprint Manager进行检查,主要检查封装的完整性。尤其像芯片的SOP,SSOP,VSSOP,TSSOP这些易混淆封装,以及电阻电容的0805和0603封装是否使用正确。

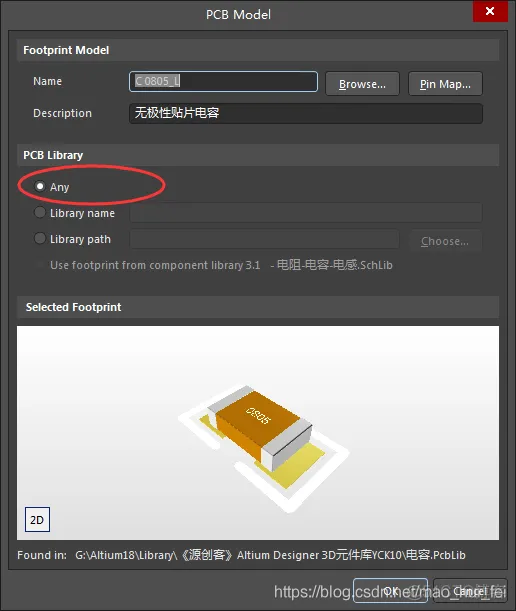

如果这个设计作品开源,在器件的封装选择时,使用的库文件应选择Any,这样他人在打开这个工程时,便不会出现封装缺失的问题。

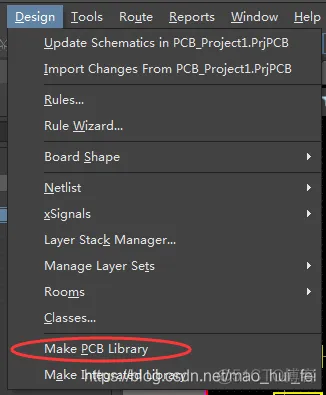

同时,在PCB绘制完成后,应将所有使用PCB库导出,快捷键D+P(Design + PCBLIB),并保存在工程目录下。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。