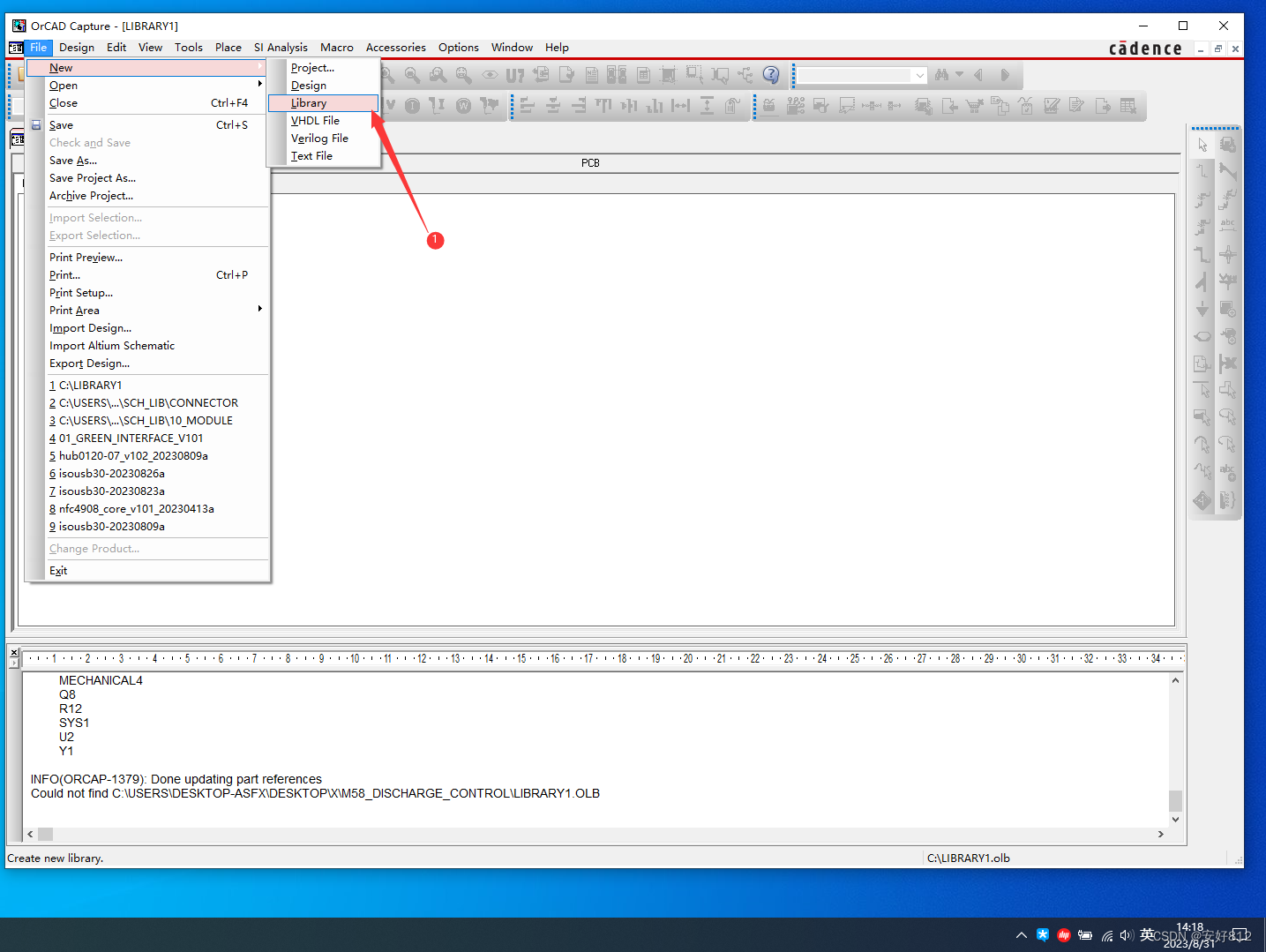

1、选择菜单 “File—New—Library ”,出现如下图所示界面。

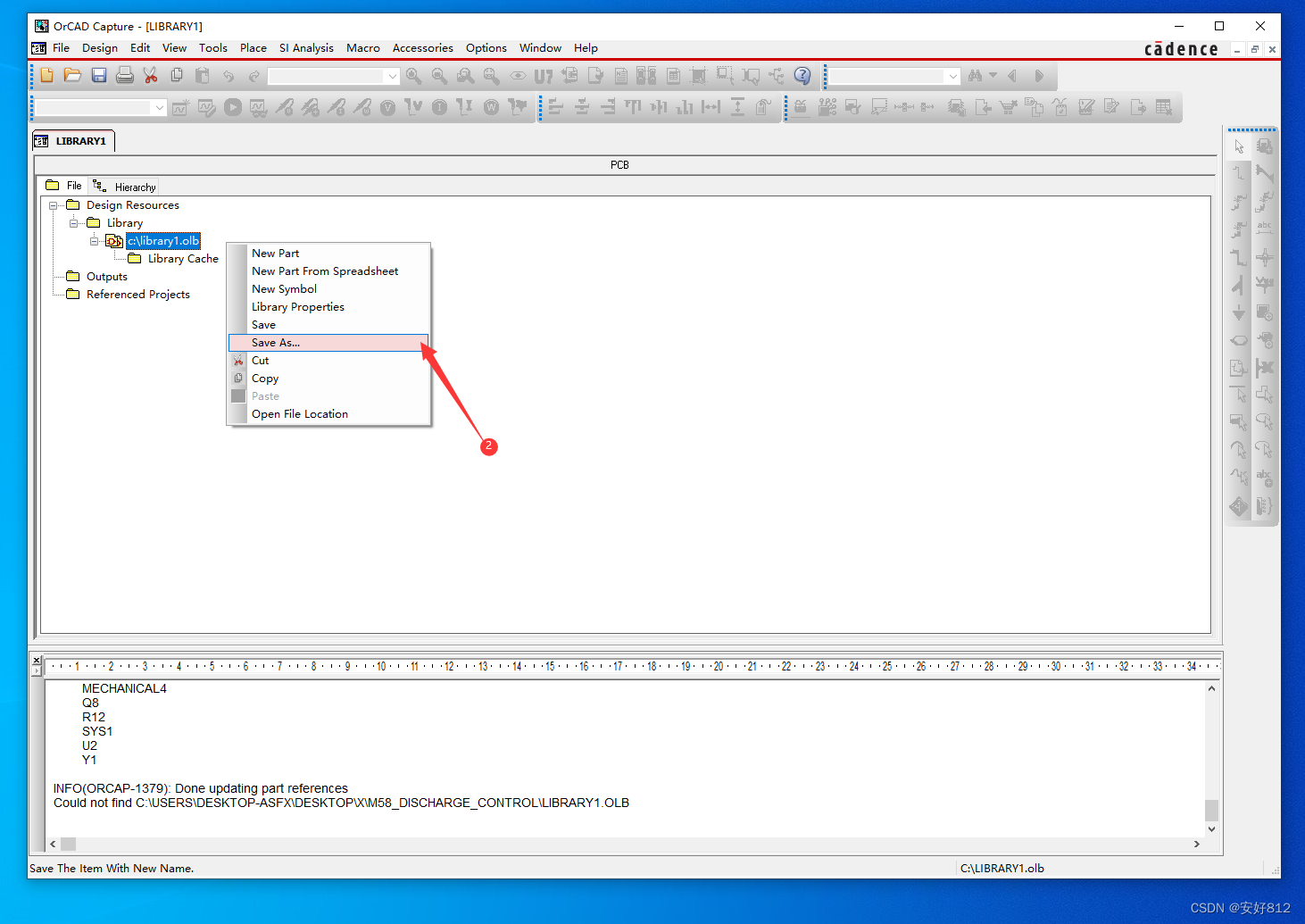

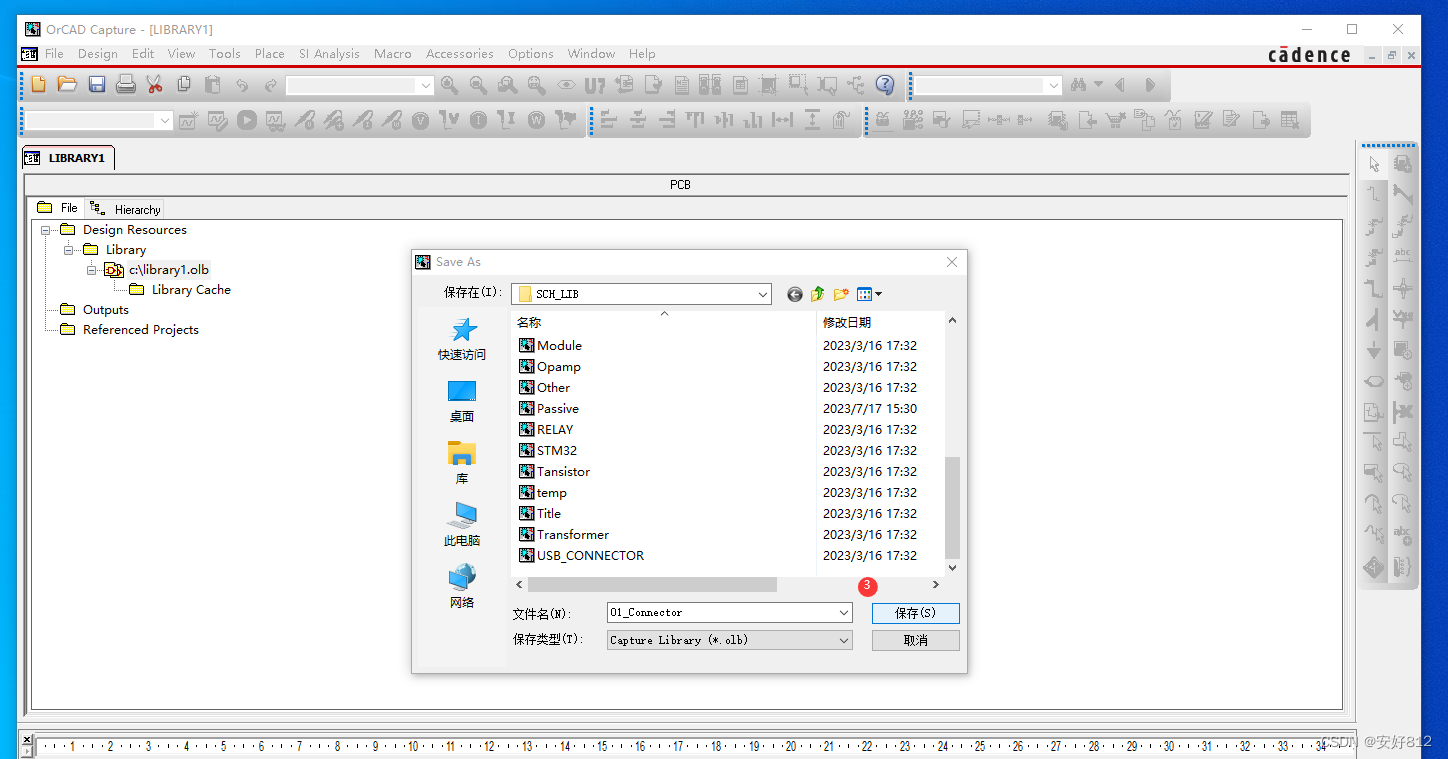

2、 将“libraryl .olb” 另存到自己的文件夹,取名为 “01_Connector”(可以取其他名,建议按照类别,方便后期使用),再来新建器件,如下图所示。

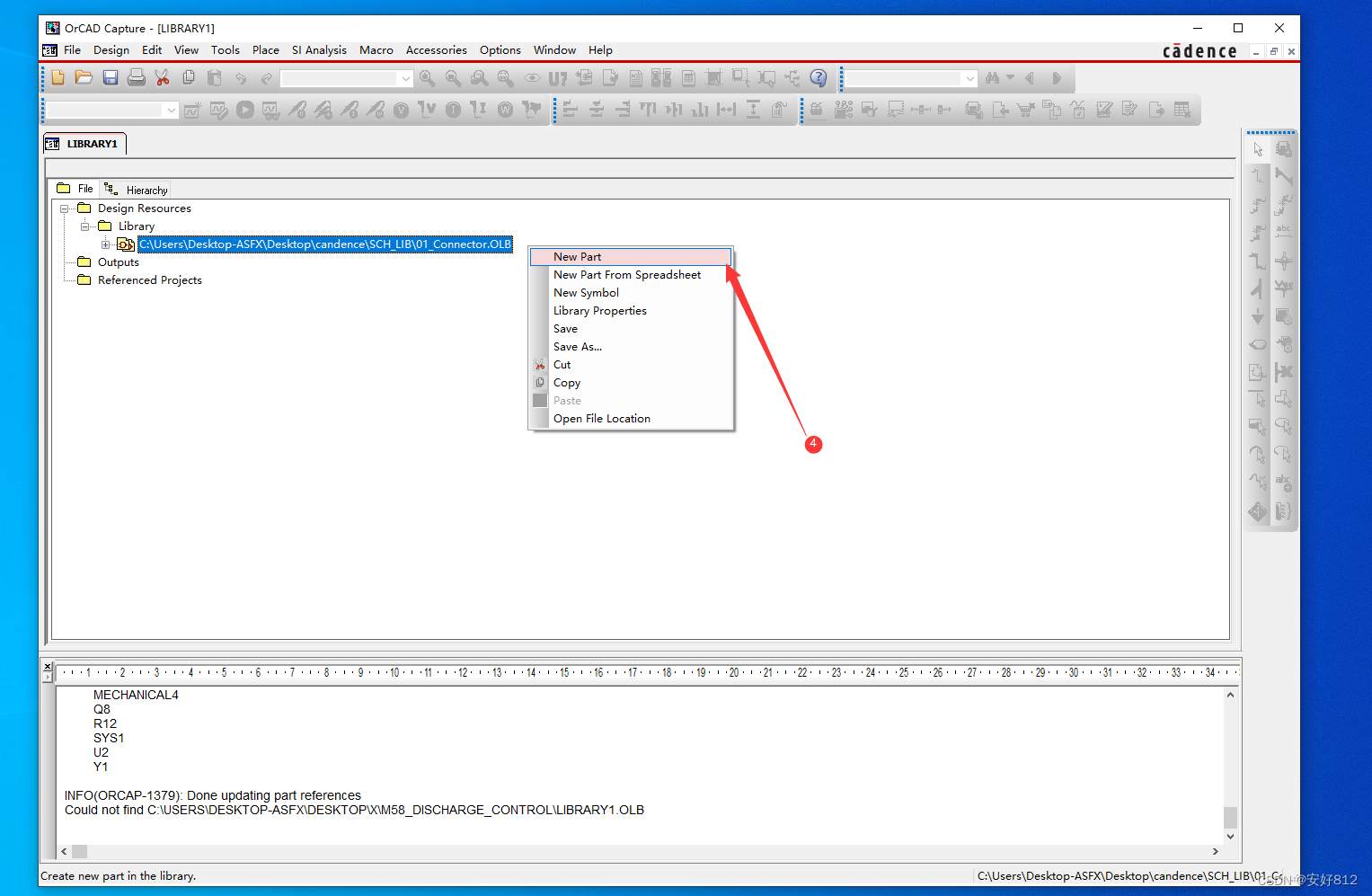

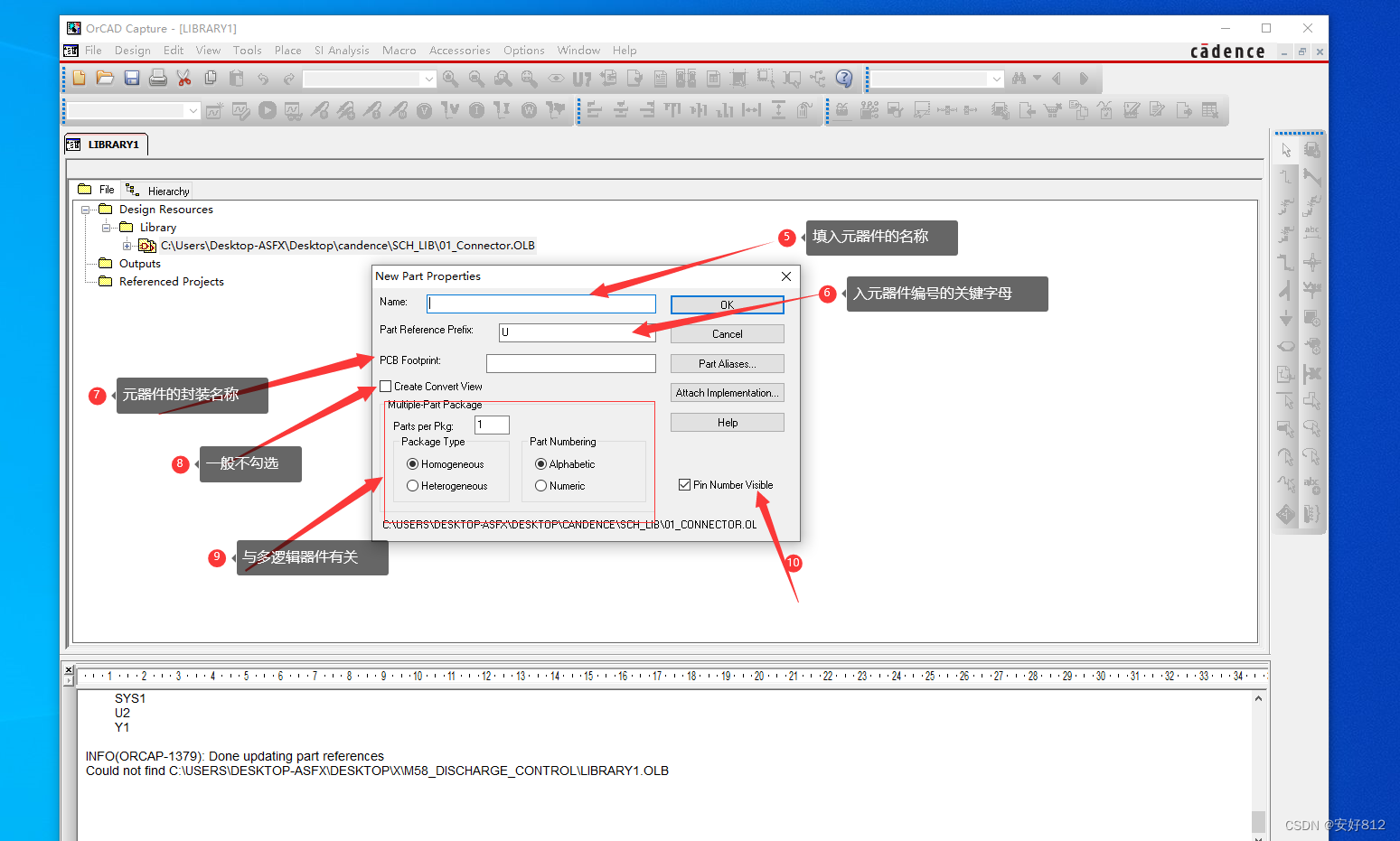

3、右击 “C:\Users\Desktop-ASFX\Desktop\candence\SCH_LIB\01_Connector.OLB”,选择 “New Part ”,如下图所示。

4、单击 “OK ” 按钮,进入绘制界面。

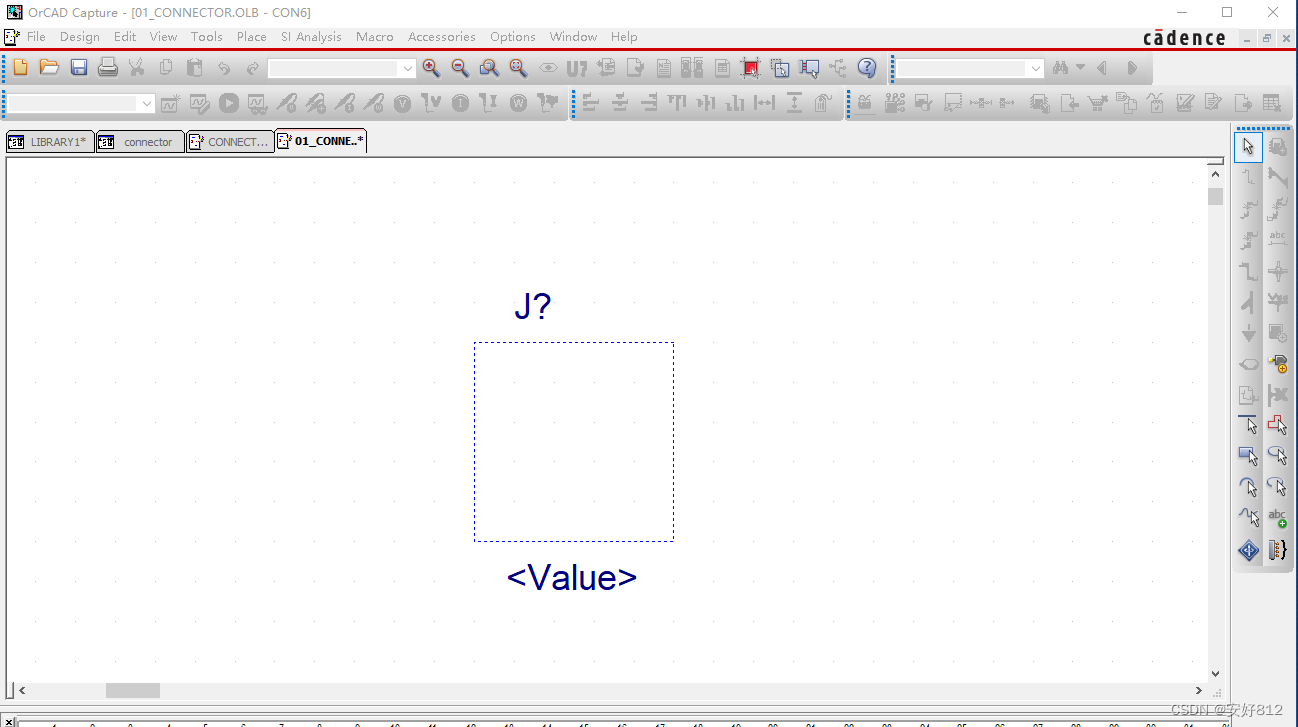

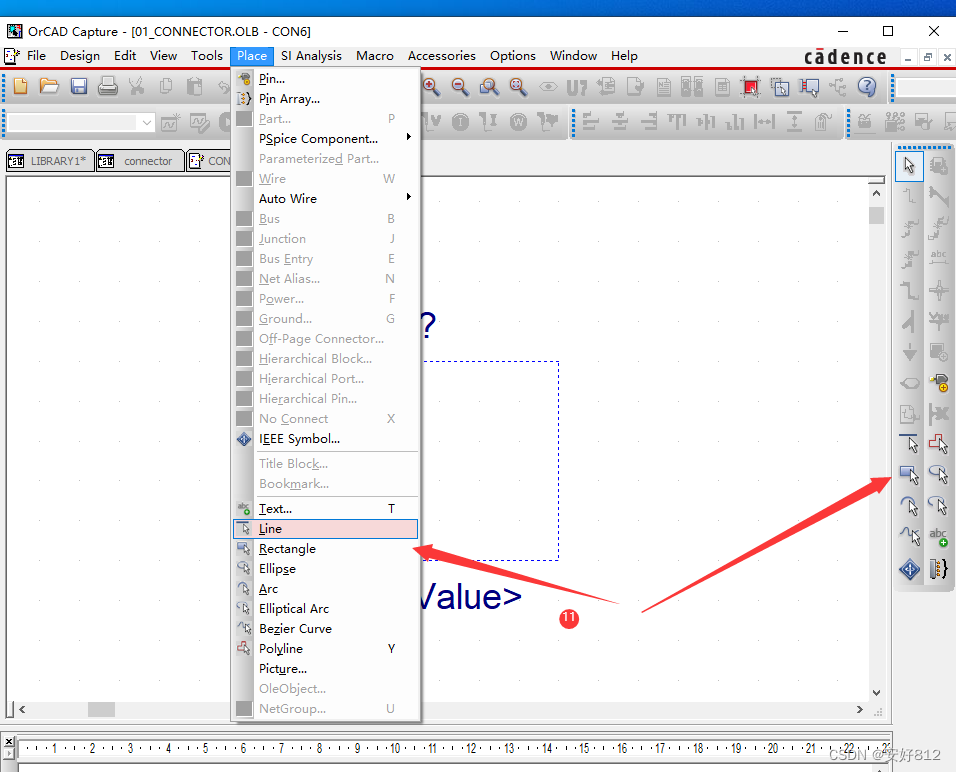

5、选择菜单栏 “ Place—Rectangle”或边框放置栏 ,如图。

画出合适大小框,然后通过右键选择 “End Mode” 结束命令。 说明:初次画好后,选中矩形框后,鼠标按住边缘,是可以调整大小的。

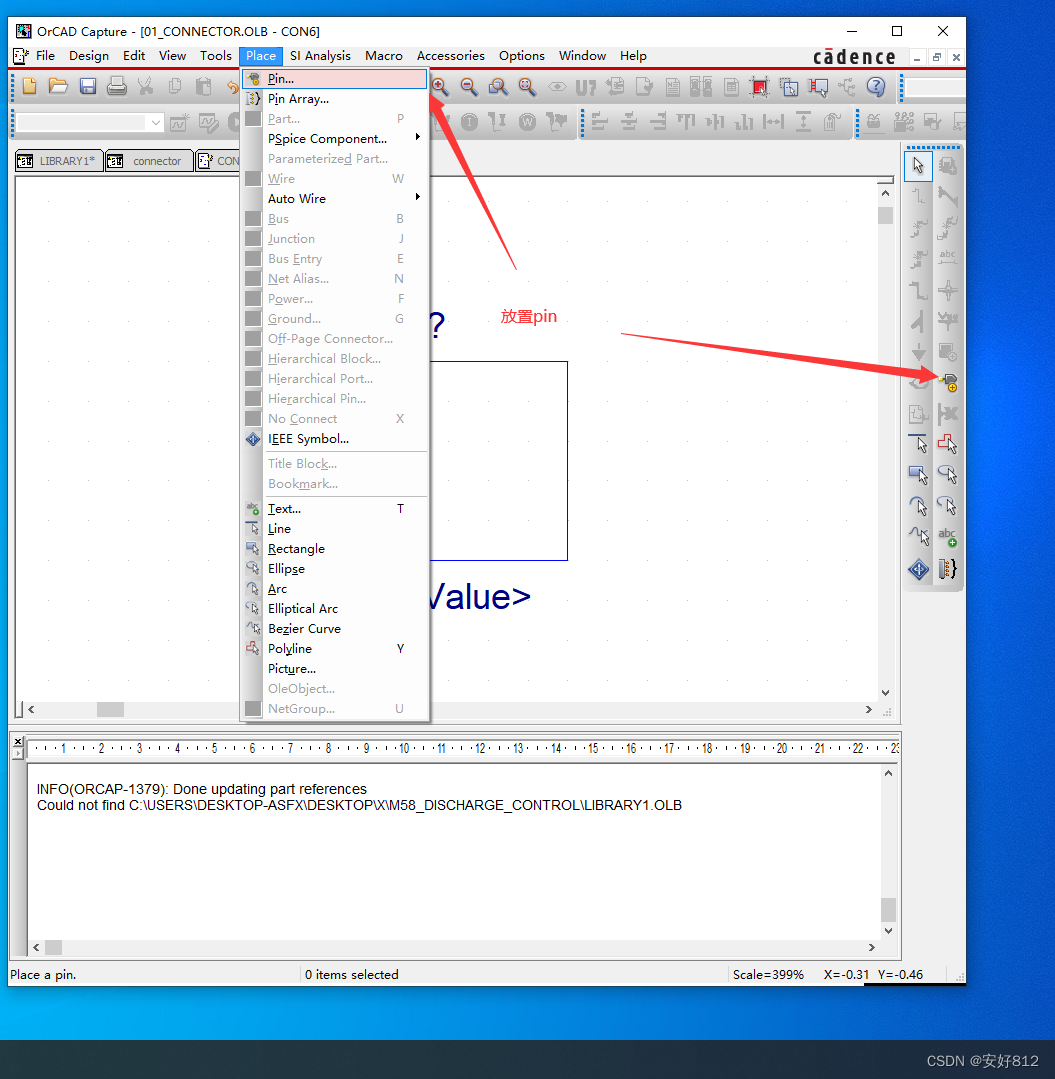

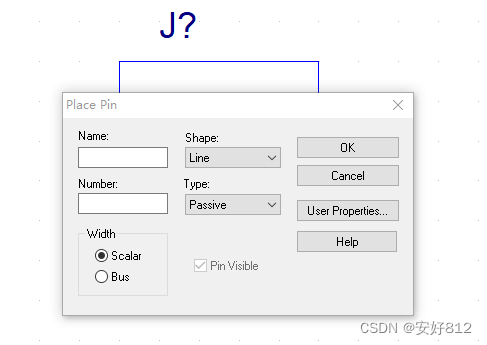

6、放置引脚,选择菜单 “Place—Pin...”, 出现的界面如图。

Name 处填上引脚名;

Number 处填上引脚号;其他保持默认即可。

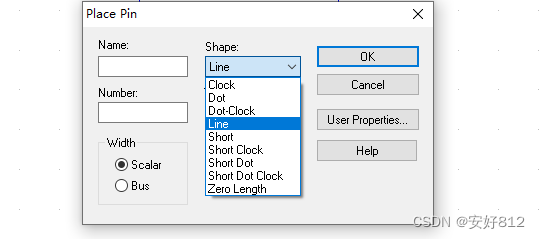

设置引脚形状:

Clock:表示该引线为 时钟 信号。

Dot:表示“非”。 Dot -Clolk:表示经“非”作用的时钟信号。

Line:一般引线;其长度为三个格点间距。

Short:表示短引线。其长度为一个格点间距。

Short Clock:为短引线的时钟信号。

Short Dot:为短引线的“非”。

Short Dot Clock:为短引线的“非”形式时钟信号。

Zero Length:表示长度为零的引线。一般用于表示“电源”和“地”引线。

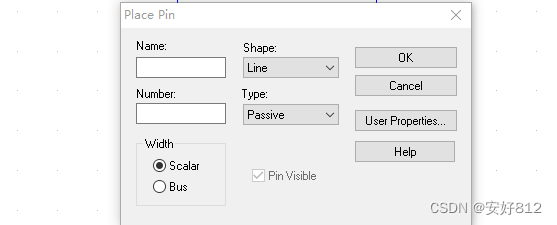

3 State:三态引线。该引线可能为低电平、高电平和高阻三种状态。

Bidirectional:双向信号引线,既可以起输入作用也可以起输出作用。

Input:输入端引线。

Open Collector:集电极开路输出端引线。

Open Emitter:发射极开路输出端引线。

Output:输出端引线。

Passive:无源器件的引线。

Power:电源引线和地引线。

Width:指定该引线信号是一般信号 “ Scalar ” 还是总线信号 “Bus”。

7、设置好后,单击 “OK ” 按钮,在页面上放置即可。

8、 选择菜单 “File—Save ” 进行保存完成此单逻辑元器件制作。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删