有两个工具支持:Allegro Design Entry HDL (concept)和OrCad capture CIS。似乎业界多用OrCad capture CIS。 以前的项目用过concept。

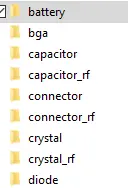

如果使用concept,元器件库需要做以下几点:

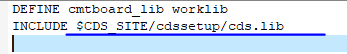

当使用Concept做一个新的design的时候,会在项目folder下生成一个cds.lib,该文件内容指向library setup

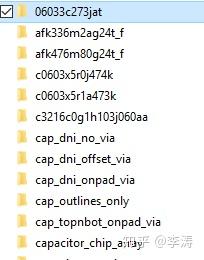

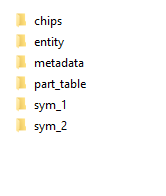

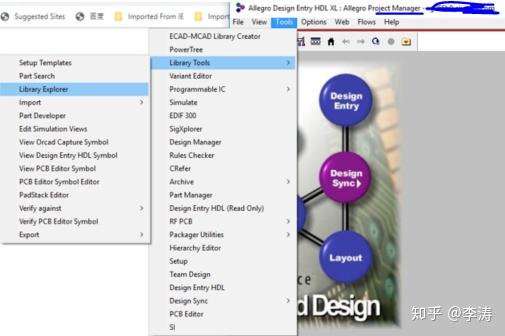

使用Library Explorer创建一个新的项目,然后修改cds.lib加载所有需要转换的concept库单元。

重新打开项目后会看到所有的库单元,右键选择“Part Developer“打开一个新的”Part developer“的工具。

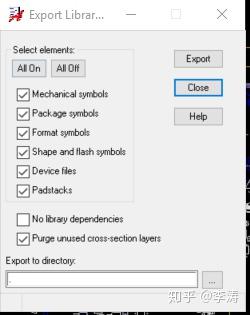

选择file->Import and Export找到”Export Capture Parts"

用OrCad capture打开该dsn文件,design cache会有一些库单元。将这些库单元选中右键“copy”。然后在“Library”加载自己的元件库,右键“paste”就可以得到这些库单元

如果文件没有lock,可以简单 File->Export->Library就可以了

6.0 mm +/- 0.25mm --> 40 layers boards?

For a width of 0.25mm with thickness of copper of 35µm , the current is 0.700 mA

For 0.3mm -> 0.9 mA

For 0.5mm -> 1.5 A

For 0.7mm -> 1.9 A

需要理解材料如何选择,层厚,线宽....etc

需要和PCB板卡商确定材料类型(conductor和dielectric),厚度,介电参数...etc. 线宽需要根据叠层设计和PCB板卡商确认(50 ohm,100 ohm, 45 ohm...ect)

setup -> Cross-section可以看层结构。View->show Drill chart 可以看过孔。如果看到盲埋孔,需要看 setup-> BB Via definition -> define BB via 知道这些盲埋空如何定义的。

Tools-> Reports可以产生各种report,需要看看哪些report是有用的可以加到checklist中去

约束定义好了并且走线之后,我们需要使用约束管理器去检查所有约束是否满足。步骤如下:

- 打开Allegro Constraint Manager (Setup -> Constrains->Constrains manager)

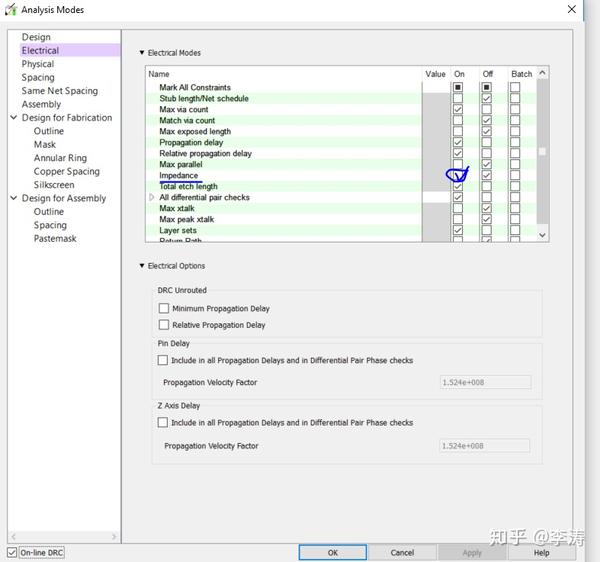

-打开Analyze-> Analyze Modes确保关心的参数被选取了(比如下图的impedance)

-回到constraint的主页面,在关心的参数点击analyze可以看结果

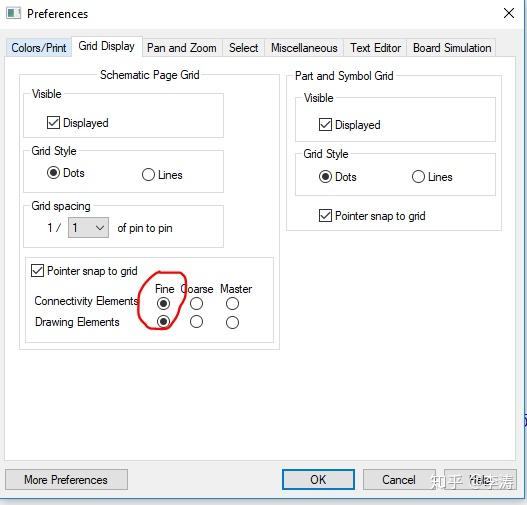

Options->Preferences可以配置连线的grid粗细,避免连线跳格太大

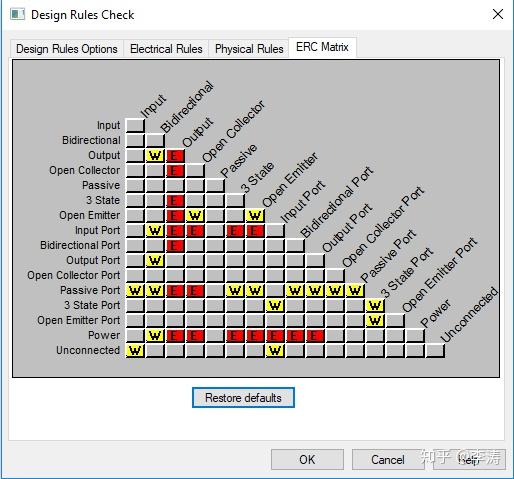

ATE板子一般会将多种资源连接到一个net上,因此DRC的check会报很多error和warning。尝试修改ERC matrix但是没见到效果

但是可以将DRC的warning放到waiver中,DRC的error无法放入waiver。

1) 封装设计相关资料

一般标贴器件的焊盘尺寸可以参见ipc的标准,有一个工具“pcb matrix ipc lpc viewer”可以下载参考如何定义标准标贴封装的焊盘大小;

做tester channel card,DPS card的封装的时候最好是在Pin1的中心画一个十字星,目的是在放入PCB的时候方便和footprint对齐坐标;

制作有via的焊盘时,需要考虑散热焊盘和antipad设计,在于争视频第25讲和以下文章可以看到具体内容

2) 层叠的设计

层叠的层数是由板子复杂度决定的。但是走线层的铺铜厚度(1 oz,0.5oz),介质层厚度及DK参数,阻抗控制需要线宽等需要事先和PCB厂商询问。

因此一般在约束管理器我们只约束线宽而不约束阻抗,原因就是因为在层叠中设置的一些影响阻抗的值比一定是打板的最终数据,allegro计算的阻抗不是实际板子值。所以我们只约束线宽,然后要求PCB厂商微调介质层厚度及DK参数保证阻抗。

3) 过孔的设计

在层叠设计之后要简单规划过孔的类型,然后在setup-> BB Via definition -> define BB via 中添加。

层叠的层数是由板子复杂度决定的。但是走线层的铺铜厚度(1 oz,0.5oz),介质层厚度及DK参数,阻抗控制需要线宽等需要事先和PCB厂商询问。

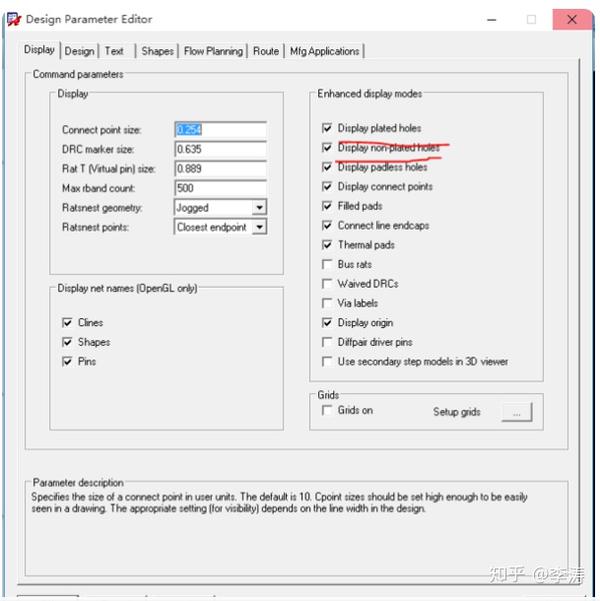

route时候如果增加VIA看不到drill hole,需要查看这些设置:

Display->color/visibility检查都有哪些设置

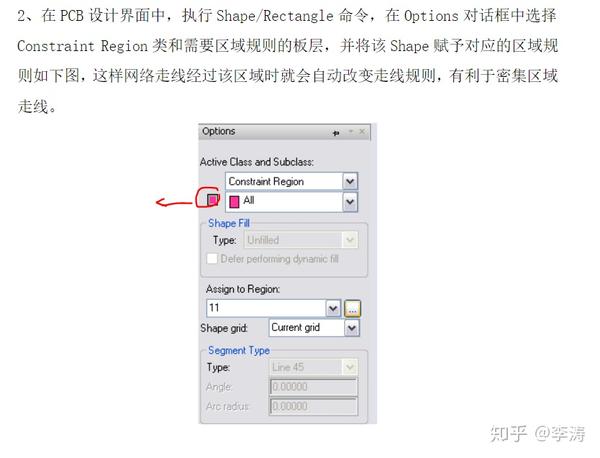

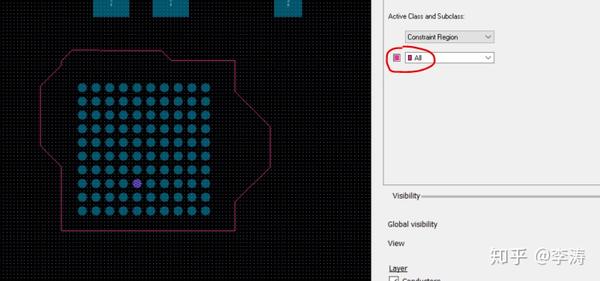

4) region的定义和约束施加

一般DUT的BGA array附近的走线需要不同的线宽,线距约束。因此需要定义这个特殊region,然后在约束管理器中对这个region定义参数。 Region可以用下面步骤定义,注意选择颜色保证绘制以后可见。

做tester channel card,DPS card的封装的时候最好是在Pin1的中心画一个十字星,目的是在放入PCB的时候方便和footprint对齐坐标。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...