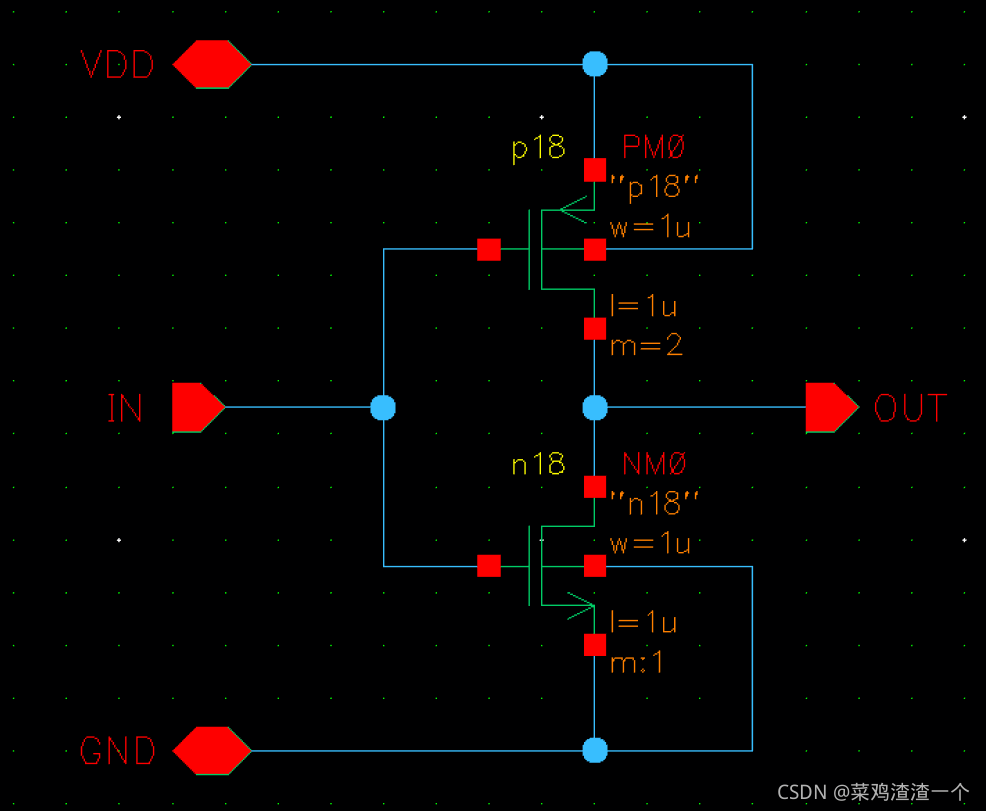

本文主要记录了如何用Cadence Virtuoso IC617建立器件和生成版图。虽然前面的文章记录过如何生成器件,但是本文将重新记录,方便查看和学习。本文将用以下原理图,这是一个反相器。

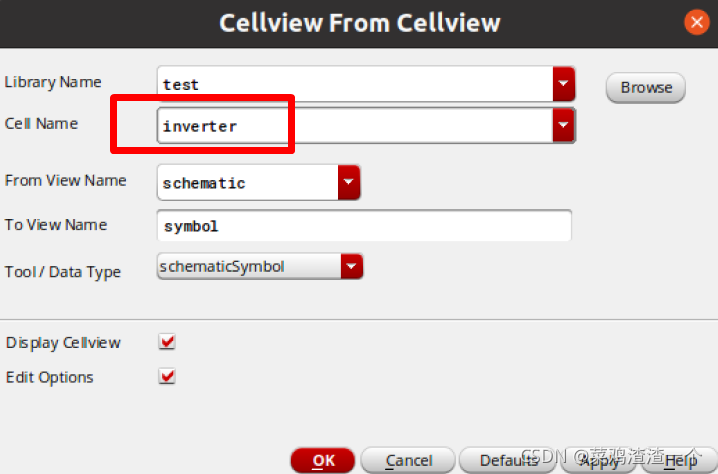

确保原理图中的器件都是有版图的,没有包含各种信号源,同时接口都放置了Pin脚。选择Create -> Cellview -> From Cellview。

名字默认为原理图的名字。点击OK到下一步。

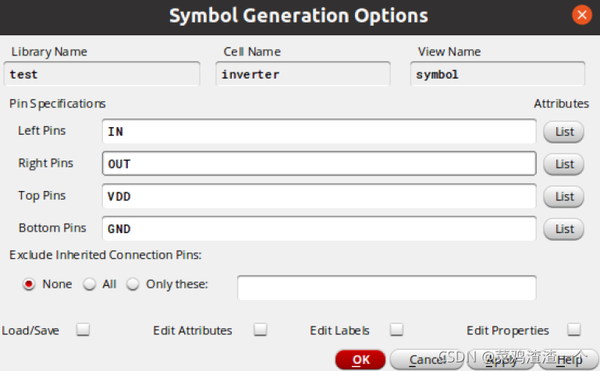

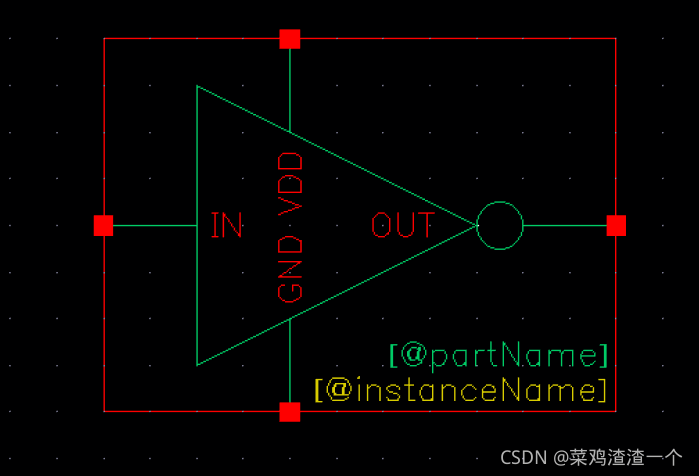

修改一下默认生成的Pin的位置。左边是IN,右边是OUT,上面是VDD,下面是GND。点击OK到下一步。

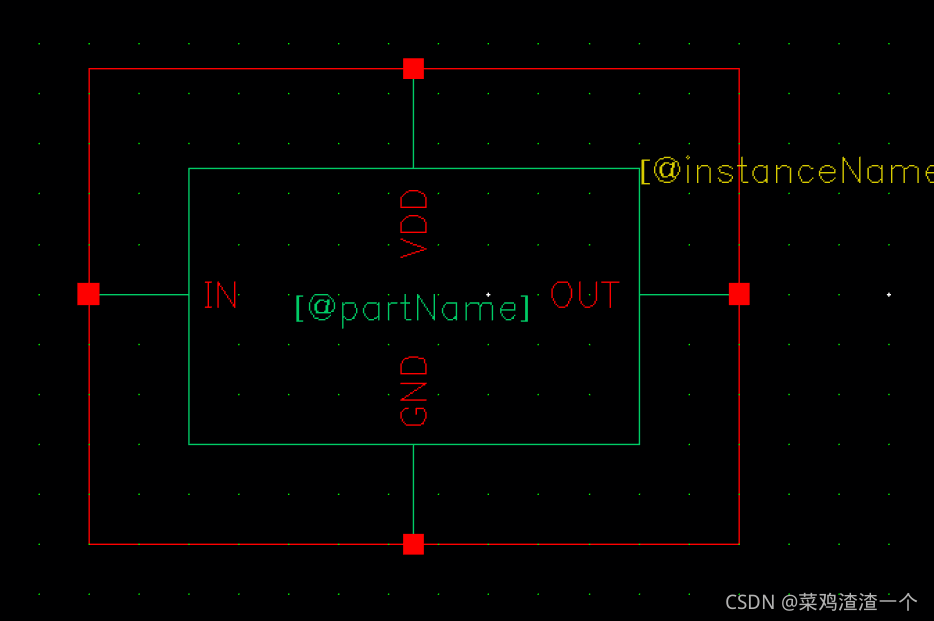

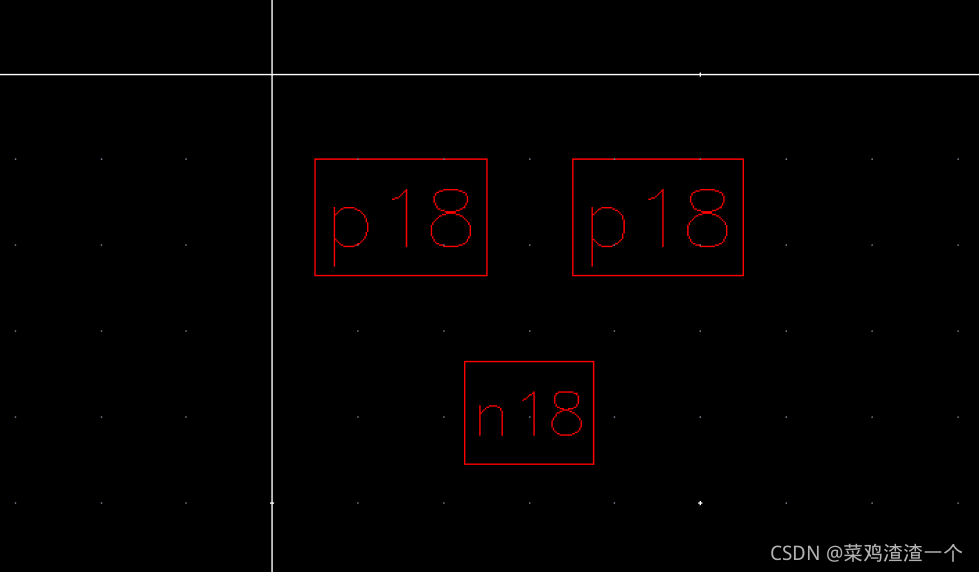

默认生成的器件。记得先保存一下这个器件的原理图和之前的原理图。

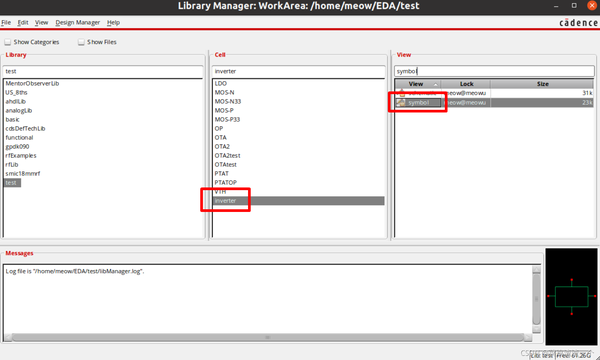

保存之后确认一下Library里有没有生成对应的symbol。

修改一下器件,这样就比较好看了。

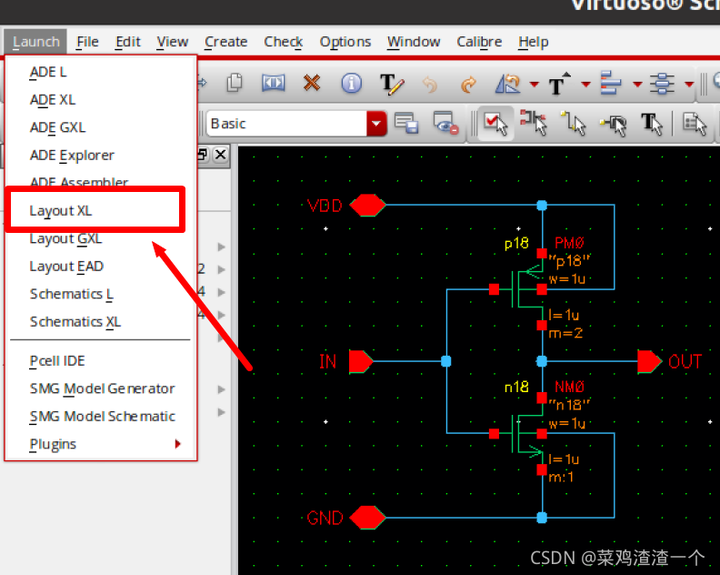

在原理图界面下,选择Layout XL

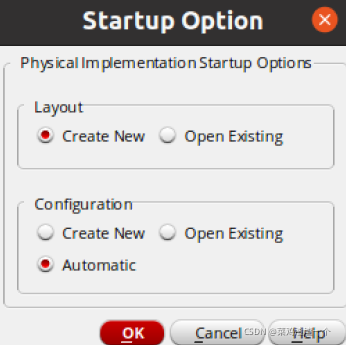

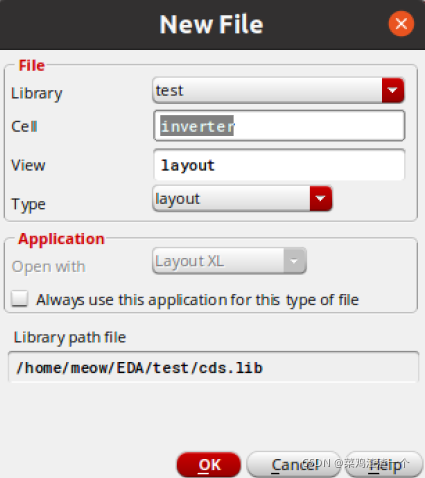

默认是创建新的Layout,默认即可。

名字默认即可。

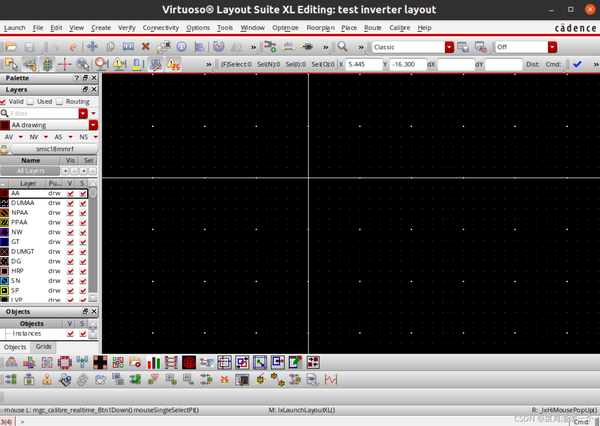

到了版图界面。

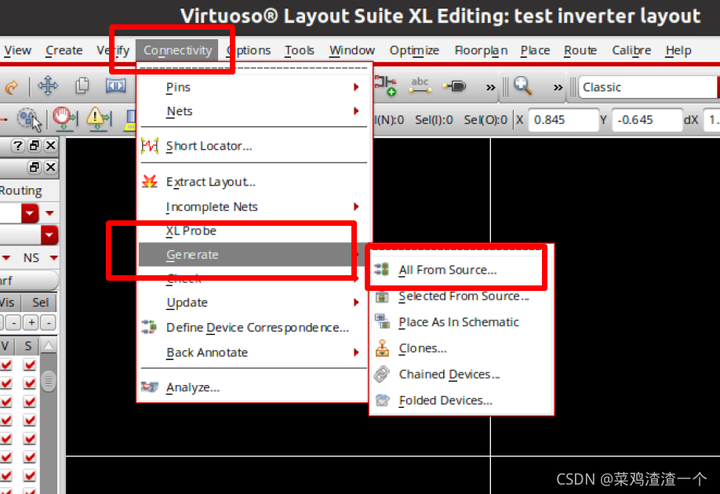

点击Connectivity -> Generate -> All from source,将每个元件的版图导入进来。

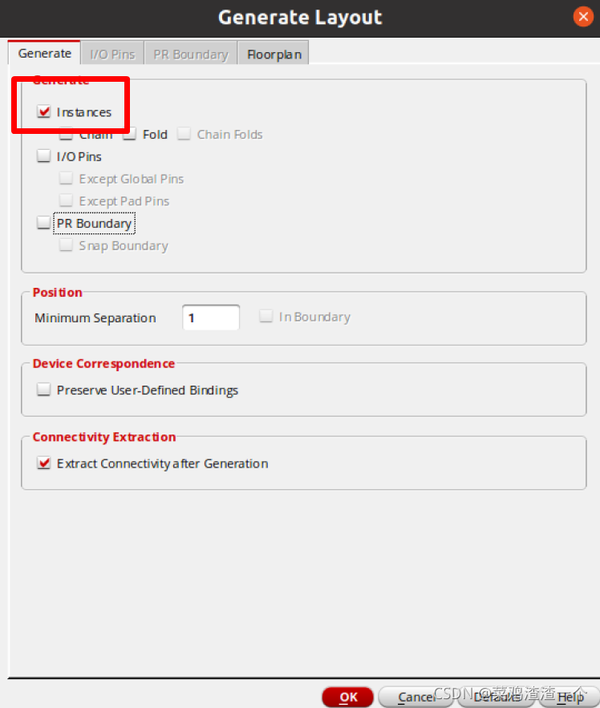

只导入器件,不导入其他的。

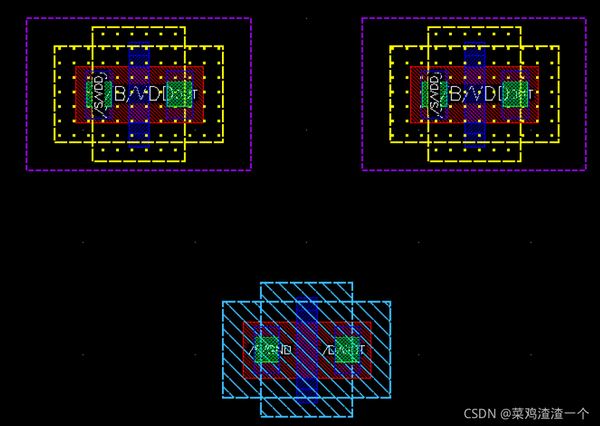

器件被导入,但是没有被显示出来。

快捷键Shift+F,就显示了。

布局需要尽量紧凑,但是也要考虑两个器件之间的影响。一般的工艺支持6到8层的金属层,是用于布线的,从最底层到最顶层,支持的最小线宽和最小过孔依次增大。

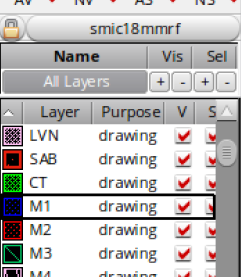

连线时,先选择对应的层,带drawing标识的才能画线 ,此处选择金属1层。

按P添加走线,按O添加过孔,按R绘制矩形,基本就是这三个操作。在画图的时候还要结合测量工具(快捷键K),来保证满足最小间距的要求。

最后,在金属字符层上,添加Label,也就是引脚,一定要和原理图中的对应。

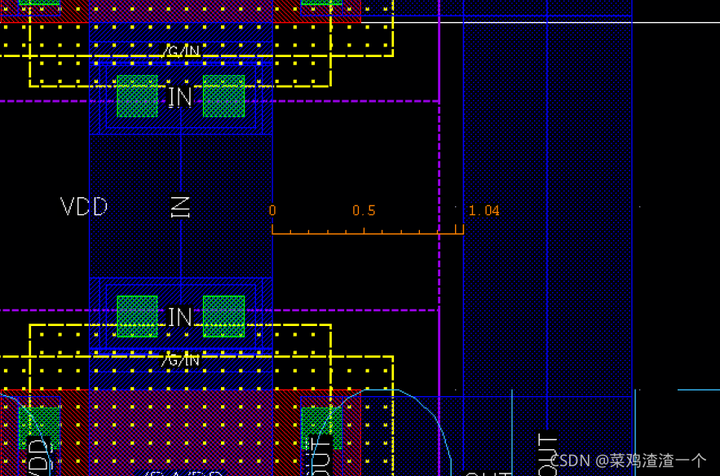

画好的版图如下图。

DRC检测是检测版图的器件间距和布线等,能否符合工艺的要求。

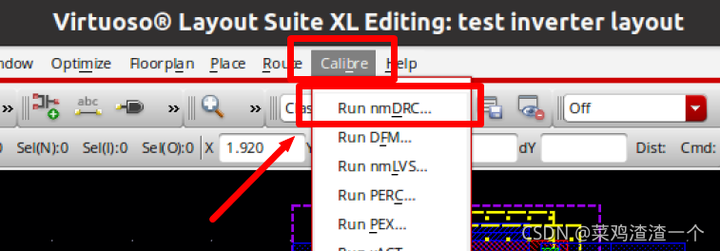

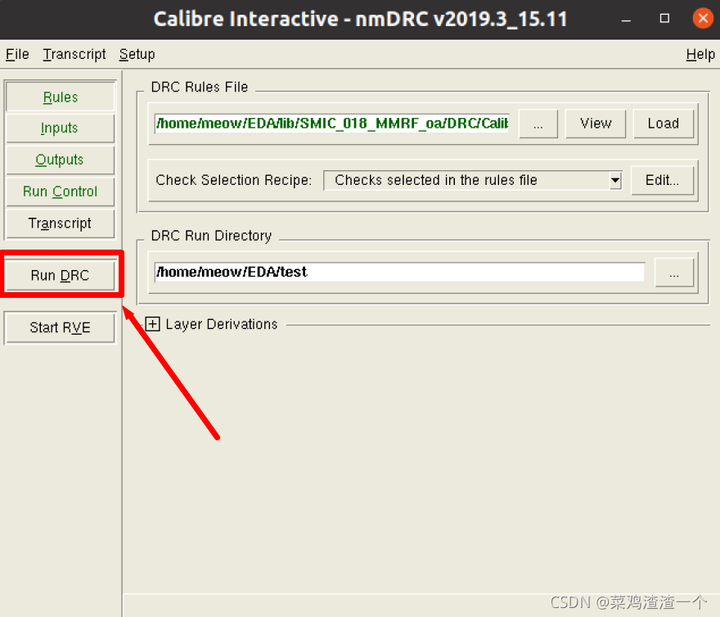

选择Calibre -> Run nmDRC。

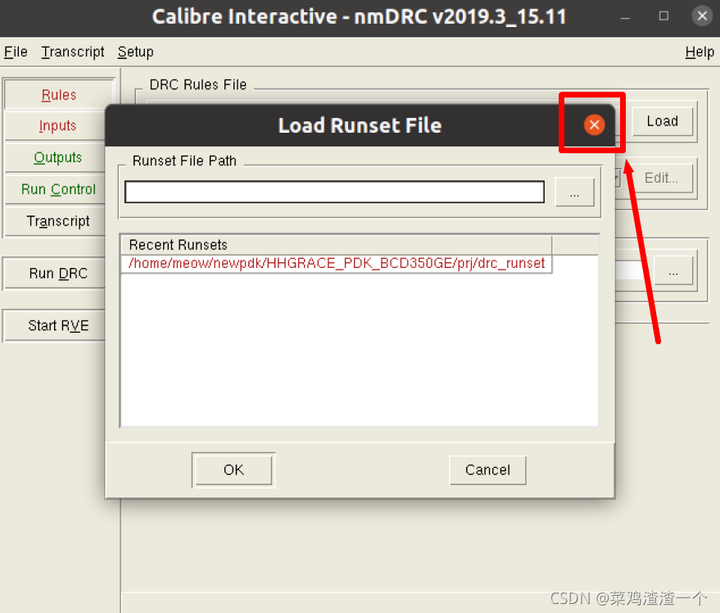

叉掉第一个窗口。

注意,如果在这一步出现License的错误,如下图

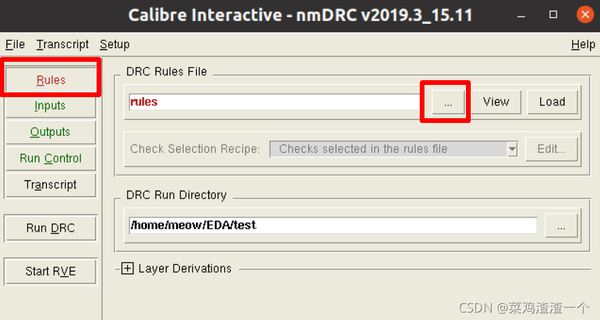

稍等一会,等除了Rules之外全部变绿后,点击Rules,然后点击三个点,加载DRC规则。

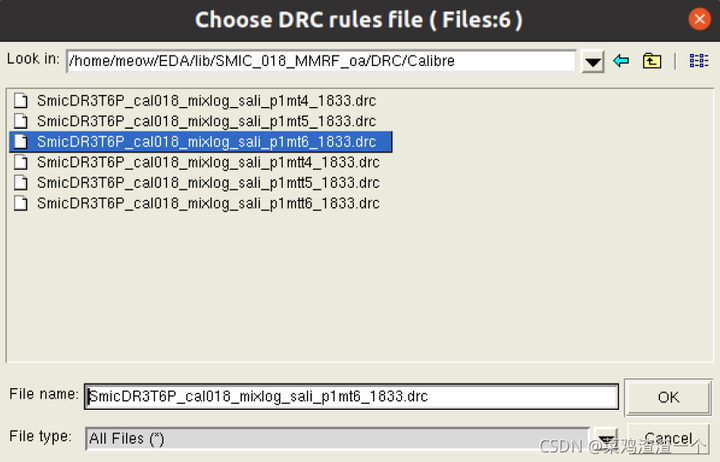

在存放工艺库文件的文件夹中,有DRC规则文件,加载进来。

点击运行。

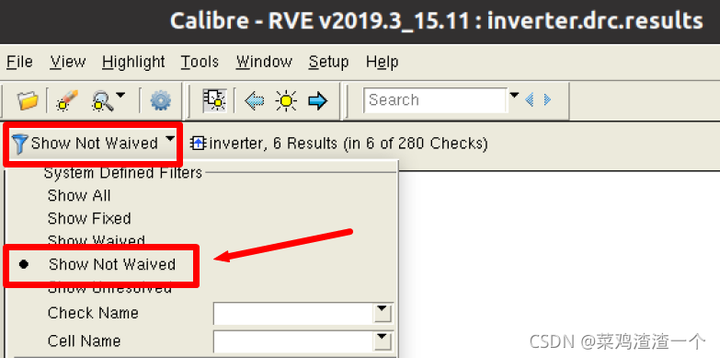

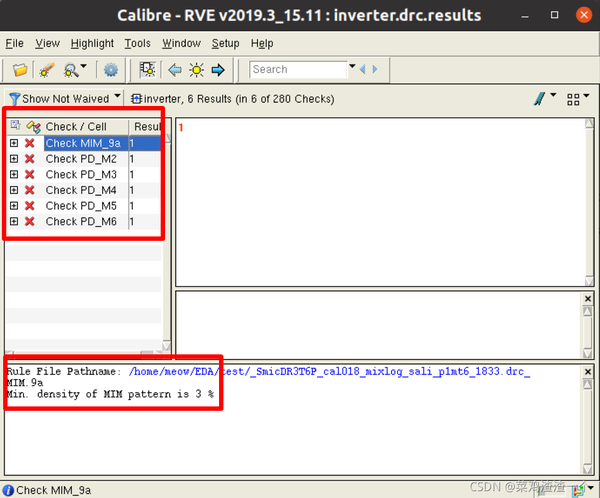

在弹出的结果框中,可以筛选信息类型。

就能看到版图存在的错误。将错误全部修改完就完成了DRC检测。(下图的错误主要是电路密度错误,也是就弄得太稀疏了,忽略即可)

LVS检测是针对电气连接的检测,能查看版图的连线是否和原理图连线完全一致。

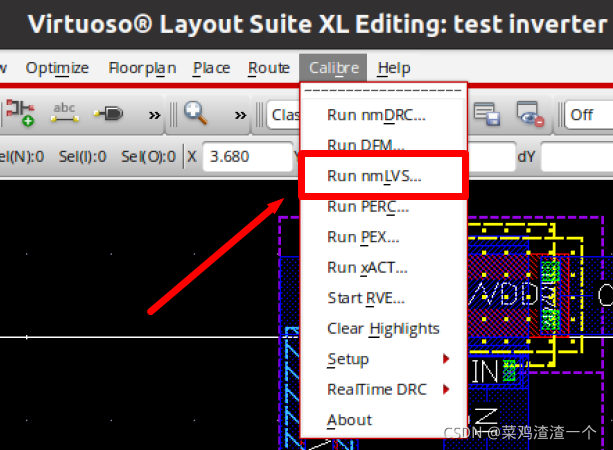

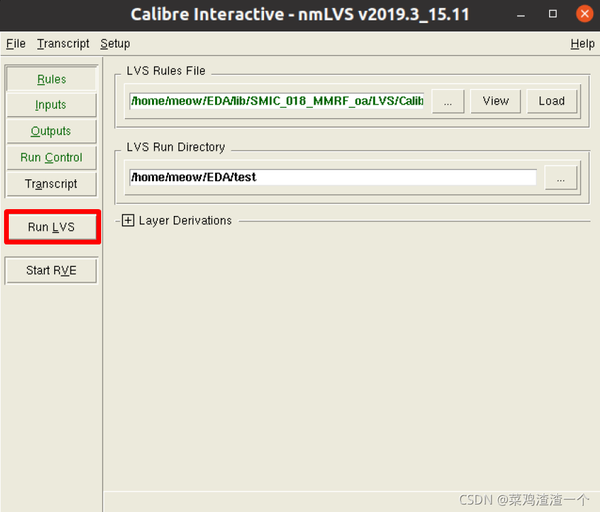

选择Calibre -> Run nmLVS。

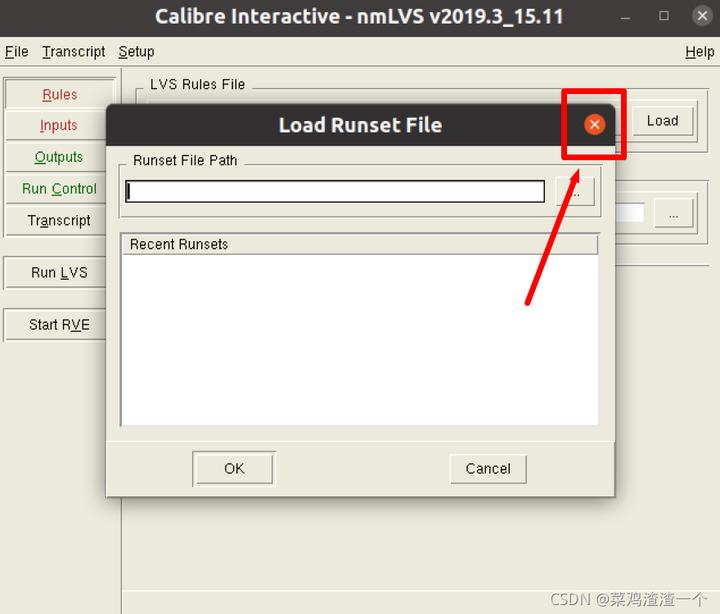

叉掉第一个窗口。

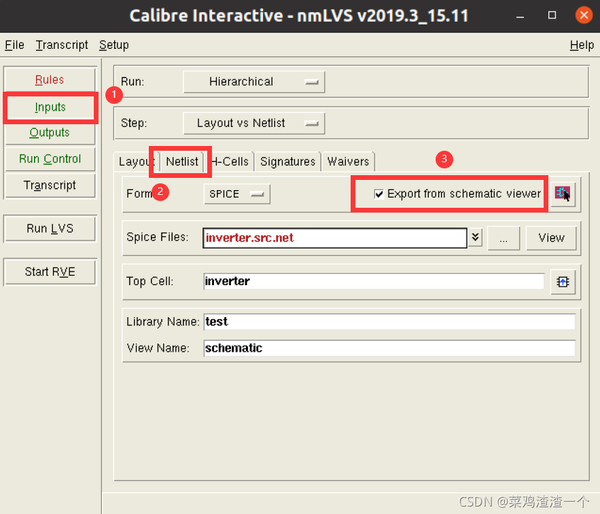

选择Inputs,在Netlist里,把对应的勾选上。

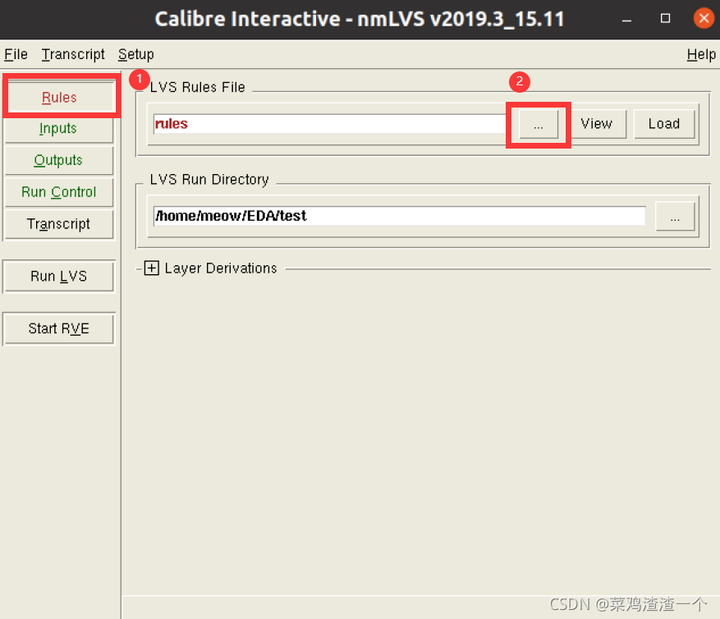

点击Rules,然后点击三个点,加载LVS规则。

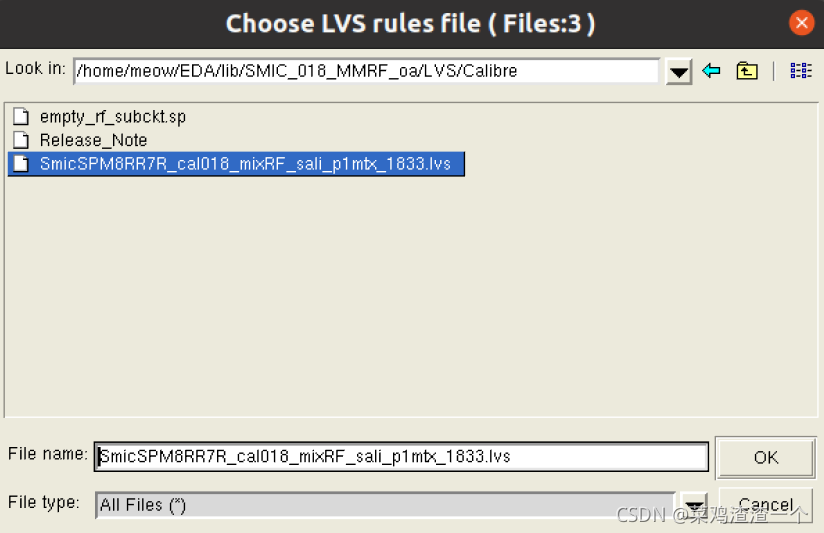

在存放工艺库文件的文件夹中,有LVS规则文件,加载进来。

点击运行。

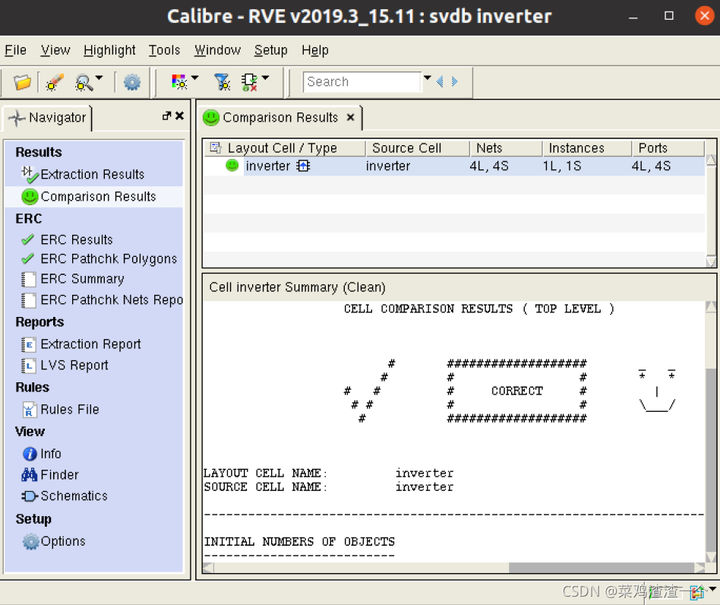

在弹出的结果窗口中,看到笑脸,就意味着通过了检测。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...