ChipScope Pro调试设计

在传统的FPGA设计中,调试时大都采用示波器和逻辑分析仪。FPGA和PCB设计人员保留一定数量FPGA引脚作为测试引脚,FPGA设计者在编写FPGA代码时,将需要观察的FPGA内部信号定义为模块的输出,在综合实现时再把这些信号锁定到保留的测试引脚上,最后连接示波器或逻辑分析仪的探头到这些测试脚进行观测。这个测试方法存在很多局限性,成本高、灵活性差、操作麻烦。

成本高。示波器、逻辑分析仪的成本较高。灵活性差。要测试FPGA的内部节点,需要修改设计,将待测信号引到FPGA引脚上来进行测试。PCB设计完成后这些用作测试引脚的位臵和数量就固定了,不能灵活改变。如果测试引脚不够用时,影响测试。如果测试引脚太多,又将影响PCB布局和布线。而且在一些极端设计中,FPGA的I/O引脚可能已经用光,根本没有多余的引脚被用来做测试引脚。操作麻烦。示波器、逻辑分析仪必须通过探头连接到测试引脚,容易造成短路,损坏器件。

随着FPGA的规模不断增大,FPGA的设计变得越来越复杂,其封装形式大多向球形方式转移,传统的使用探针监测信号的方式变得越来越困难。Xilinx推出的集成化逻辑分析工具ChipScope Pro,完全解决了这些问题。

ChipScope Pro具有传统逻辑分析仪的功能,价格便宜,而且不需要附加大量探头,具有很高的实用价值。它是针对Xilinx Virtex系列和Spartan系列器件设计的片内逻辑分析工具,它通过JTAG口,将FPGA内部信号实时读出,传入计算机进行分析。基本方法是利用FPGA内的BRAM,存储信号波形数据,然后通过JTAG接口将数据传送到计算机,并将波形在计算机显示出来。ChipScope测试系统连接结构图如图9-1所示。

使用这种技术观察FPGA内部信号的测试方法,具有以下优点。

成本较低。仅需要ChipScope Pro 设计软件和一根下载电缆,极大地简化了PCB的设计成本。较高的灵活性。不需将待观察的信号通过额外的引脚输出到FPGA,信号的数量和存储深度由器件BRAM决定。器件中BRAM越多,可观察的信号数量和存储深度就越大。使用方便。ChipScope Pro在 ISE工具中作为一个IP模块来调用,可以方便地选择待测信号,也可以设臵复杂的触发条件。

图9-1 ChipScope 测试系统连接结构图

ChipScope Pro由一系列相关的IP 核及其软件工具组成,包括核生成器(Core Generator)、核插入器(Core Inserter)、分析仪(ChipScope Analyzer)和TCL 脚本控制接口。

1) 核生成器

Xilinx Core Generator Tool(Xilinx 核生成器):通过它可以生成

集成控制器核(ICON)、

集成逻辑分析核(ILA)、

虚拟I/O 核(VIO)及

安捷伦跟踪核(ATC2)的网表和实例化所需的模板文件。IBERT Core Generator(IBERT 核生成器):通过它生成Virtex-4 和Virtex-5 系列的误比特率测试核(IBERT)的网表和实例化所需的模板文件。

2) 核插入器

Core Inserter(核插入器):自动将CON、ILA 和ATC2 核插入已经综合完成的设计中。PlanAhead Design Analysis Tool(PlanAhead 设计分析工具):自动将ICON 和ILA 核插入设计网表中。请参考PlanAhead 章节内容。

3) ChipScope Analyzer(ChipScope 分析软件)

通过它可以配置FPGA,可以设定触发条件,可以设定ILA、IBA/OPB、IBA/PLB、VIO 及IBERT 的踪迹显示方式。

4) ChipScope Engine Tcl (CSE/Tcl) Scripting Interface(TCL 脚本控制接口)

通过TCL 脚本语言和JTAG 链,完成与芯片的通信交互。在设计中,使用ChipScope Pro 有两种操作流程,如图9-2 所示。

图9-2 ChipScope 操作流程图

流程1:通过ChipScope Pro 内核生成器,产生各种不同功能调试内核,如ICON、ILA和IBA 等,将生成的例化代码插入HDL 源程序中,再对包括ChipScope Pro 内核的设计进行综合实现后下载到器件中,利用ChipScope Analyzer 进行分析。

流程2:利用ChipScope Pro 的内核插入器将所需要的内核直接插入到已经综合完成的设计网表(NGC 或EDIF)中,然后对这个新的网表文件布局布线后下载到器件中,利用ChipScope Analyzer 进行分析。

接下来我们详细介绍ChipScope 的IP 核及其应用,重点介绍如下内容。

ChipScope Pro 核生成器及各核的属性。ChipScope 内核插入器。ChipScope Pro Analyzer 核分析仪。

在FPGA Editor 中修改ChipScope 核信号连接。

ChipScope Pro 相关IP 核

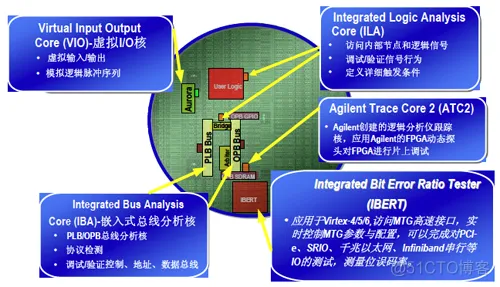

ChipScope Pro 提供了多种不同功能的调试内核,通常分成三类:逻辑调试内核、误比特率测试核和集成总线分析核。用户根据系统的调试要求,应用不同的调试内核,方便快速地找到设计中存在的问题。常用IP 核如图9-3 所示。

1) 逻辑调试内核。

ICON(集成控制器核)。ILA(集成逻辑分析核)。VIO(虚拟I/O 核)。ATC2(安捷伦跟踪核)。

2) IBERT(误比特率测试核)。

Virtex-4 FX 平台的IBERT(误比特率测试核)。Virtex-5 LXT/SXT/FXT 平台的IBERT(误比特率测试核)。Virtex-6 LXT/SXT 平台的IBERT(误比特率测试核)。Spratn-6 LXT 平台的IBERT(误比特率测试核)。

3) IBA(Integrated Bus Analyzer,集成总线分析核)。

IBA/OPB(集成总线/处理器外设总线核)。IBA/PLB(集成总线/处理器本地总线核)。

图9-3 常用ChipScope 的IP 核

一、 ICON 核

ICON 核具备与JTAG 边界扫描端口通信的能力,因此ICON 核是ChipScope Pro 应用必不可少的关键核。一个ICON 核可以最多同时连接15 个ILA、IBA/OPB、IBA/PLB、VIO或者ATC2 核。在Virtex-4/5/6 和Spartan-6 芯片中,可以通过BSCAN_VIRTEX 原语来使用USER1、USER2、USER3 或者USER4 扫描链,且由于BSCAN_VIRTEX 原语实现了一条单独的扫描链,因此就没有必要导出未使用的用户扫描链。在其余类型芯片中,只能使用USER1 或者USER2 扫描链。

二、 ILA 核

ILA 核提供触发和跟踪功能,根据用户设置的触发条件捕获数据,然后在ICON 的控制下,通过边界扫描端口将数据上传到PC,最后在分析仪(Alalyzer)中显示出信号波形。由于ILA 核和被监控的逻辑是同步的,因此设计中的所有时钟约束会被应用到ILA 核。ILA包括下面3 个主要组件:

输入、输出触发逻辑:输入触发逻辑用于检测各种触发条件;输出触发逻辑用于触发外部测试设备以及其他逻辑。数据捕获逻辑:数据捕获逻辑用于捕获数据,并将所捕获的数据存储到芯片的BRAM 中。控制和状态逻辑:控制和状态逻辑用于管理ILA 的各种操作。

三、 VIO 核

VIO(Virtual I/O)核是一个虚拟控制台,用于实时监控和控制FPGA 内部逻辑信号,可以观测FPGA 设计中任意模块的输出信号,也可以对这些模块添加虚拟输入,类似DIP开关、按键等,且不占用BRAM 资源。VIO 核面向模块操作,支持下面4 类信号:

异步输入信号:异步输入信号,由JTAG 时钟信号(TCK)钟控,周期地读入PC,结果显示在ChipScope Pro 分析仪的用户界面。同步输入信号:同步输入信号,由设计中的时钟钟控,周期地读入PC,结果显示在ChipScope Pro 分析仪的用户界面。异步输出信号 :异步输出信号,由用户在ChipScope Pro 分析仪中定义,送至周围的逻辑,输出信号的逻辑“1/0”由用户定义。同步输出信号:同步输出信号,由用户定义,与系统时钟同步,输出信号的逻辑“1/0”由用户定义。

四、 ATC2 核

ATC2 核由Xilinx 和Aglient 合作开发,配合Aglient 的最新一代的逻辑分析仪使用。ATC2 内核结构框图如图9-4 所示,可以看成一个可配置的多路复用器,输入为一些信号组,最大可以配置成64 个组。

图9-4 ATC2 结构图

Agilent 逻辑分析仪上运行一个FPGA 动态探测器的应用软件,用它可以观察从FPGA 输出的信号。

ATC2 实现了FPGA 与Aglient 逻辑分析仪的联合调试、捕获数据,允许Aglient 逻辑分析仪访问FPGA 内部任何节点,提供更深的捕获深度,具有更复杂的触发设置,并且支持网络远程调试,功能十分强大。与单独使用ChipScope Pro 相比,减少了BRAM 的使用。

ATC2 与Anlient 逻辑分析仪连接,可以为每个信号提供2M 的捕获深度,是ILA 的60倍。此外,最多允许在FPGA 内部添加64 个观测信号组,和逻辑分析仪的连接路径最多可达128 条。这非常有利于查找设计缺陷。

五、 IBERT 核

IBERT 核用于测量高速串行收发器多条通道上的误码率和实时调整高速串行收发器参数。BERT 核由三部分组成。

BERT 逻辑:BERT 逻辑例化RocketIO 收发器模块,包含了模式产生器和检测器。有多种模式可以选择,包括简单的时钟模式、完全伪随机二进制序列(PRBS)模式和帧计数模式。动态重配臵端口(DRP):每个Rocket I/O 收发器都有一个动态重配臵端口,因此,可以动态改变收发器属性。控制和状态逻辑:管理IBERT 核。

六、 IBA/OPB核

在Xilinx的FPGA中可以嵌入软核处理器MicroBlaze,在一些高端器件中还有IBM的硬核处理器核PowerPC,IBA/OPB核是专用于连接片上外设总线(OPB)的。IBA/OPB核主要包含四个部分:

协议冲突监测:监测和报告OPB总线冲突事件,最多32个。输入、输出触发逻辑。

触发输入逻辑监测OPB总线和其他用户定义事件。

触发输出逻辑触发外部测试设备和其他逻辑。数据捕获逻辑:用于捕获数据,并将所捕获的数据存储到BRAM中。控制和状态逻辑:管理IBA/OPB核操作。

七、 IBA/PLB核

IBA/PLB核是专用于连接片上外设总线(PLB)的。IBA/PLB核主要包含三个部分:

输入、输出触发逻辑。

触发输入逻辑监测OPB总线和其他用户定义事件。

触发输出逻辑触发外部测试设备和其他逻辑。数据捕获逻辑:用于捕获数据,并将所捕获的数据存储到BRAM中。控制和状态逻辑:管理IBA/PLB核操作。

注意:IBA/PLB核只用于PLB v46之前的PLB版本。XPS工具在PLB v46中提供了一个IBA核(chipscope_plbv46_iba),用于调试。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。