1 速度和面积

在全面优化水平将达到速度和面积RTL要利用逻辑拓扑的优势。

供FPGA由于在后端而言缺乏知识,门级优化。普通情况下更高的速度要求更高的并行性以及更大的面积,可是在某些特殊情况下并非这样。由于FPGA的布局布线具有二阶效应。

直到布局布线完毕。工具才会知道器件的拥堵或者布线的困难,可是这时实际逻辑拓扑已经被提交,假设我们的优化选项设置为速度,那么当实现后器件过于拥挤而无法布局布线时,布局布线工具进而会产生附加逻辑。从而是实际速度更慢。因此当FPGA的资源利用率接近100%时进行面积的优化将获得更快的速度。

2 利用综合工具提供的资源共享选项,能够实现一些互不相容的并且类似的操作,某些时候可能会减少面积,比如

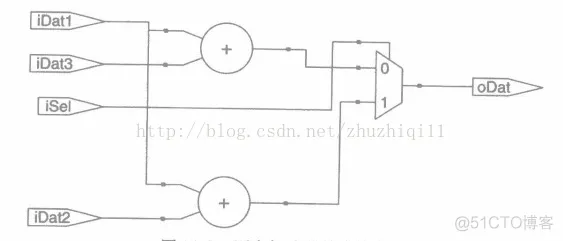

assign outdata=isel?idata1+idata2:idat2+idata3; 没有设置资源共享选项时实现例如以下:

.bmp)

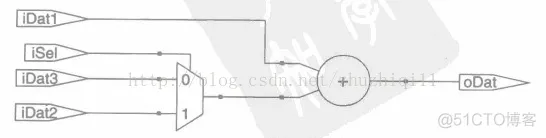

打开资源共享设置后:

3 流水线、又一次定时和寄存器平衡

a 寄存器平衡不应该用于非关键路径。

b 带有不同复位类型的相邻触发器会阻止寄存器平衡。

c 约束又一次同步寄存器,使其不被其它寄存器平衡影响。

4 有限状态机的编译

採用标准编码的状态机会被编译器识别而且又一次优化。

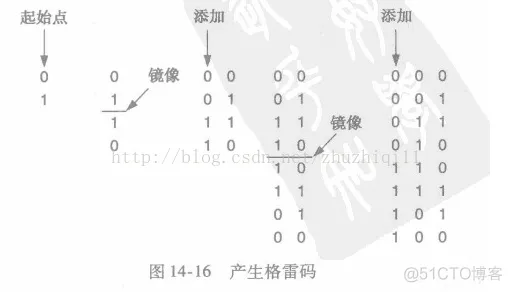

对于状态机,驱动异步输出时应该採用格雷码,格雷码产生例如以下图所看到的:

编译器会自己主动去除没用的状态。假设要求安全就别非常高。打开安全模式。无效的状态产生时将会产生一个复位信号。

5 黑匣子,黑匣子被放在优化模块的网表或者布局图的坐席。它包括在实现流程中的较后的设计总。

假设要求黑匣子时应该给出I/O的时序模型。

6物理综合提供综合和布局图之间的紧密联系。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...