1.verilog语言中操作数使用补码的形式处理数据,reg型数据可以赋正值,也可以赋负值。但当一个reg型数据是一个表达式中的操作数时,它的值被当作是无符号值,即正值,记得注意转换。

2.verilog语言算数运算中**代表指数运算,eg:2**M代表2M 。

3."按位异或"运算符^,"按位同或"运算符^~ 。

4.可以用触发器打拍子,一方面实现信号同步,以后好处理,一方面对于亚稳态的有效减少。

5.之前数据结构学的知识不止可以用在软件语言上,这些逻辑结构是客观存在的,算法是客观存在的。不管是硬件语言还是软件语言,只要能设计合适的存储结构即可,比如C++中对于队列思想的实现,可以用数组,也可用链表,同样,在硬件中可以用一个寄存器组来实现FIFO队列。

6.为了实现信号的高速处理,尽量把大任务分解成小任务,利用乒乓操作,流水线设计,串并行转换等(本质上是速度面积的互换)。

最大可能时钟频率是由电路中最慢的逻辑路径决定的,也就是关键路径,意思就是说每一个逻辑的运算,从简单到复杂都要在一个时钟周期内完成,同步电路往往会出现逻辑延迟过大,使得系统频率降低,采用流水线的设计思想,将复杂的运算分为数个简单的运算,可以帮助提高系统频率。

为确定电路的未来行为而必需考虑的所有历史信息。如果状态机的状态寄存器发生亚稳态后,稳定之后它们可以保持任何值,包括非状态机已定义的一组状态。

三段式状态机的优缺点:三段式描述方法虽然代码结构复杂了一些,但是换来的优势是:使FSM做到了同步寄存器输出,消除了组合逻辑输出的不稳定与毛刺的隐患,而且更利于时序路径分组,一般来说在FPGA/CPLD等可编程逻辑器件上的综合与布局布线效果更佳。

8.异步复位亚稳态的危害例子,如果复位时发生了亚稳态,那是多个寄存器都进入了眩晕状态,每个寄存器可能会复位,也可能不复位,那就有多种排列组合的情况,很有可能造成系统工作紊乱(比如状态乱飞)。

复位,同步释放。

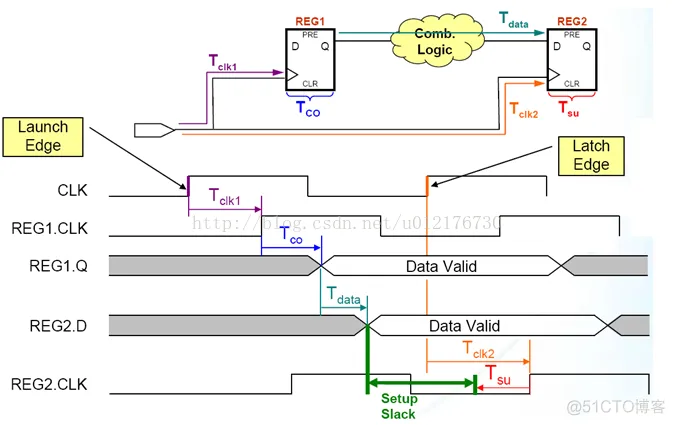

9.时序分析时大致可以分为四种情况,reg2reg是比较典型的,可以通过对其他情况的修改转化成reg2reg,这样便于分析。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...