FPGA中的布局布线资源主要包括三部分:CB、SB和行列连线。布线资源的目的是为了能够让位于不同位置的逻辑资源块、时钟处理单元、BLOCK RAM、DSP和接口模块等资源能够相互通信,从而协调合作,完成所需功能。FPGA中的布线资源,就好比绘制PCB板时的连线资源一样,虽然器件A和器件B的位置和连接关系没有任何改变,但很可能因为周边电路的布局、布线的一些变化,使得前后两次A、B之间的连线形态发生很大的变化。因此,与采用固定长度的金属线将所有宏单元连接在一起的CPLD不同,FPGA中任意两点之间的线延迟是无法预测的,必须等到布局、布线完成之后才能确定。这也是为什么在FPGA的开发中,时序约束和时序分析这两样工作是必不可少的。

接口资源是FPGA芯片的门户,它决定了FPGA芯片与外界交互的能力,因此接口资源是FPGA必须具备的一种资源。按照功能来划分,FPGA的外围接口有负责供电的,有负责接地的,有负责芯片配置的,有负责用户IO的,等等。而这其中最重要的就是负责用户IO的接口资源,按其承载信号的类型又可以细分为用户时钟管脚(一般仅指输入)和用户数据IO。一般来说,用户时钟管脚兼具用户数据IO的功能,但绝大多数数据IO不能兼具用户时钟管脚的特性。区分用户时钟IO和数据IO的关键,就是看其是否有直接连接到时钟网络资源的通路。如果有直接连接到全局时钟网络资源的通路,那么这是一个全局时钟管脚;如果有直接连接到区域时钟网络资源的通路,那么这是一个区域时钟管脚;如果有直接连接到IO时钟网络资源的通路,那么这是一个IO时钟管脚。 当然,做为FPGA芯片制作厂商,它会提供详细的管脚属性资料供大家区分这些管脚,从而达到正确、恰当使用的目的。

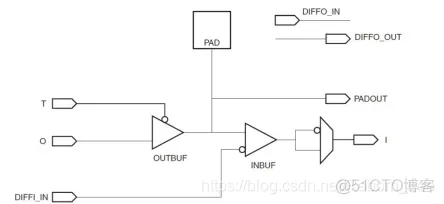

针对用户IO资源,Xilinx公司的IOB(Input Output Block)以及Altera公司的IOE(Input Output Element)是其中的代表。用户IO资源最基本的功能就是必须支持单端或差分的输入、输出、双向以及三态模式,因此用户IO的基本原理图如下:

其中,PAD代表FPGA芯片的金属管脚。

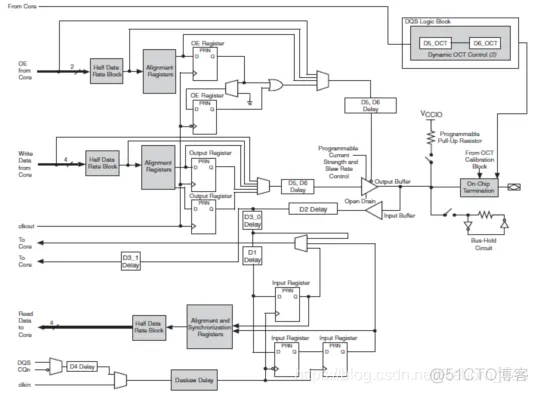

除此以外,当传输速度较高时,从用户IO资源到内部逻辑资源块之间的延迟就会显得不可忽略,因此,为了配合较高速度的接口传输,用户IO资源中必须集成一些专有的寄存器和精确的延迟调整功能,来完成较高速度的SDR或者DDR的输入、输出功能。例如,集成了相关功能模块的用户IO资源类似下图:

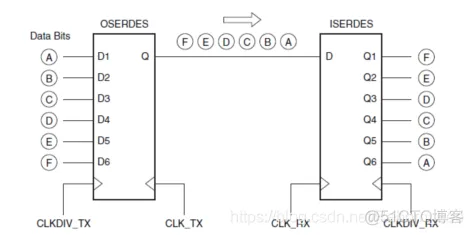

为了进一步提升接口传输的性能,增加用户使用的便利性,各大FPGA厂商又在用户IO资源中集成了名为SERDES的串并转换器,其中用于输入的叫做ISERDES,用于输出的叫OSERDES。相比于SDR、DDR的模式,SERDES能够做到1:6甚至更高的串并转换比率。下图就是SERDES的工作原理,大家可以参考理解。

最后,用户IO资源还必须支持LVTTL、LVCMOS、LVDS等多种数字电平,有的用户IO资源甚至内部嵌入了用于高频匹配的电阻,这样在电路板布线时,可以省去一些板载的匹配电阻。

为了适应目前越来越高的串行通信速率要求,各大FPGA厂商也早已开始在自己的FPGA产品中嵌入专门的硬件资源用于超高速的串行通信。例如Altera公司的Rocket IO资源和Xilinx公司的Transceiver资源。目前来说,这两种专有的硬件资源都已经能够支持最高达28Gb/s的串行通信速率。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...