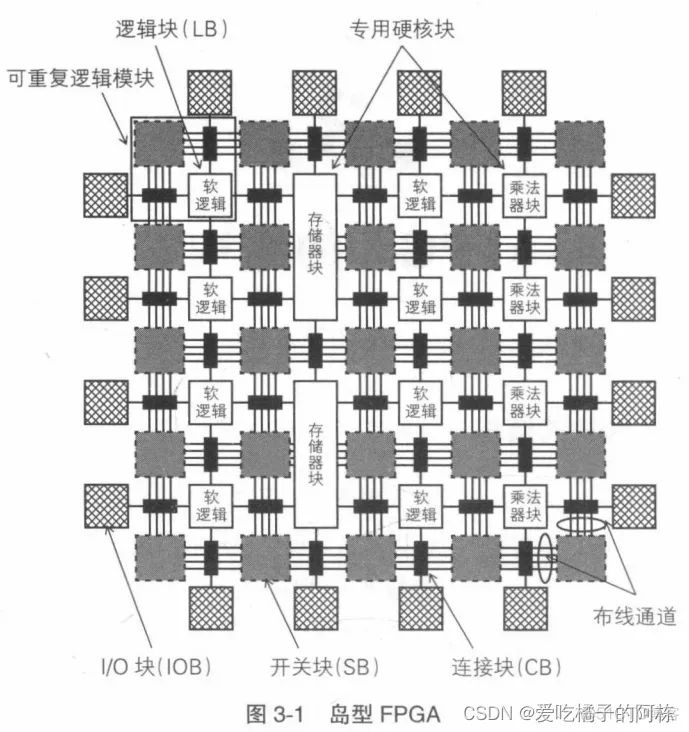

常见的FPGA都属于岛型FPGA,结构如下图所示。

FPGA的组成要素主要是:

①逻辑块 ②IO块 ③开关块 ④连接块 ⑤布线通道 ⑥专用硬核块

一、逻辑块

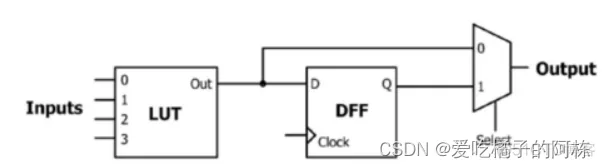

商用FPGA的逻辑块主要是通过查找表(Look Up Table,简称LUT)、触发器和多路选择器组成,结构如下图所示:

电路中的组合逻辑由LUT实现,比如上如所示的是一个4输入的LUT,它就能够实现4输入的组合逻辑。

电路中的时序逻辑由触发器实现。

多路选择器用来选择逻辑块使用的是组合逻辑还是时序逻辑。

那么为什么LUT能实现组合逻辑呢?下面就要讲讲LUT的结构。

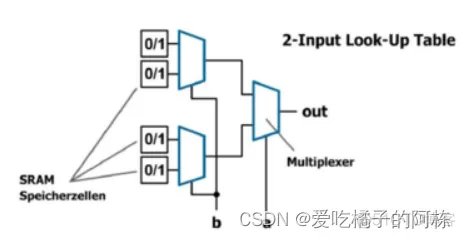

下图是一个2输入的查找表的结构示意图:

LUT的组成要素主要是:

①SRAM ②多路选择器

SRAM可以用来存储逻辑1或0,多路选择器用来选择输出哪个SRAM中存储的值。

对FPGA进行配置的过程实际上就是对SRAM中逻辑值的编辑过程。

简单的来讲,一个2输入的LUT可以看成一个2输入的真值表,所以通过在4个SRAM中编辑0或1的逻辑,2输入的LUT能够实现所有2输入的逻辑。

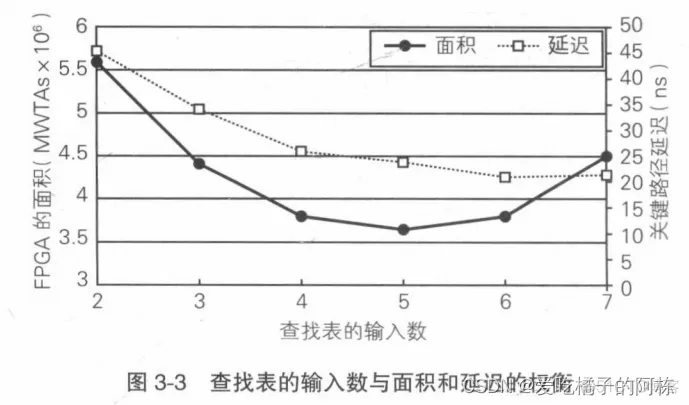

通过2输入的LUT可以推广到n输入的LUT,但是LUT的输入数并非越多越好也非越少越好,因为LUT的输入数越多虽然可以描述更复杂的逻辑以至于加快电路速度,但是在实现简单逻辑时会造成资源的浪费,LUT的输入数很少的情况下会使得描述一个复杂逻辑需要多个LUT以至于减慢电路速度,所以LUT的输入数需要考虑资源和速度两个方面来作一个权衡。下图描述了查找表的输入数和与面积和输出延时的权衡:

由上图可以看出,LUT的输入数在4~6个时面积和速度方面的性能最好,所以在商业FPGA中基本都是选择使用4~6个输入的LUT,比如在Xilinx的7系FPGA中用的就是6输入的LUT。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...