我们知道进行FPGA开发的时候,用的某家的芯片,都会用这家的开发环境,他们都有自己的仿真器,Xilinx有ISE,Altera有Quartus II,但是这些厂家的仿真器是不如专业EDA厂家的仿真器好用,就比如HDL硬件描述语言仿真软件工具Modelsim,如Modelsim AE(Altera Edition) 和 Modelsim XE(Xilinx Edition)。它是唯一的单内核支持VHDL和Verilog HDL 混合仿真的仿真器,在做FPGA和ASIC设计的时候,RTL级和门电路级电路仿真一般都会选择Modelsim。编译代码与仿真平台无关,便于保护IP核,同时定位编译错误也很快。Modelsim SE是版本最高的,编译速度最快。而上面提到的AE、XE输入OEM版本,是专门集成在FPGA厂家设计工具中的版本。

1.前仿真,功能仿真: 纯粹验证电路功能是否符合要求,不考虑电路门延迟与线延迟。写完HDL代码后就可以直接仿真,在设计综合之前,进行RTL级仿真。

2.后仿真,时序仿真: 真实反映时序的逻辑与功能,考虑电路门延迟与线延迟。这是在布局布线之后进行的。

RTL级侧重的是寄存器以及寄存器之间的逻辑,绝大多数的电路都可以看做是寄存器进行数据存储,数据处理,处理的流程由时序状态机控制,这些处理就可以用硬件描述语言来描述。

RTL级和门级区别在于,RTL是用硬件描述语言Verilog或VHDL描述,门级则是用集成好的具体的逻辑单元(依赖厂家的库)来实现功能,门级设计完最后可以加工成实际的硬件。实际上,RTL和门级是设计实现上的不同阶段,RTL经过逻辑综合后,就得到门级。

RTL描述可以表示为一个有限状态机,或是一个可以在一个预定的时钟周期边界上进行寄存器传输的更一般的时序状态机,用VHDL和Verilog两种语言进行描述。

RTL级与门级.

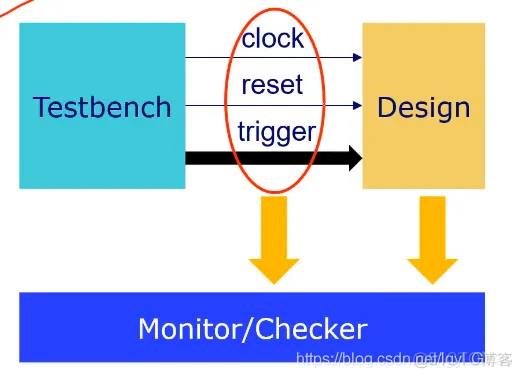

Design就是顶层RTL文件,TestBench提供时序,复位和触发信号,Design的信号也可以被仿真软件抓取到,是一个完整的闭环,而Monitor就是显示,如波形等。

1.设置工作路径

2.创建工程

3.编写 Verilog 文件和 Testbench 仿真文件。

4.编译(全编译和单独编译)

5.启动仿真器并加载设计顶层

6.运行仿真

补充一个编译的小坑:

output a;

wire a;

//这样会报错,因为output默认就是wire类型,

//所以这样编译会报错:重复定义。 只需要删掉wire a即可。

此时执行完的仿真首先是能看到波形,判断代码功能是否正确,是功能仿真,之后,添加仿真库、网表和延时文件,再进行 后仿真。

以串口UART为例,编写tb代码

***************************************************************

仿真文件中定义端口,在RTL文件中的input换为reg,

output换为wire型。 以分号;结尾

***************************************************************

`timescale 1ns/1ns

module uart_loopback_top_tb;

reg sys_clk ; //外部50M时钟

reg sys_rst_n ; //外部复位信号,低有效

reg uart_rxd ; //UART接收端口

wire uart_txd ; //UART发送端口

//初始化

initial begin

sys_clk <= 1'b0;

sys_rst_n <= 1'b0; //初始化赋值为0

uart_rxd <= 1'b1; //因为rxd是拉低一段时间之后表示start,所以初始化要拉高

#100 sys_rst_n <= 1'b1;

//为了避免竞争冒险,先延迟10ns再来下降沿

#10 uart_rxd <= 1'b0;

***************************************************************

50M/115200 = 434个时钟周期,也就是说一个01信号要等待434个时钟周期才是一个有效的01信号。而一个时钟周期是20ns,所以434*20ns = 8680ns

***************************************************************

#8680 uart_rxd <= 1'b1; //因为是模拟,随意赋值,一共八句

#8680 uart_rxd <= 1'b0;

#8680 uart_rxd <= 1'b1;

#8680 uart_rxd <= 1'b0;

#8680 uart_rxd <= 1'b1;

#8680 uart_rxd <= 1'b1;

#8680 uart_rxd <= 1'b0;

#8680 uart_rxd <= 1'b0;

//停止位

#8680 uart_rxd <= 1'b1;

end

***************************************************************

之后,需要将对象例化进来

***************************************************************

uart_loopback_top uart_loopback_top_u( //例化习惯用_u命名

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.uart_rxd (uart_rxd) ,

.uart_txd (uart_txd)

);

//生成50M的时钟

always #10 sys_clk = ~sys_clk;

endmodule

1.选择路径

Modelsim必须是绝对路径,也就是必须是原来的路径才能工作,不想ISE工程,复制粘贴到另外一个地方照样可以打开,但是Modelsim不行。

File——Change Directory——选择路径

2.创建新工程,输入设计源文件

命名与tb文件相同;

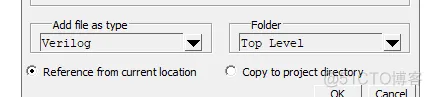

Add Existing File,把tb文件和rtl的.v文件全部加载进来

修改文件内容:右击文件——Edit——保存

编译:某一文件右键——Compile All

3.启动仿真 Start Simulation

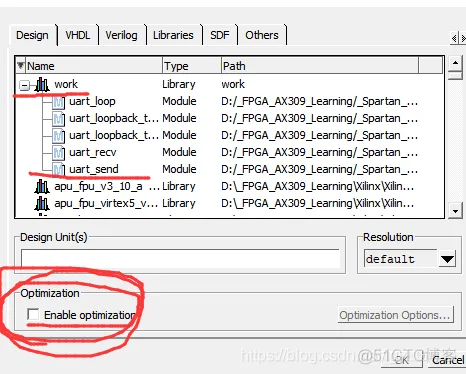

Design、VHDL、Verilog、Libraries、SDF 和 Others共6个标签。

用的最多的是 Design、Libraries 和 SDF 。

(1)Design:

Resolution 选项,这里可以选择仿真的时间精度,一般都是默认;如果设计文件中没有指定,则按 1ns 来进行仿真;

最下面的 Optimization使能优化,一定要去掉。

(2)Libraries

Search Libraries、Search Libraries First 功能基本一致,不同在于 Search Libraries First 中指定的库会在指定的用户库之前被搜索。

(3)SDF 【Standard Delay Format(标准延迟格式)】

包含了各种延迟信息,用于时序仿真的重要文件。SDF Options 区域设置 SDF 文件的 warning 和 error 信息。“Disable SDF warning”是禁用 SDF警告,“Reduce SDF errors to warnings”是把所有的error变成warning 。

Multi-Source delay 可以控制多个目标对同一端口的驱动,如果有多个控制信号同时控制同一个端口或互连,且每个信号的延迟值不同,可以使用此选项统一延迟。有三个选项:latest、min 和 max。latest选择最后的延迟作为统一值,max选择所有信号中延迟最大的值作为统一值,min选择所有信号中延迟最小的值作为统一值。都完成之后就可以点击OK了,这里需要注意,在Design这里一定一定要选中tb文件再ok,否则出不来波形,我最开始就是这个错误,导致左侧栏的文件都有错误。

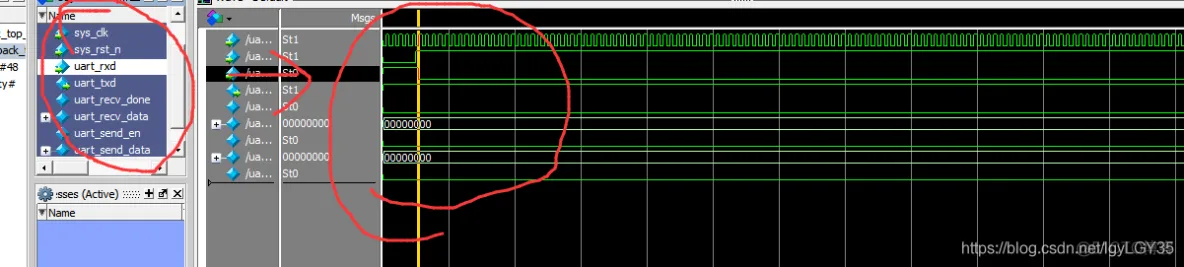

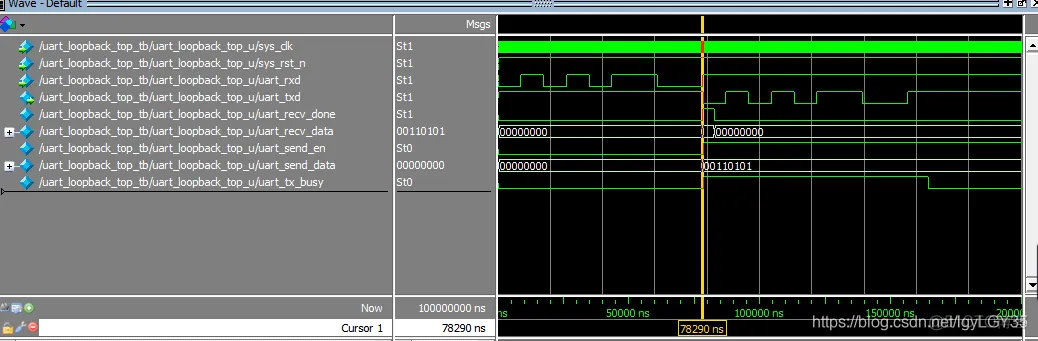

OK之后,波形如下,信号的标注在左侧,

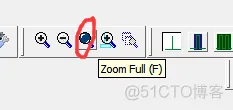

4.观察波形

波形缩小,看到如下,数据与tb文件中相同

就可以看到1us的波形了

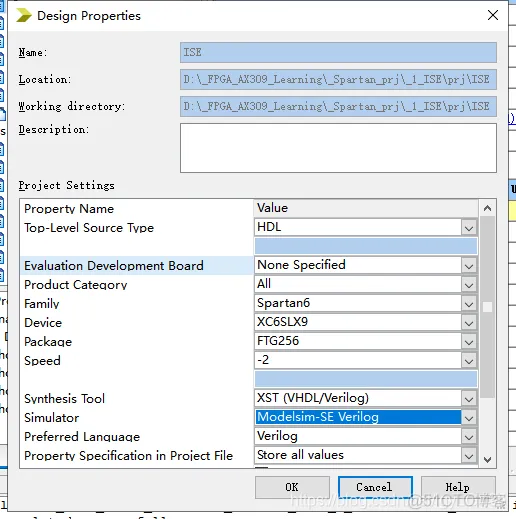

首先将ISE与Modelsim关联起来…

然后,修改ISE中仿真工具

仿真只需要Synthesize即可。双击

之后, 弹出一个WARNING,点击No即可。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...