布线问题

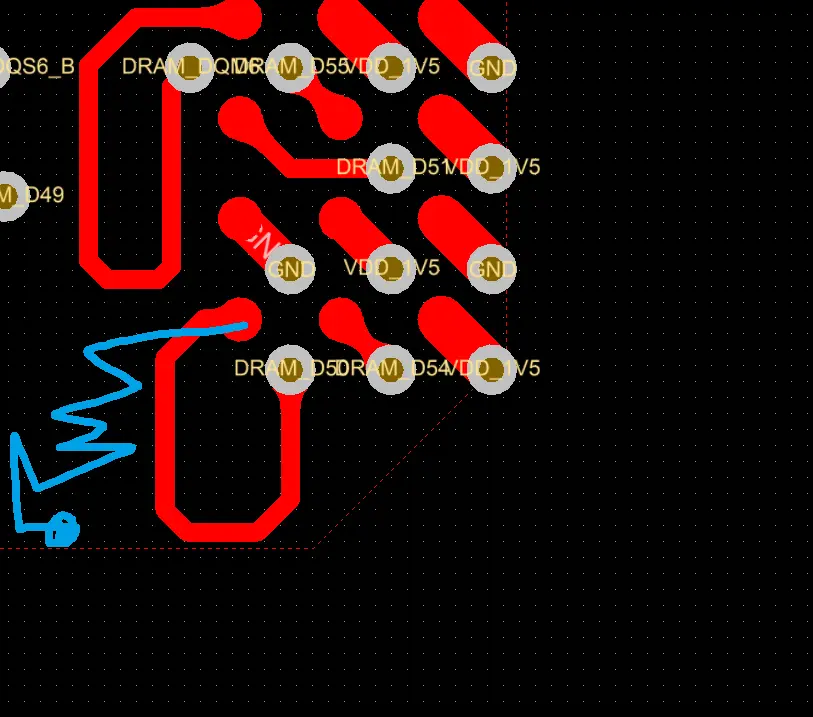

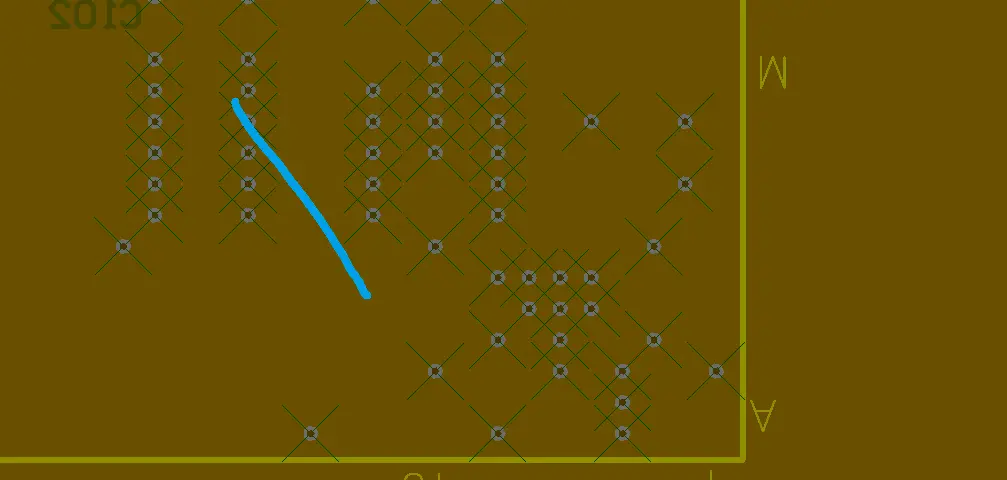

1.【问题分析】:走线等长出现环路,这种环路是不允许出现的,禁止这样进行环路出线,会造成干扰吸收。

【问题改善建议】:可以采用其他方式出线。

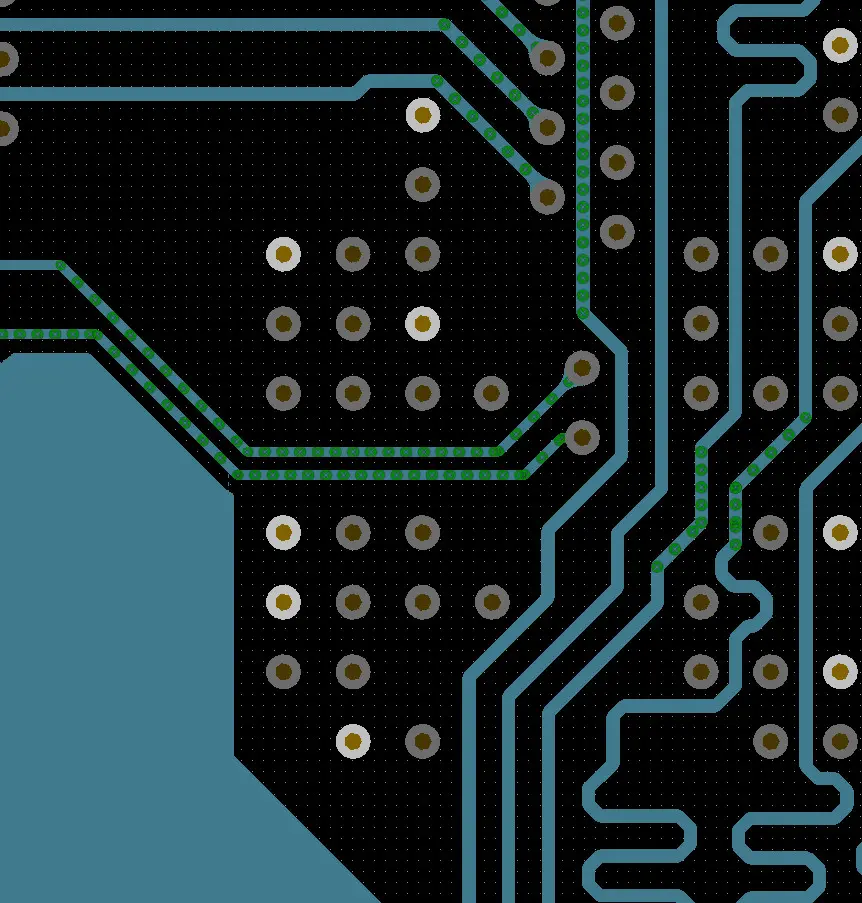

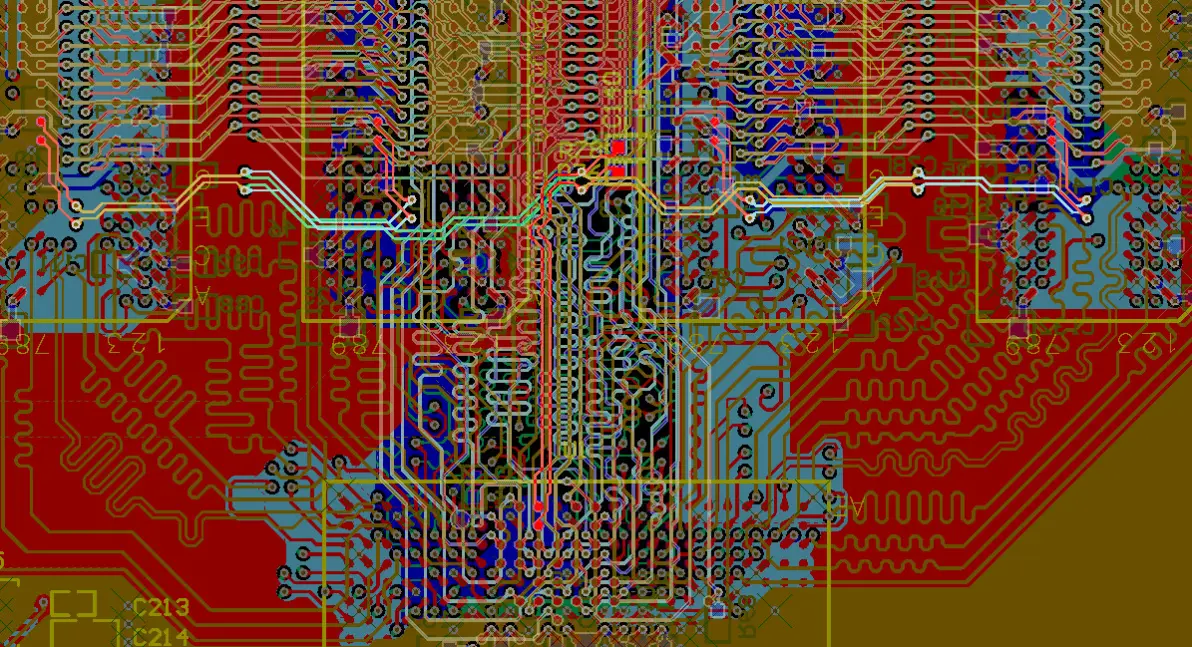

2.【问题分析】:走线3W处理,这个是一定要遵循的原则,不然信号会出现严重干扰,同时走线可以按4mil处理,后期通过阻抗来调整,差分就按照一根线来看间距。

【问题改善建议】:建议重新修改间距,这里的间距需要重新修改。

3.【问题分析】:走线按照2S进行走线处理。

【问题改善建议】:建议重新进行更改此处。

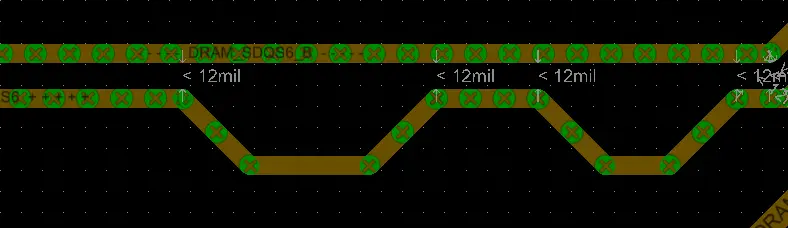

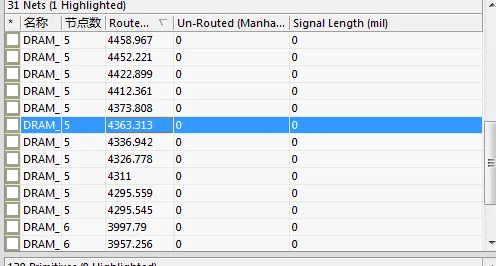

4.【问题分析】:所有的地址线的等长没有保证在一个等长的范围内。

【问题改善建议】:

DDR:单端50欧差分100欧、3W、数据线同组同层,最好包地隔离、数据等长+-25mil、地址等长+-100mil。

DDR2:单端50欧差分100欧、3W、数据线同组同层,最好包地隔离、数据等长+-15mil、地址等长+-100mil。

DDR3:单端50欧差分100欧、3W、数据线同组同层,最好包地隔离、数据等长+-10mil、地址等长+-25mil。

DDR4:单端50欧差分100欧、3W、数据线同组同层,最好包地隔离、数据等长+-5mil、地址等长+-20mil。

5.【问题分析】:过孔的处理注意好,不要随便 打流氓孔。

【问题改善建议】:修改好过孔的美观性。

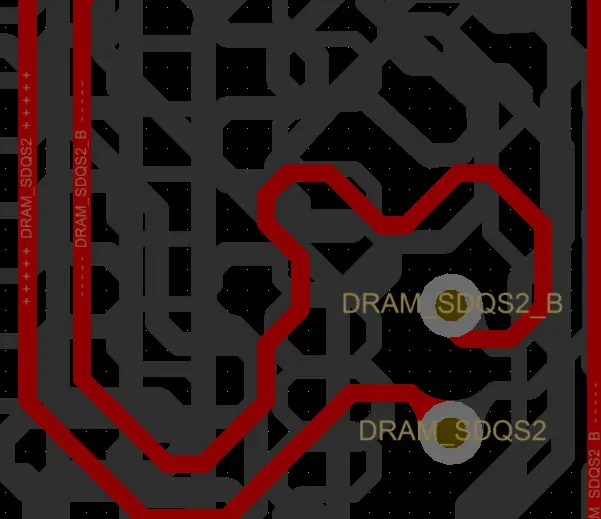

6.【问题分析】:T点 走线保证一个T点一个层,比如这对差分在中间开始出线,第二个T点的所有线保证在一个层中,然后在T点的第三个分叉保证T点的走线还是在一个层中,这样保证信号的时序性好和回损性小。

【问题改善建议】:建议修改两边的同一等级的线的等长的层。

更多技术干货请扫码关注

技术老师请加 V X:15616880848

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。