Ansys® Totem-SC™、Ansys® PathFinder-SC™等全新产品助力优化汽车、5G和高性能计算半导体的功耗与可靠性

主要亮点

Ansys宣布推出两款全新的半导体产品——分别是面向电源完整性签核的Ansys® Totem-SC™和面向静电放电(ESD)可靠性签核的Ansys® PathFinder-SC™。新产品将现有的Totem™和PathFinder™产品集成到Ansys SeaScape™大数据平台中,通过分布式处理能力显著提升其速度和功能。上述举措,可进一步助力Ansys实现其采用开放式可定制设计平台赋能多物理场工程仿真的战略承诺。

Totem-SC基于SeaScape平台构建,能够充分解决当今超大规模存储芯片设计和模拟混合信号芯片设计中日益复杂的电源完整性分析挑战。作为一款大规模可扩展数据平台,SeaScape利用大数据技术实现高度扩展性的弹性计算,并加速多物理场分析工作。Totem-SC可让新一代设计的动态压降签核工作速度平均提升10倍,如互补金属氧化物半导体(CMOS)图像传感器、动态随机存取存储器(DRAM)、闪存、现场可编程门阵列(FPGA)和高速收发器等。

三星电子公司副总裁Seonil Brian Choi表示:“电源噪声是我们CMOS图像传感器的一项关键指标,因为它会直接影响像素性能。Totem-SC使用标准的小内存机器,为三星的高分辨率传感器设计提供性能卓越的压降签核解决方案。高保真度的仿真结果让我们的团队能够信心十足地最大限度优化设计,从而开发出更优质的最终产品。”

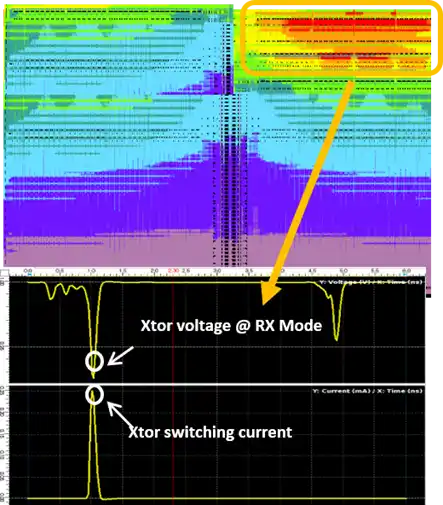

图为Ansys Totem-SC展示的在电网中的压降区域

PathFinder-SC是一款功能强大的解决方案,可用于验证所有芯片的保护电路,这种电路可防止芯片因静电放电(ESD)和电压峰值而受到损坏。随着芯片技术工艺节点缩小至7nm及以下,这项技术变得日益重要,因为微小的晶体管需要关键ESD电路的保护,而该电路的检查、验证和签核工作正是PathFinder-SC的用武之地。凭借SeaScape技术,PathFinder-SC能够使超大规模SoC的签核速度加快10倍,因此非常适合当今人工智能、成像、网络、5G和6G通信应用中的大型高速半导体设计。

三星电子技术副总裁Chanhee Jeon表示:“随着设计规模不断扩大,对预测准确度的要求日益严格,ESD签核的难度也在加大。我们发现,PathFinder-SC可提供具有出色根源分析和多物理场分析功能的高性能ESD签核解决方案,从而帮助我们充分满足交期要求。”

SeaScape的大数据弹性计算算法非常适合可扩展、分布式部署,因为它使用常规大小的机器,而不需要消耗具有大量内存的大型主节点机器资源。SeaScape平台采用开放式平台架构,允许客户通过基于Python的可定制用户界面(UI)与其它工具和自定义算法相集成。

Ansys副总裁兼电子、半导体与光学事业部总经理John Lee表示:“当今的芯片和电子系统设计工作包含日益复杂的多物理场分析与仿真,因此需要一系列丰富的工具才能完成求解。Ansys坚信,SeaScape这样的开放式可扩展平台,可以让用户能够始终(从早期原型构建到制造签核)利用最佳的工具完成其产品设计的仿真、分析和优化工作。”

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。