先对前述文章做个补充:

有的接插件是有机械孔的,这个mechanical hole有讲究,字不重要看图:

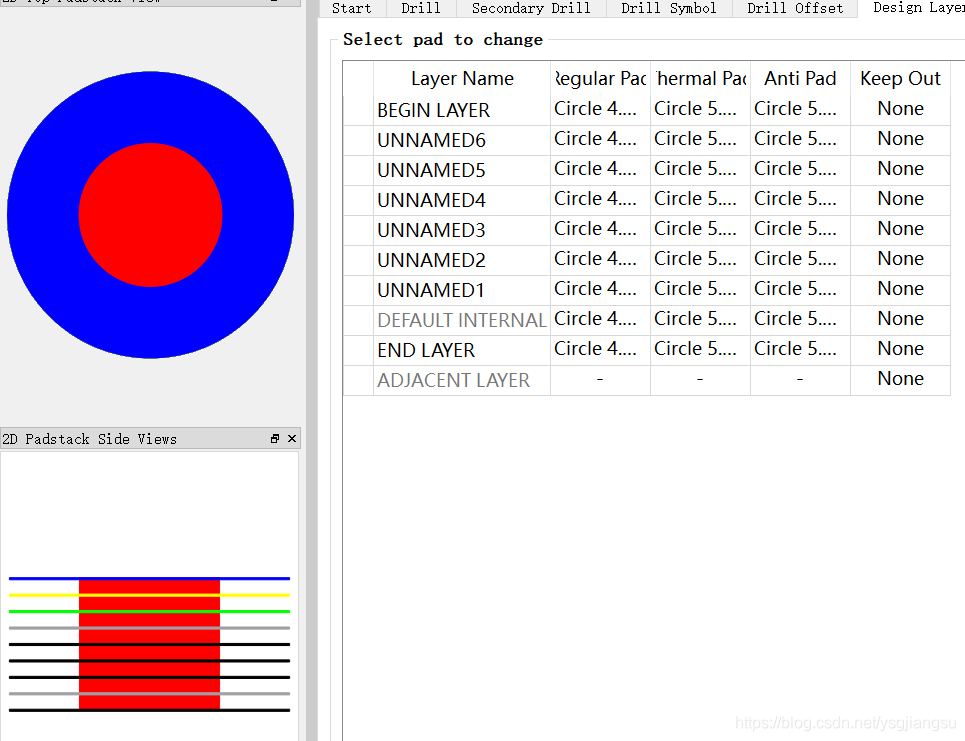

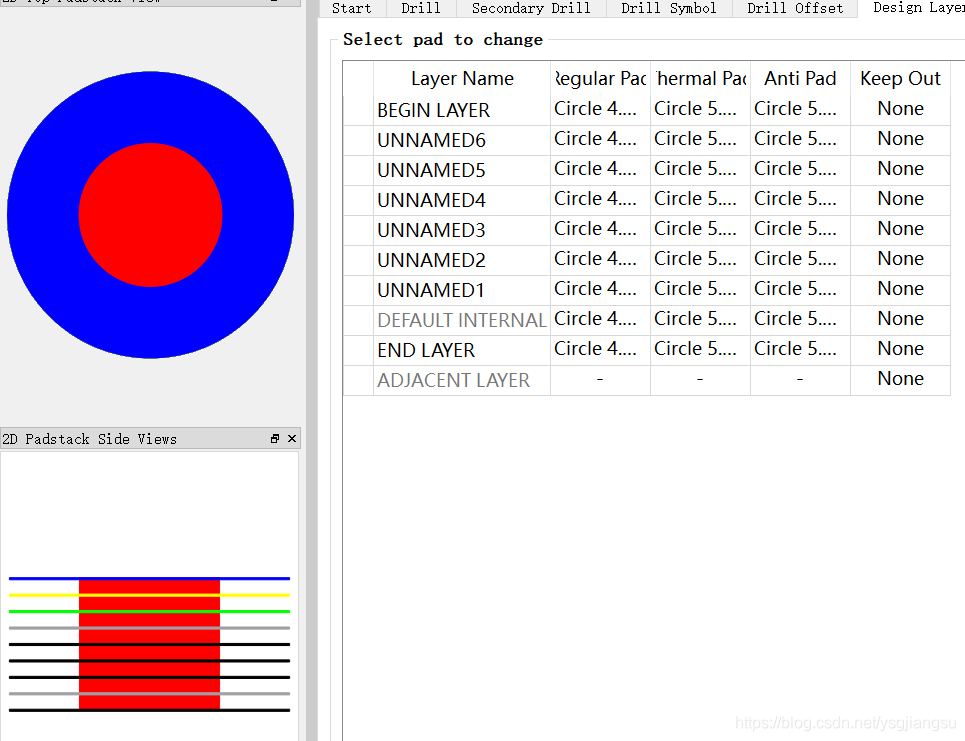

需要指明每一层的连接几何尺寸,17.2最高支持32层VIA,所以要问,我就画四层板,中间不应该是两层么,你整这么多层?没问题!用不上的层,自动忽略了。

菜鸟初成

零零散散的要点:

- 当发现元件封装画错了怎么办? 打开元件封装,重画。然后 选择你想要的更新的元件封装,单击左下角的refresh按钮就行了(前提是你待更新的元件在当前PCB中未被fix,如果被fix了,那就unfix解除之后再更新)

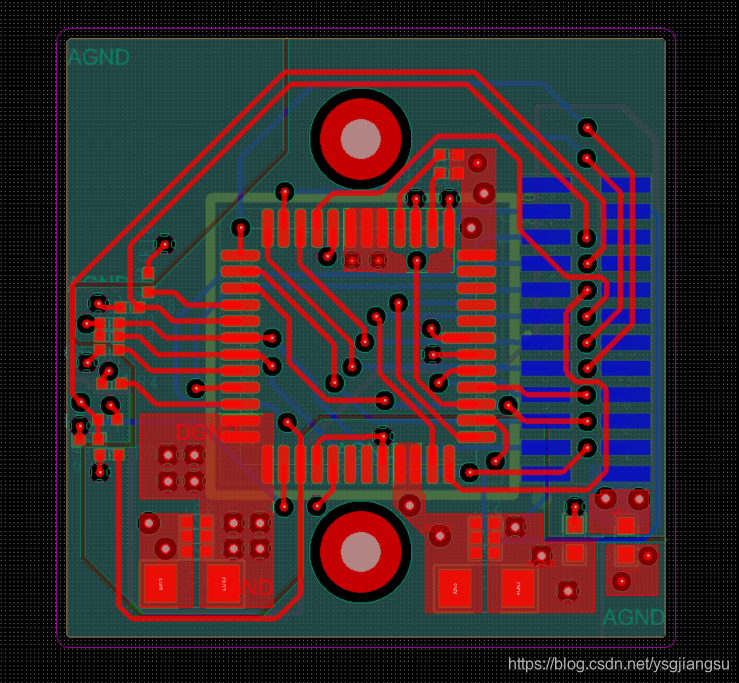

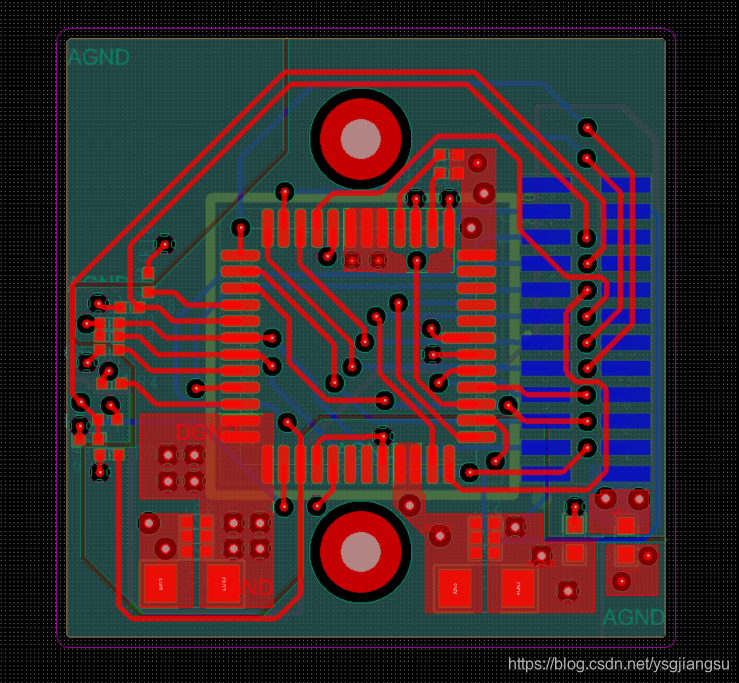

- 在内电层分割的时候,如何高效操作? 先把地相关的NET高亮起来,比如PCB包含AGND和DGND两种地,分别着不同的色就好了。先单击刷子,再选个颜色 选你想要高亮的NET,单击就好。由于我这里已经分割了内电层,所以整块区域都亮了。 不想这么闪耀,回到过去? 取消高亮就行了,选ALL 另外,不要怪allegro颜色暗淡,是因为你没有调光,如下图:

- 一般需要用fill处理的部分,画块几何图形就好了 只不过需要你指定一下,net name,软件自己不去体会的。

- 画了多个几何图形,也叫shape,如何合并? 然后依次点击需要的合并的shape就好了。

- 我只是想放些过孔,比如电源附近,怎么搞 通过布线按钮,在需要的NET上双击,便得到VIA。然后借助copy命令,把这个VIA按照一定的几何关系摆放下去。效率相当高! 明明FILL重叠了为什么也不避让? 那是因为你没有设置smooth: 先说这个情形只发生在动态铜且未开启smooth,但是为什么不报错? 这需要解释一下dynamic fill选项: smooth:铜皮会自动实施避让 rough:用于显示铜皮的连接,注意在输出光绘文件时,需要选择smooth disabled:铜皮不会实时避让,需要单击update to s

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删