软件

产品

一个学习信号完整性的layout工程师

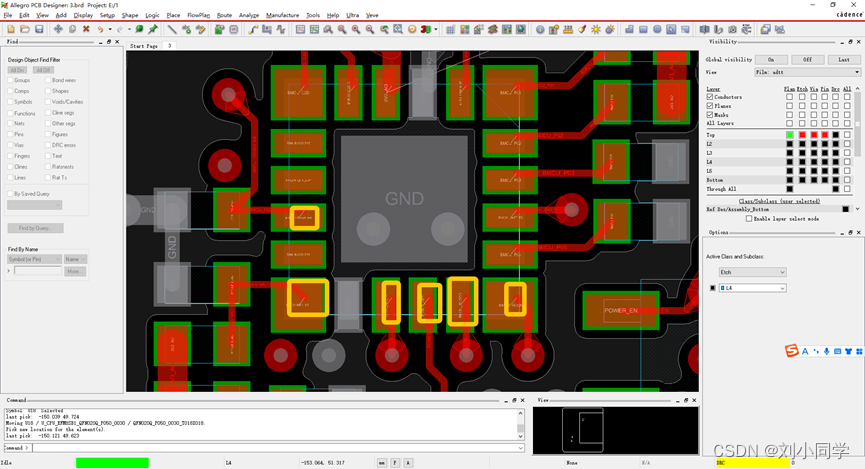

在进行设计PCB时,经常会复用之前的参考设计,或者将其中的某一模块copy过来。因为之前的设计是经过测试验证的,所以有些相同的模块就没必要重新layout。避免引入未知的问题,但是在这个模块的导入或导出时,经常会遇到一些网络断链的情况。比如我们导出和导入布局时,因为设计单位的不同或者规则设计不一致,会出现下面的这种情况:

会有各种小飞线,如果我们在不想要改动布局或者器件布局合理的情况下,我们可以使用如下命令进行操作:

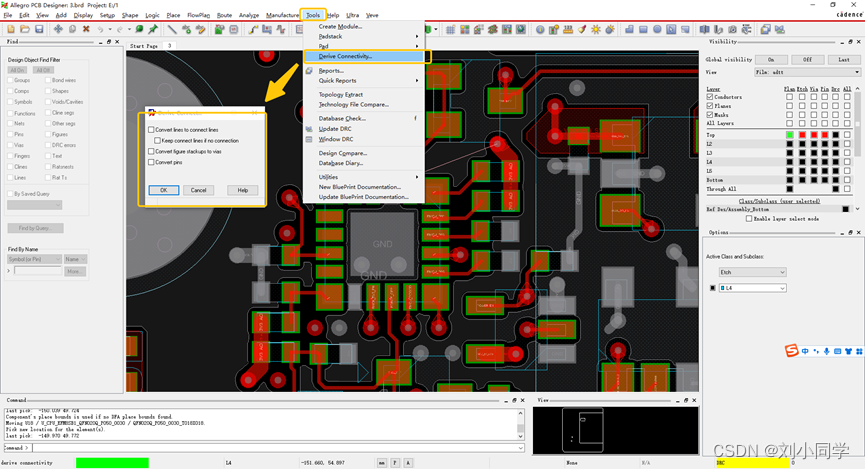

在Allegro的菜单下选择Tools命令,点击Derive connectivity,会弹出如下 对话框 :

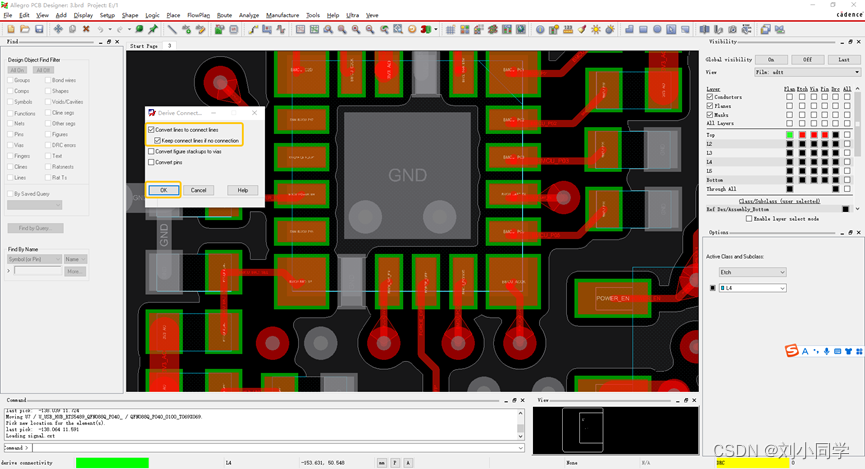

连接飞线,一般勾选前两个命令,点击OK,就可以看到飞线消失了,如下图所示:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删