********************************************************************************************************************************

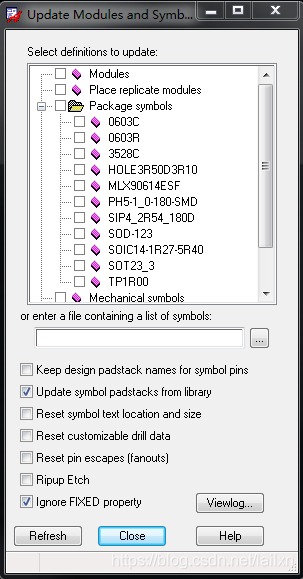

封装修改后,在allegro下palce--update symbols。在package symbol下选择要更新的封装。

注意勾选如果更改过pad请注意勾选 :update symbol padstacks;

如果是固定的器件还要记得勾选:Ignore FIXED property。

配图allegro 16.6:

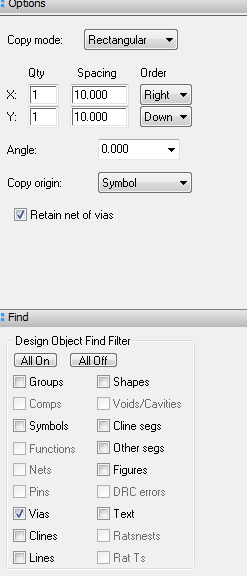

比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观

Copy

Find勾选Via

Option数量间距,如果还想保留via的net,还要勾选 Retain net of vias。如下图:

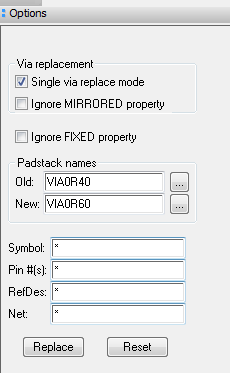

答: Tools ->PadStack->Replace,然后必须选上Single via replace mode,最后选上要想替换的过孔即可;

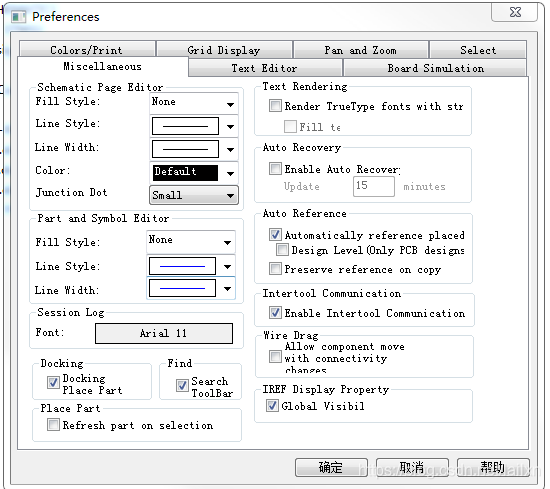

打开原理图和 PCB, 在 OrCAD 中 Option–Preferences 设置 Miscellaneous,勾选 Enable Intertool Communication。如下图:

Edit ->Text,然后选中PIN Number修改即可。

用ORCAD画原理图,很多ORCAD的SCH中,大多在offpage connector 加上一个页码。方法很简单:Tools->annotate->action->add intersheet reference即可。

选中该Net,然后Edit->Properties,按下图修改其属性即可。或者也可以依次点击Tools->Setup Advisor->Next->Next->Identify DC Nets->填入网络的Voltage即可。

更改信号线的宽度(Edit\Change\Find\Clines)option\linewidth

删除信号线(Edit\Delete)

改变信号线的拐角(Edit\ Vertex )

删除信号线的拐角(Edit\Delete Vertex)

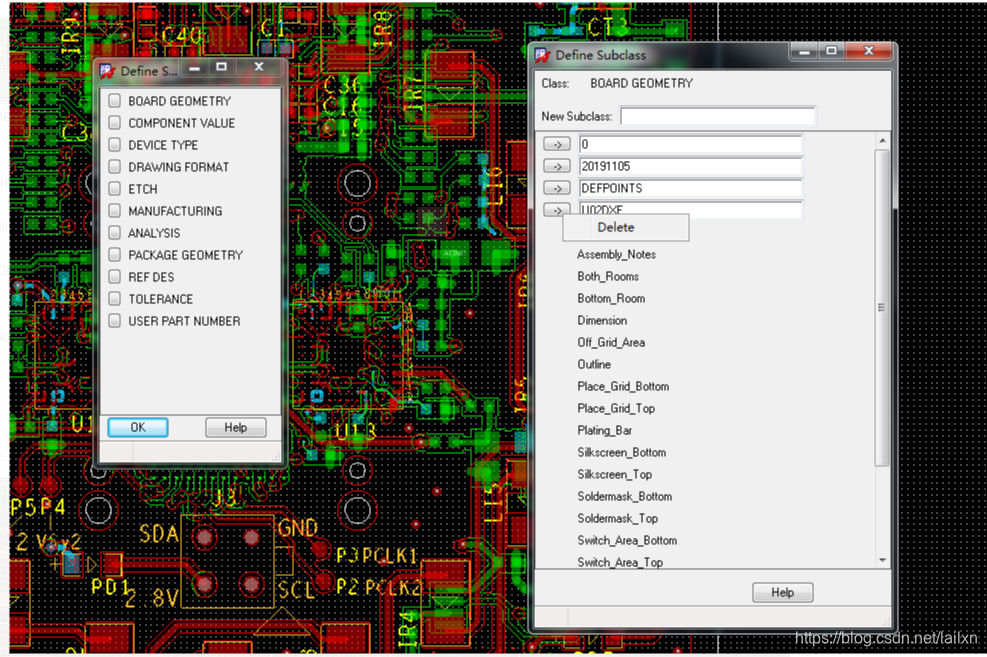

Setup---Subclasses---BOARD GEOMETRE

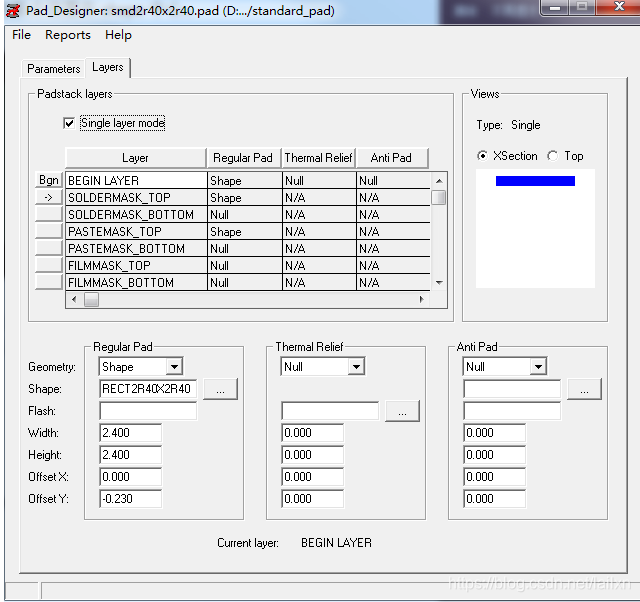

去检查焊盘的offset,在画封装时,调整好坐标即可。如下图的offset是y=-0.23。实际放置焊盘时,将坐标设置为x 0 0.23即可对准中央。

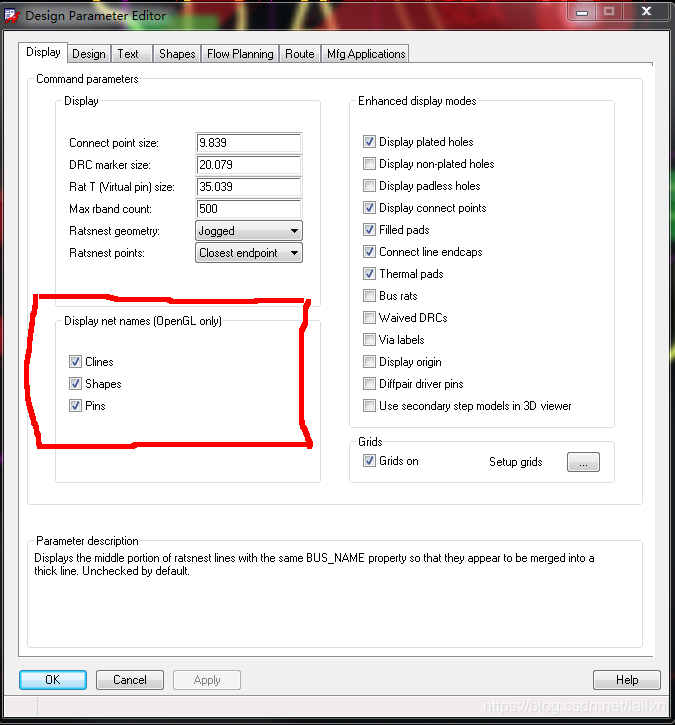

Setup-Design parameter Editor---Display net names

解决方法:安装补丁。

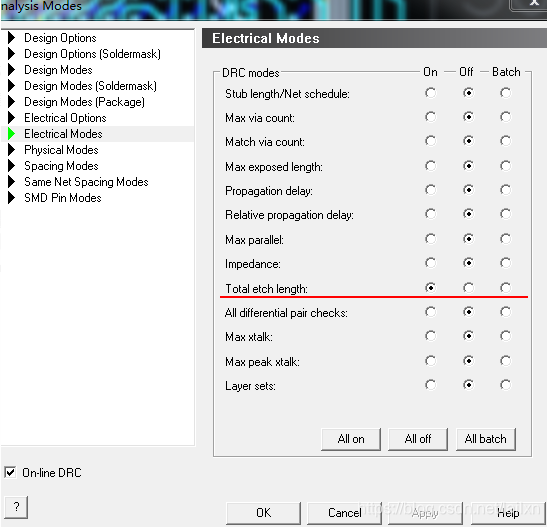

setup-constraints-constraint Manager--ELECNET-Routing--Total Etch Length--选用对应的NET右键Analyze 即可

首先先要打开Total Etch Length 这一项

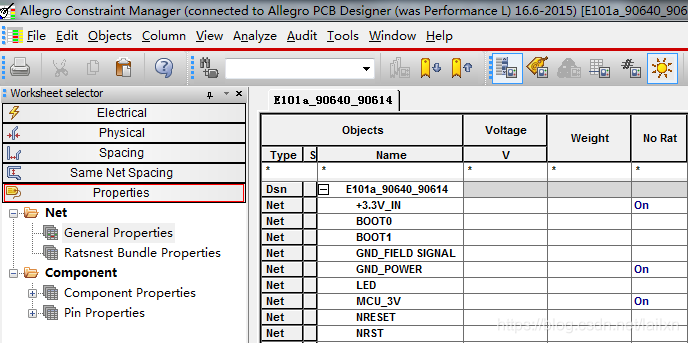

Cadence Allegro菜单栏”Edit->Net Properties…”,然后会弹出”Allegro Constraint Manager”对话框(即我们常说的约束规则管理器对话框),并会自动切换至“Properties”选项卡,我们在节点“Net->General Properties”下搜索对应的网络,如“GND、VCC-3V”,在对应的“Not Rat”列设置为“On”状态,即可隐藏对应的飞线啦。如果要取消隐藏,则选择“Clear”。

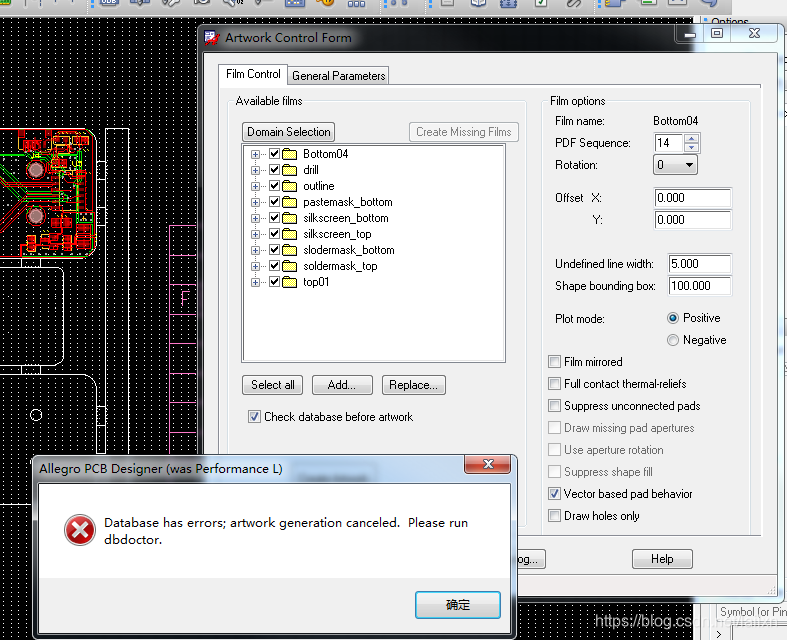

错误入图:

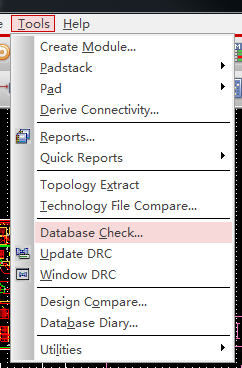

解决方法:Tools--Database check。

新建.brd文件。

导入dxf文件(file-inport-dxf),dxf文件定义了板子上的器件或者接口放置的位置,板子的外形等等。

利用dxf文件画板框(16.6在 outline 层,17.2要画在design outline层),采用change命令,画route keepin,翻译过来就是PCB布线的区域,超过这个区域的布线无效采用edit---z-copy命令。

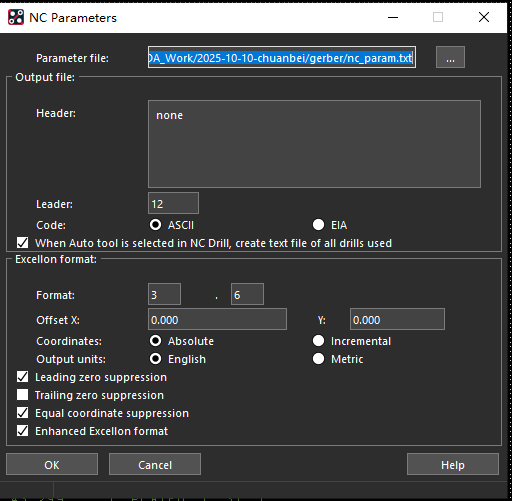

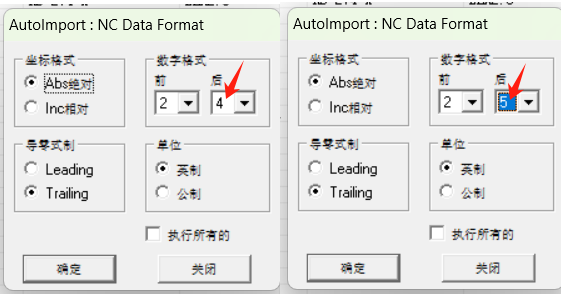

(1)尤其记得勾选enhanced 哪一项

(2)如果还不行 就用记事本打开.drl文件,删除 ;design :***.brd那一行。

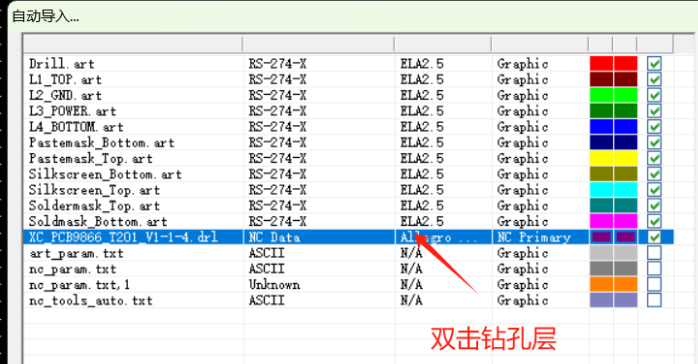

修改钻孔文件的数字格式

改成和art文件一样的数字格式。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删