解决:

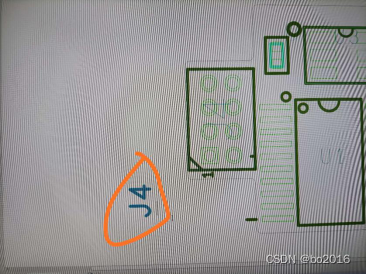

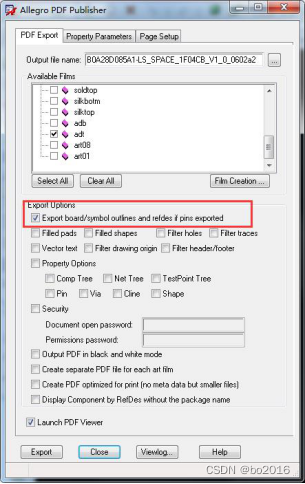

导出的时候什么都不要勾,只导adt或adb(因为上图那个J4有可能在ASSEMBY_TOP这个层面里)

上图这个勾勾 勾上了 就会导出ASSEMBY层的位号

解决:不影响,因为贴片是根据坐标和器件型号来贴的

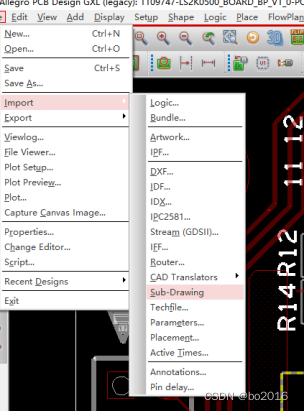

首先你的另外一块板必须有该器件,然后导sub drawing

然后指库,指到导出的目录,然后再到sub-drawing,选中那块板卡的丝印框和连接器和螺钉,一起导出,然后打开需要导入的板子,导入这个sub-drawing就行了

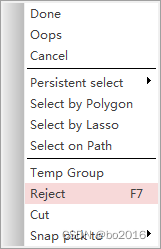

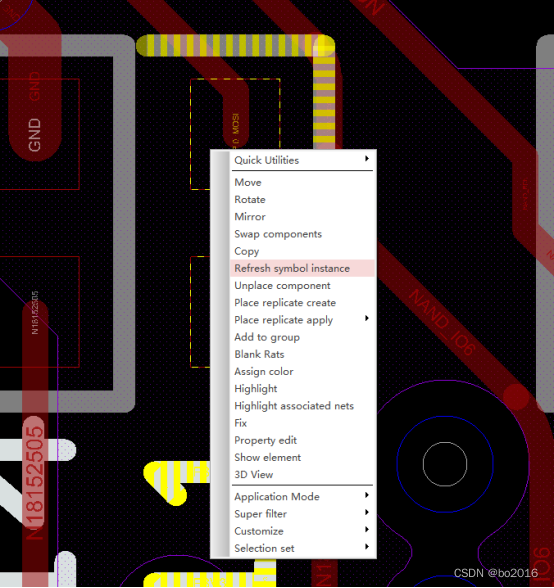

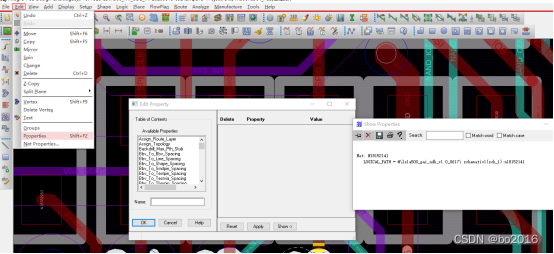

右键 点这个,先点Delete,然后右键,再点Reject

Edit-->Move,在Options中Rotation的Point选User Pick

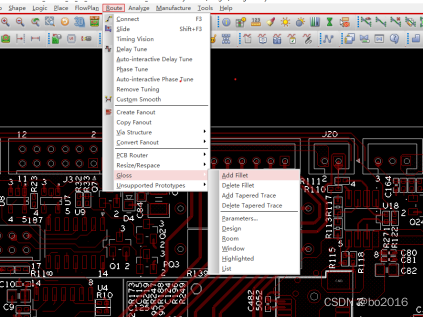

打开所有走线层,否则没有打开走线层就不会执行。执行命令route->gloss->add fillet

选择placementedit模式-->find all on--->点击所选器件--->右键rotate

Setup-->text sizes 打开相应的字体设置;在弹出的对话框中,输入相应的字体大小。(setup-->design-->parameter-->text-->setup text size)

改变字体大小:

Edit--->change,然后在右边的控制面板find tab里边只选text(只改变字体)然后在右边控制面板options tab 里 line width 舔线的宽度text block 里选字体的大小。

回到软件界面,通过菜单栏edit--->change,改变相应的字体。

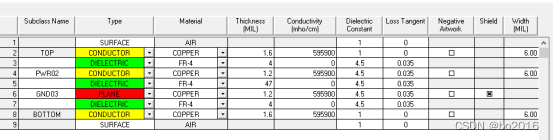

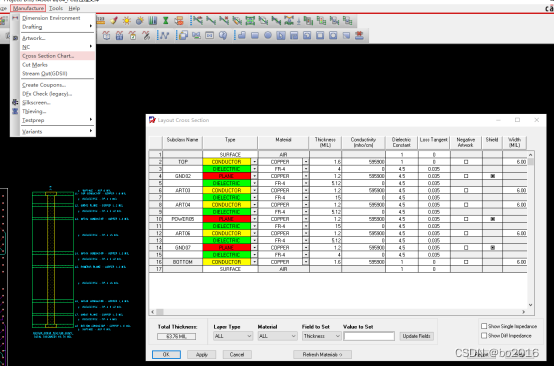

PLANE是平面、新建工程默认是2层,需要进入以上界面手动添加层数。

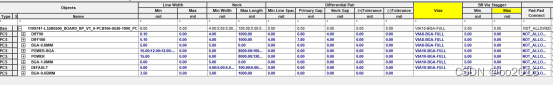

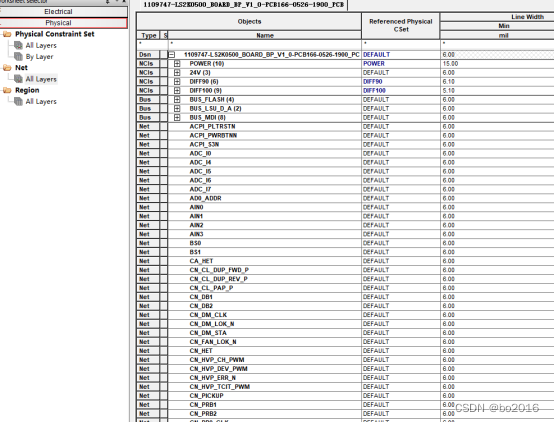

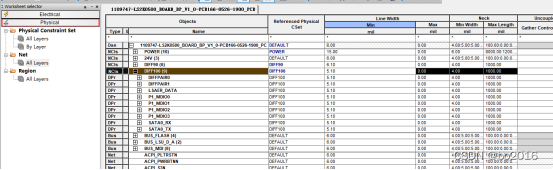

看哪些网络需要设置成差分100、电源等,默认都是DEFAULT.

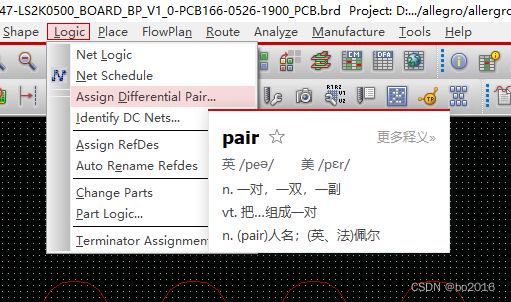

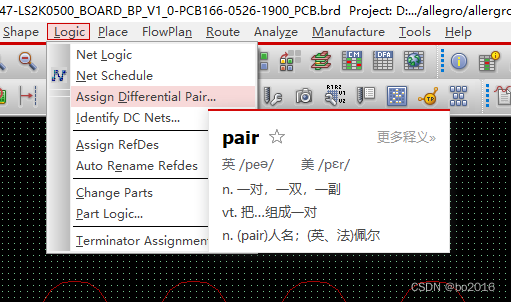

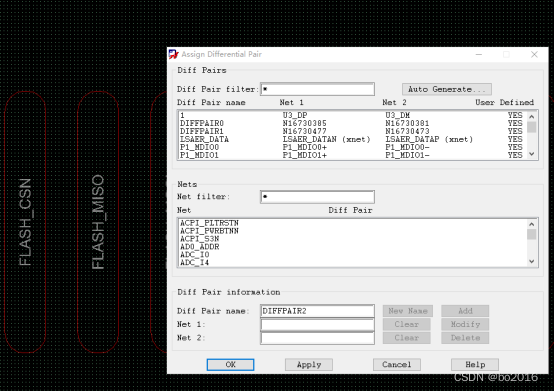

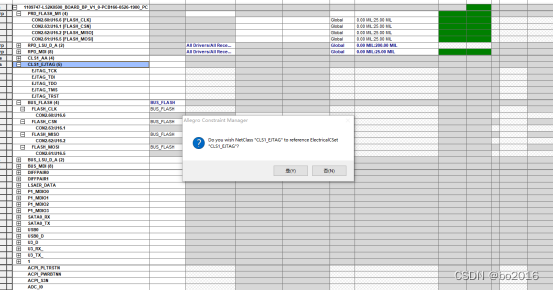

进入Assign Differential Pair 之后如下图界面,点击PCB上需要添加的网络,选中之后点击ADD

进入Assign Differential Pair 之后如下图界面,点击PCB上需要添加的网络,选中之后点击ADD

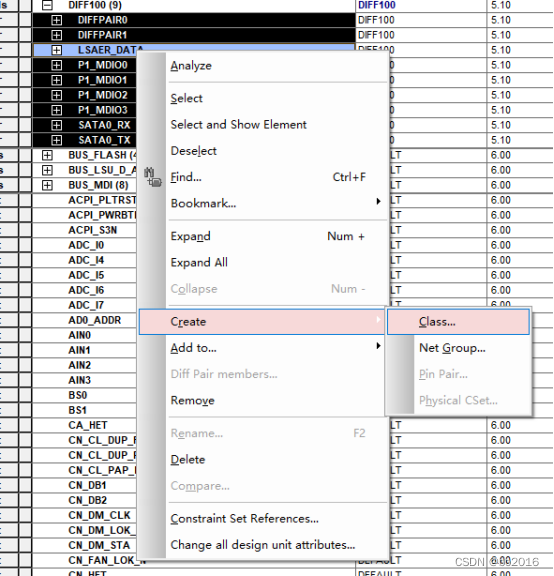

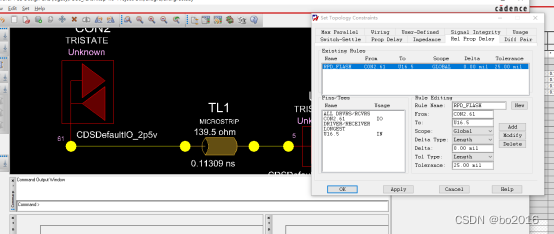

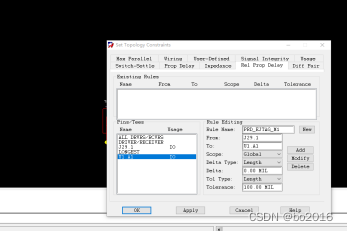

添加完差分对之后,默认是没有规则的,两个线是走在一起的,添加完之后需要在规则管理器网络里边,将所有相同差分规则、或阻抗的设置为1个CLASS,如下图所示

差分100创建完成之后,如下图所示,此时再走差分线,就不会走到一起了。

第一种等长的设置方法

最后add添加

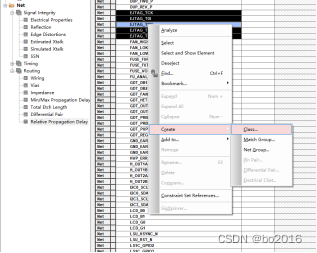

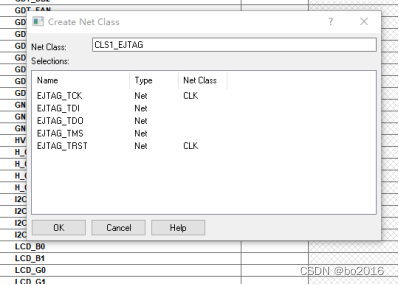

等长组添加,以EJTAG信号举例

第一步创建一个CLASS

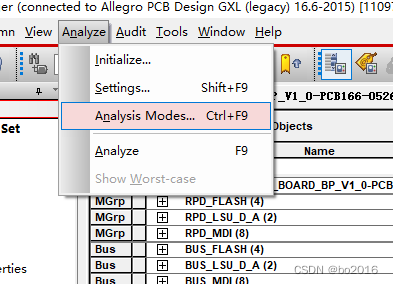

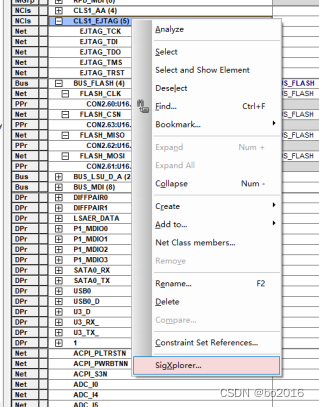

第二步进入SigXporer

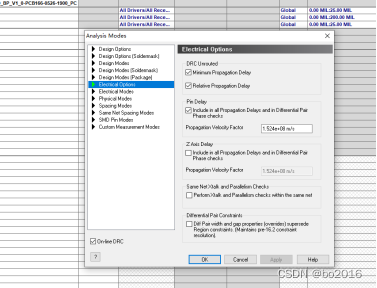

第三步设置ppr

第四步点击update CM回退到规则管理器

设置完成

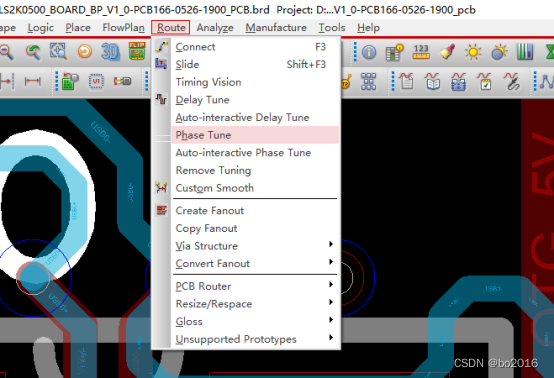

2、差分对内等长调整的功能

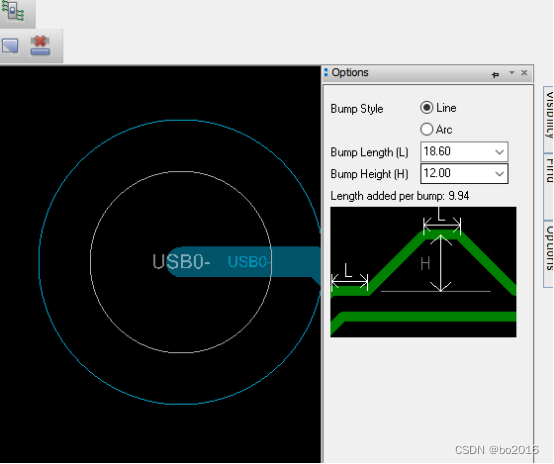

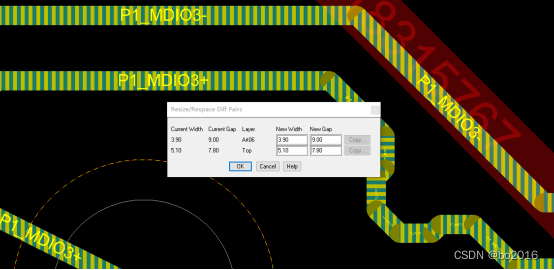

差分对等长2通常L的长度是3倍的线宽,下图Options可调整L和H

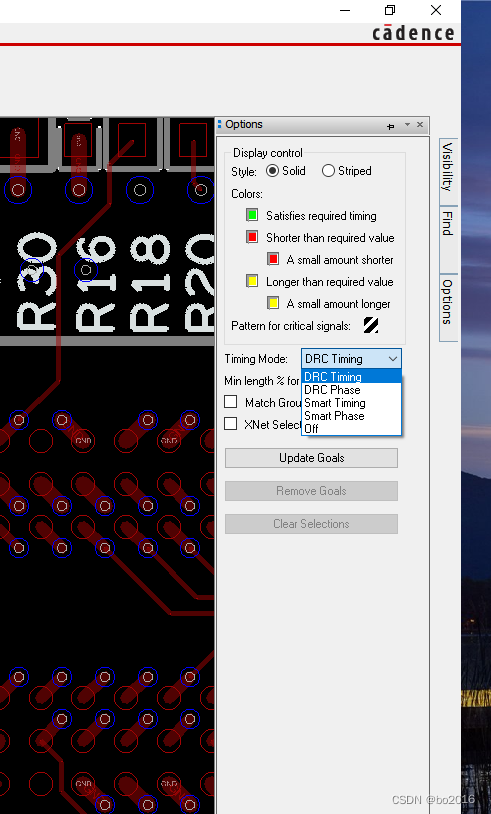

DRC Timing 针对单线等长的等长

DRC Phase 针对差分对等长

上图绿色表示等长全部是OK的,红色代表比基准线要短,黄线代表比基准线要长。

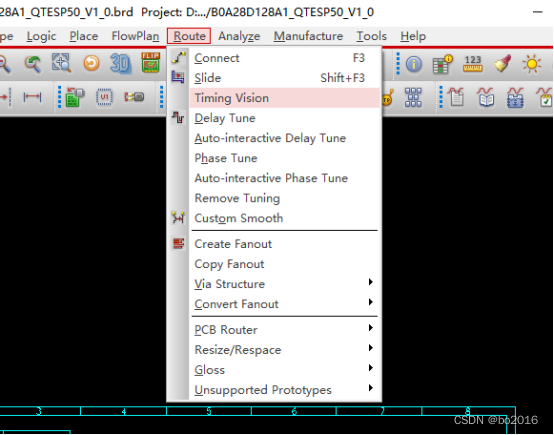

Route--timing Vision 可直观看是否等长,如果是红的把它拉长,黄的缩短。

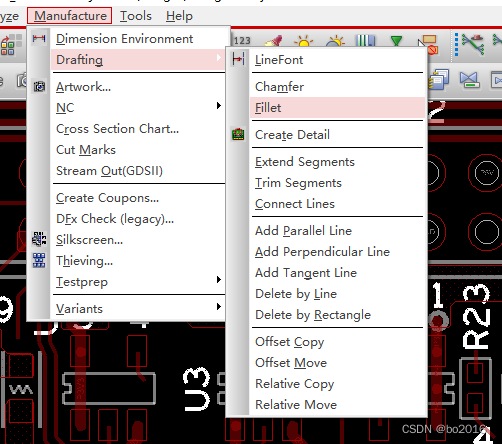

渐变线出线是为了让阻抗有一个渐变的过程,较小反射

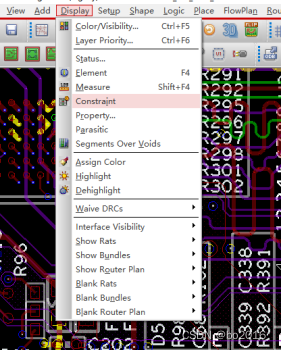

点击布局模式(placementedit)----(Options 中把Symbol选上)选中该元器件---右击

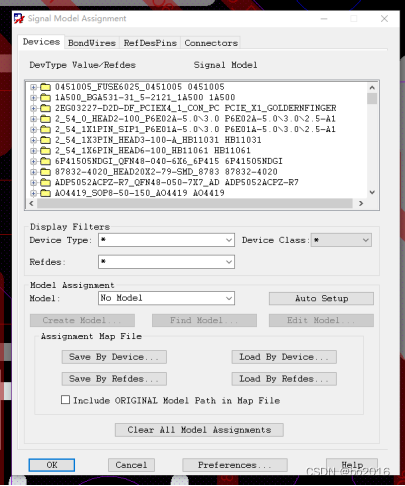

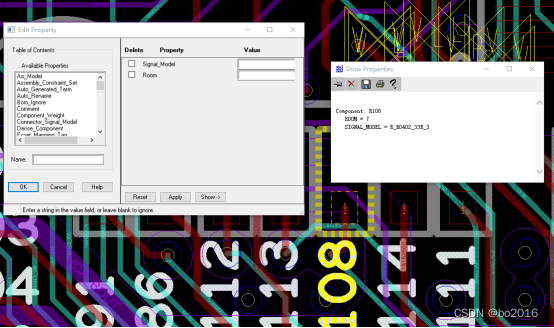

Signal Model--选择OK

点击OK--点击是,会出现下图界面

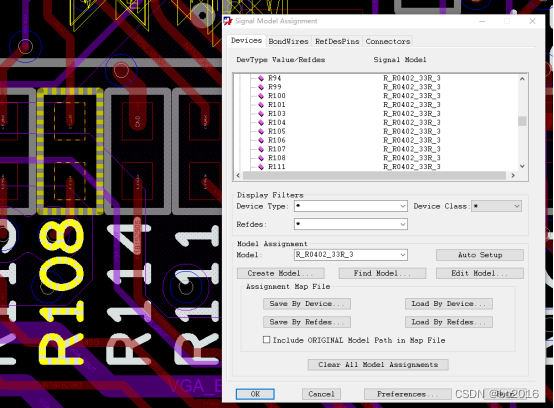

点击要赋模型的电阻,会出现下图界面

点击Create Model

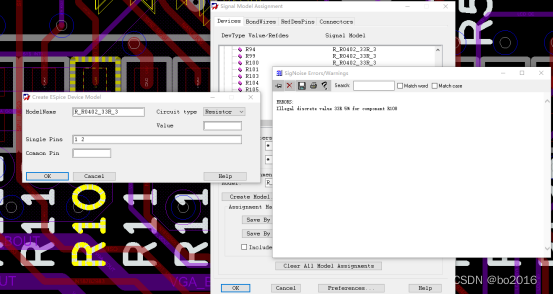

点击OK

上图Value值不做仿真的话,不用管 ,现在的目的是把电阻两端的网络关联起来,如果做仿真的话这个Value值一定要准确,,再点击OK,这个模型就赋好了。

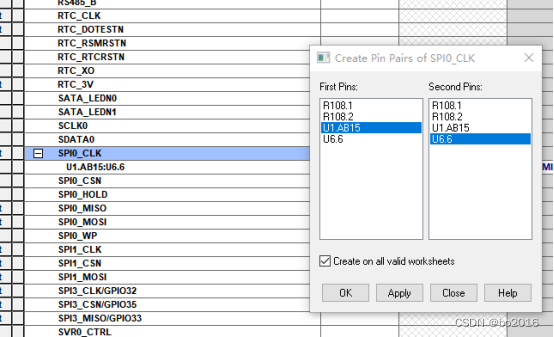

下一步道规则管理器中Electrical---Relative Propagation Delay中找到这个Xnet

再下一步Create--pin pair(创建pin pair) 就会跳过电阻

因为已经创建好一个

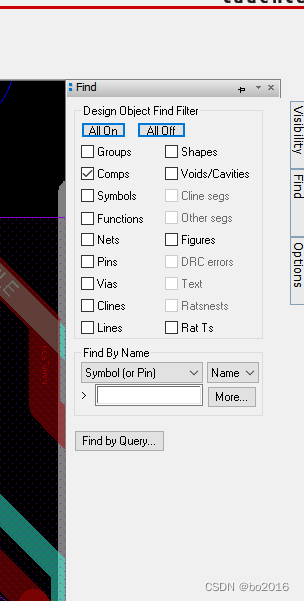

Find中选中Comps

再如上图点击之前创建模型的R108电阻,就会出现如上框图,将 该网络模型的VALUE值复制下来R_R0402_33R_3,之后退出,重新Edit--Property,框选所要赋模型的其他电阻如下图所示,选择Sigral Model 将刚才复制的填写道里边---Apply--OK,这样框选的其他所有器件都赋上模型了。

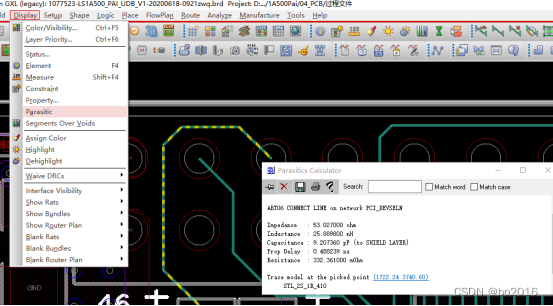

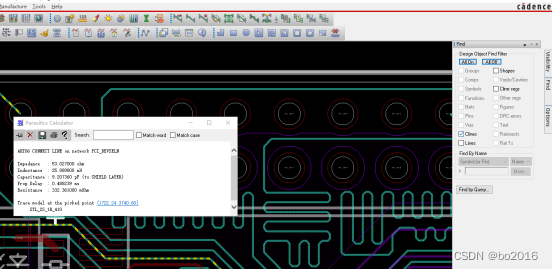

寄生参数的准确性取决于叠层设置的准确性.

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...