1.1. 层次化原理图基本概念

通常情况下,一个电路系统由许多小规模,逻辑清晰的电路组成。我们可以使用之前介绍的方法将这些小规模电路绘制在一张原理图上。

但系统复杂的大规模电路系统,我们往往将电路按照功能或者独立性分成许多子电路,每个子电路绘制在单独的原理图上。每页上的电路抽象为一个功能模块或者“元器件”,然后通过端口、跨页连接符等连接起来,形成完整的系统电路。

这样的设计方式便于多人协作,也能使系统结构更加清晰,降低出错的概率,加快设计进程。

1.2. 层次原理图基本构成和组成

Altium Designer 中的层次化原理图设计方法十分强大,我们可以将一个电路系统划分为若干个子系统,每个子系统可以划分为若干个功能模块,每个功能模块还可以分为许多更小的基本模块。而不同的电路系统之间也有可能有许多可以共用的基本模块,我们可以将这些模块提取成可以重复使用的模块电路。

下面是一个二级层次原理图的基本结构框架图:

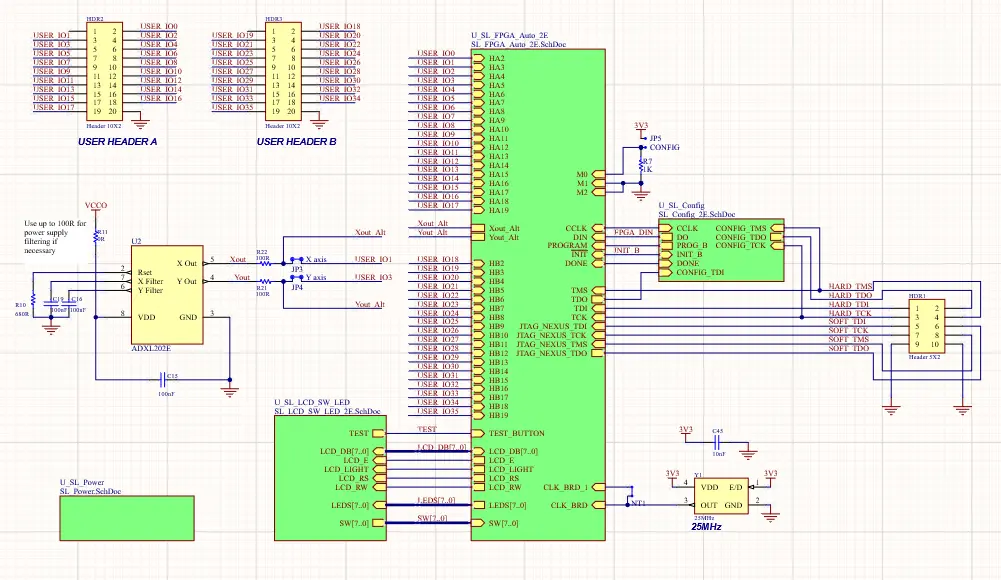

这个顶层原理图主要由5张图纸符号组成,每张图纸符号代表一个相应的子原理图文件,而其中有两个子原理图仍然由多个子模块组成。

1.3. 层次画原理图的设计方法

1) 自上而下的层次原理图设计

自上而下的设计方法:在绘制电路图之前,设计者应对项目整体有一个把握,把整个电路分为多个模块,确定每个模块的设计内容,然后对每个模块进行详细设计。这种方法适合设计者对电路模块划分比较清楚,有一定电路设计能力的设计人员。

A. 绘制顶层原理图

a) 执行“File”-“New”-“Project”-“Local Projects”,Project Name处命名为:自上而下层次练习.PrjPcb。

b) 执行“File”-“New”-“Schematic”,“Ctrl + S”保存,命名为:顶层-自上而下练习.SchDoc。设置原理图图纸参数。

c) 执行“Place”-“Sheet Symbol”,或者点击布线工具栏中的

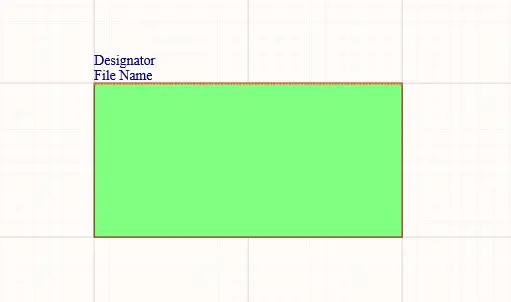

按钮,放置方块电路图。此时光标变成十字形并带有一个方块电路。

d) 移动光标到制定位置,单击鼠标确定方块电路的一个顶点,然后拖动鼠标,在合适位置再次点击鼠标左键确定方块电路的对角顶点。

此时,系统仍然处于绘制方块电路的状态,用同样的方法绘制另一个方块电路。绘制完成后,单击鼠标右键退出绘制状态。

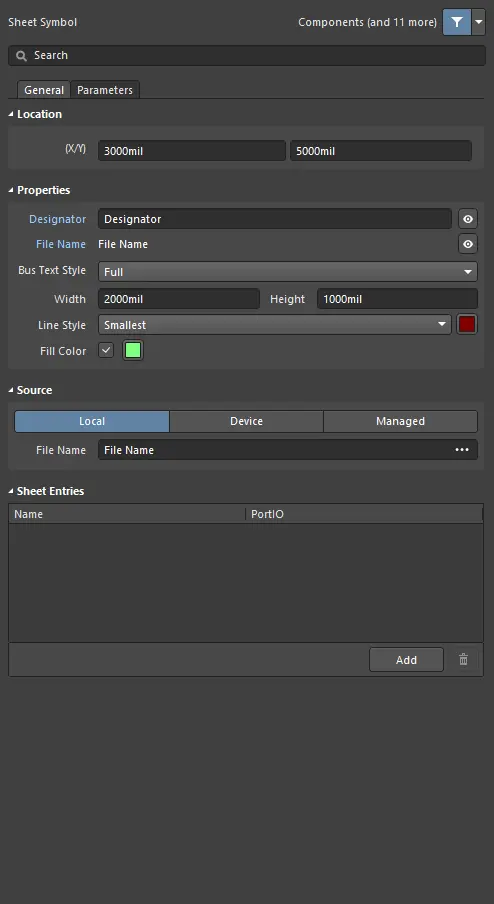

e) 双击绘制完成的方块电路,弹出方块电路属性设置面板,在该对话框中设置方块图属性。

下面是该属性面板的主要参数解释:

l Location(位置):方块电路左上角的坐标位置,我们可以指定和更改。

l Property(属性):

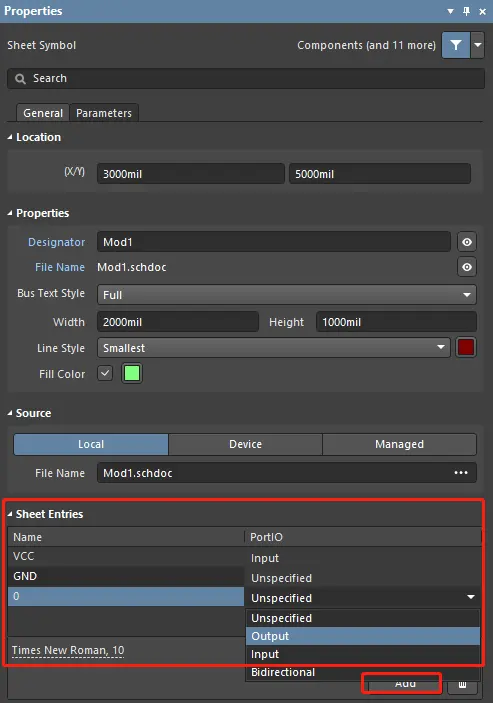

1. Designator(标识):设置方块电路的名称,我们设置为Mod1

2. File Name(文件名):设置该方块电路所代表的下层原理图的文件名。设置为Mod1.Schdoc

3. Width和Height用于设置方块电路的长度和宽度。

4. Line Style:设置方块电路边框的风格和颜色。

5. Fill Color:方块电路的填充颜色及是否透明(方框打勾)。

6. Sheet Entries(方块电路入口):设置图纸入口及属性。

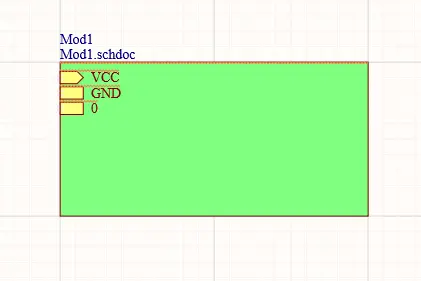

绘制完成后,方块电路出现黄色入口:

B. 绘制子原理图

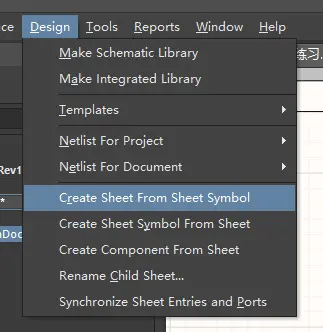

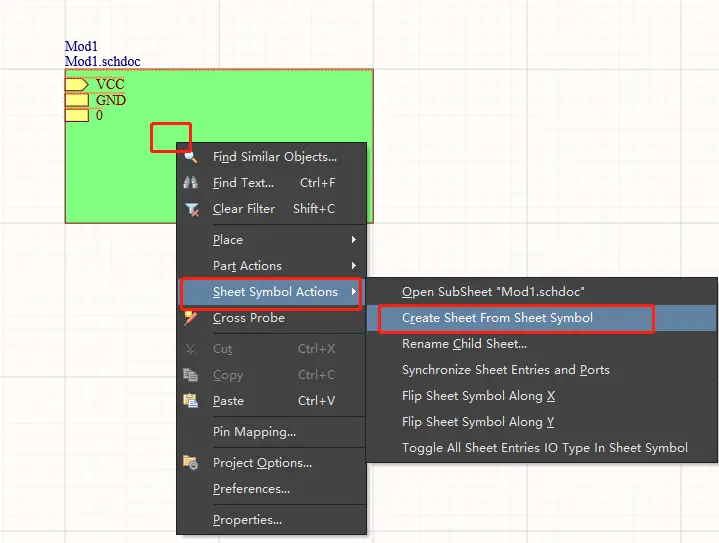

完成上一步后,我们可以在菜单栏“Design”-“Create Sheet From Sheet Symbol”,光标变成十字形。移动光标到方块电路内部空白处,单击鼠标右键。(也可以先将鼠标移动到方块电路上,右击,执行“Sheet Symbol Action”-“Create Sheet From Sheet Symbol”)。

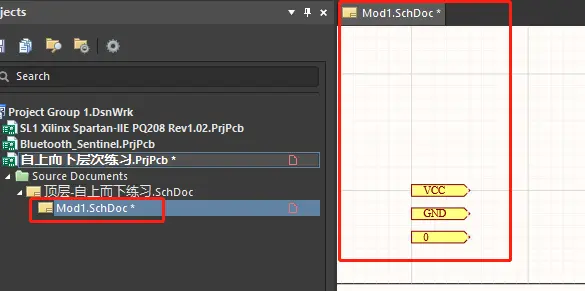

系统会自动生成一个与该方块电路同名的子原理图文件,并在原理图中生成3个与方块电路图对应的输入输出端口。

接下来我们就可以按照之前原理图基础设计方法设计这个子电路原理图了。

2) 自下而上的层次原理图设计

自下而上的设计方法:首先绘制各个子原理图,根据子原理图生成原理图符号,进而生成上层原理图,最后在顶层原理图进行连接。这种方法适用于对整体设计不是很熟悉的用户,比较适合初学者。

A. 绘制子原理图

a) 新建项目文件和电路原理图文件

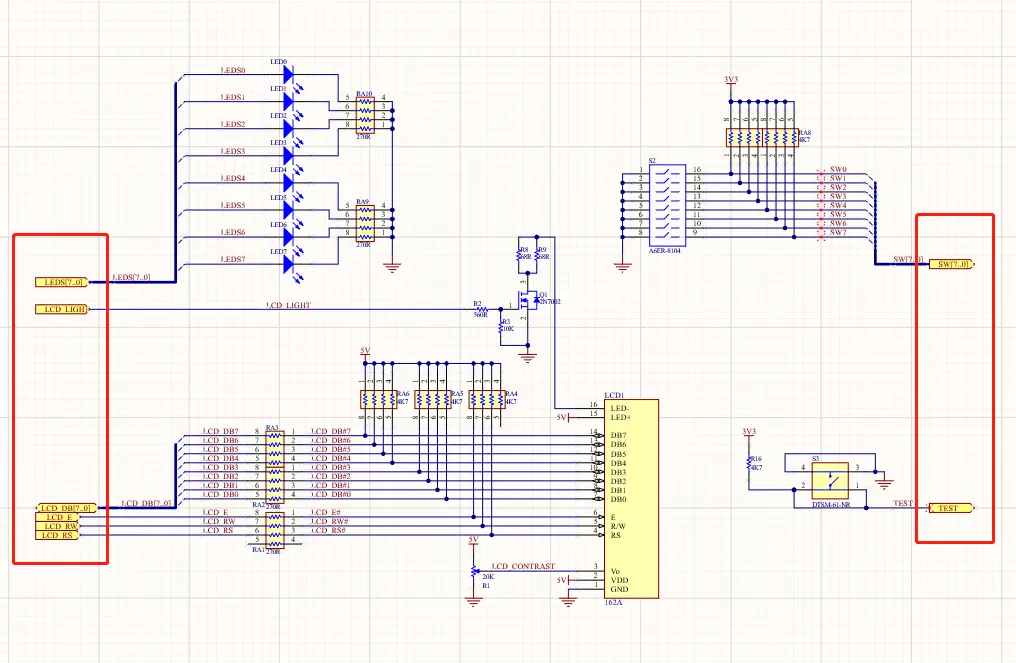

b) 根据功能电路模块绘制子原理图文件

c) 在子原理图中放置输入输出端口。

绘制完成后类似下图:

B. 绘制顶层原理图

a) 在项目中新建一个原理图文件,命名为对应:子原理图名_Modu1.schdoc。在之前的子原理图空白处右击选择“Sheet Actions”-“Create Sheet Symbol From Sheet”。弹出新的对话框:

选择要放置子原理图方块电路的顶层原理图文件,点击“OK”进行放置。

同样的方法可以将多个子电路图放置到顶层。直到完成设计。

1.4. 层次原理图的切换

1.4.1. 由顶层原理图切换到相应的子电路原理图

方法1:使用“Projects(项目)”面板,面板中直接点击对应的文件

方法2:使用“Navigation(导航)”面板,右击,Refesh刷新后,项目的层次化结构会显示出来。可以直接双击对应的文件名打开。

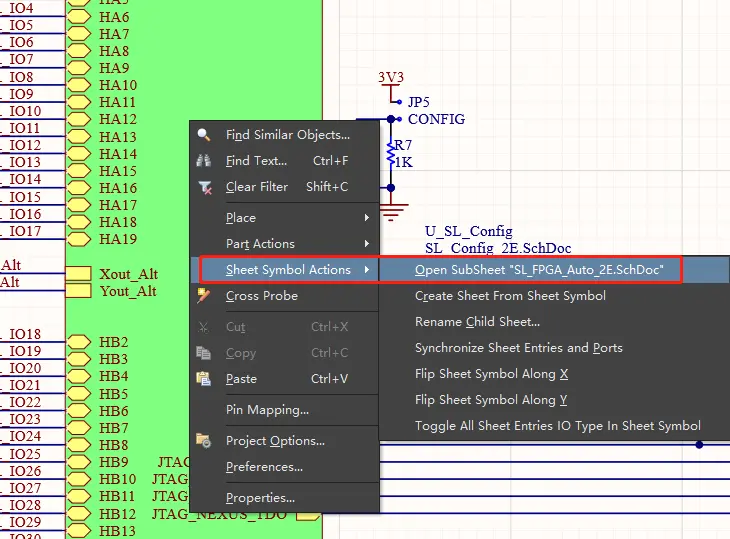

方法3:在顶层原理图的方框图上右击,选择“Open SubSheet xxx.SchDoc”

1.4.2. 由子原理图切换到顶层原理图

方法1:使用“Projects(项目)”面板,面板中直接点击对应的文件

方法2:使用“Navigation(导航)”面板,右击,Refesh刷新后,项目的层次化结构会显示出来。可以直接双击对应的文件名打开。

方法3:“Tools”-“Up/Down Hierarchy(上下层次)”命令,光标变成十字,移动光标到任意一个输入/输出端口处,单击,则对应的顶层原理图就会出现在编辑窗口中。并且被单击的输入/输出端口处于高亮显示状态。

1.5. 打印与报表输出

原理图设计完成后,经常需要将某些或者全部设计数据或图纸导出,并且生成报表打印。

1.5.1. 打印输出

Altium Designer可以将原理图打印输出,用于原理图浏览,交流。

打印之前首先进行页面设置。

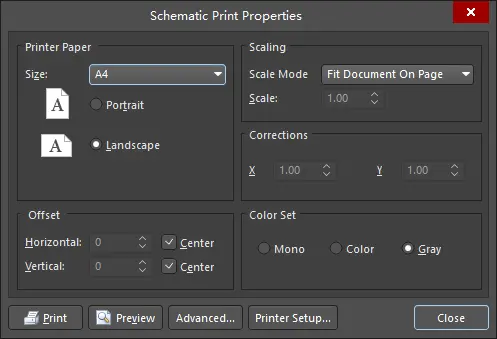

“File”-“Page Setup”,弹出对话框:

其中:

Printer Paper: 设置打印纸张栏

Size: 设置打印纸的尺寸

Portrait: 图纸竖直放置

Landscape:图纸横放

Scaling:缩放比例栏

可设置“Fit Document On Page(根据页面自动调整比例)”和“Scaled Print”,由用户自己定义比例大小。

Offset:页边偏移

设置水平页边距和垂直页边距。

Color Set:颜色设置栏

可设置:单色,彩色和灰色

点击“Preview”:可以预览打印效果。

点击“Printer Setup”:可以进行打印机设置

之后可以点击“Print”进行打印。

1.5.2. 网络表

Altium Designer的集成环境中,由原理图可以直接转换到PCB设计或仿真环境。但生成网络表可以便于交流。

彼此连接在一起的一组元器件引脚形成一个网络,若干网络组成完整电路。网络表就是对电路或者电路原理图的完整描述。其中包含:原理图中所有元器件的信息(包括元件标号,元件引脚和PCB封装等)和网络连接信息(包括网络名称、网络节点等)。

网表生成:原理图生成,文本编辑器手动编辑,从已经布线的PCB文件导出。

两种网络表类型: 基于单个原理图文件的网络表和基于整个项目的网络表。

A. 基于单个原理图文件的网络表

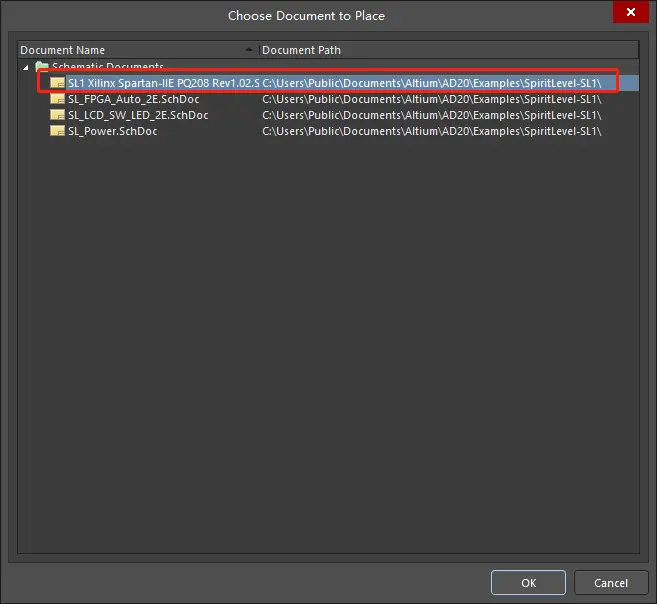

下面我们以AD自带的实例:“Xilinx Spartan-IIE PQ208 Rev1.02.PrjPcb”中的的原理图文件“SL_FPGA_Auto_2E.SchDoc”为例介绍基于单个原理图文件的网络表的创建。

打开目标原理图文件。

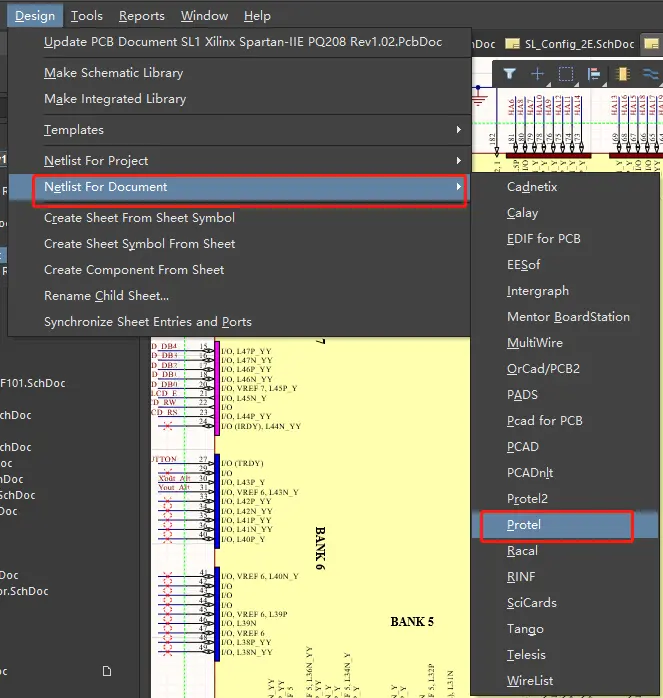

“Design”-“Netlist For Document”-要使用网络表的软件(比如Protel)

在项目面板“Generated/Netlist Files”中,系统生成了当前原理图的网络表“SL_FPGA_Auto_2E.NET”

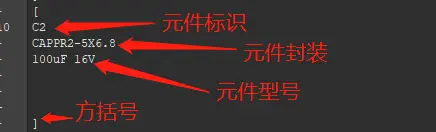

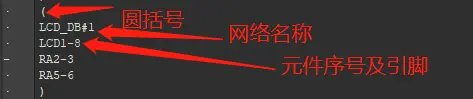

该网络表分为两大部分,一部分是元件信息,一部分是网络信息。

元件信息用方括号分隔,由元件的标识、封装形式、型号、数值等组成。

网络信息用圆括号分隔,由网络名称和网络中所有具有电气连接关系的元件引脚组成。

元件信息

网络信息

B. 基于整个项目的网络表

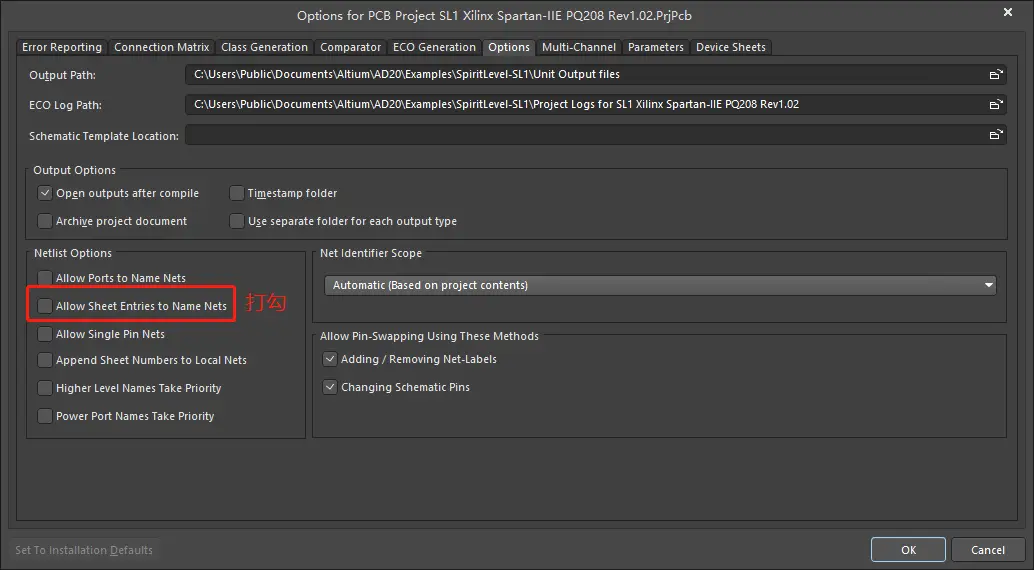

创建网络表前,对项目进行简单的设置。

在项目名称处右击,选择“Project Options”,在弹出的对话框处选择“Options”

“Output Path(输出路径)”:设置各种报表的输出路径

“ECO日志路径”:设置ECO Log文件的输出路径。

“Output Options(输出选项)”:设置网络表的网络表的输出选项。

“Netlist Options(网络表选项)”:设置创建网络表的条件。

打开目标项目。

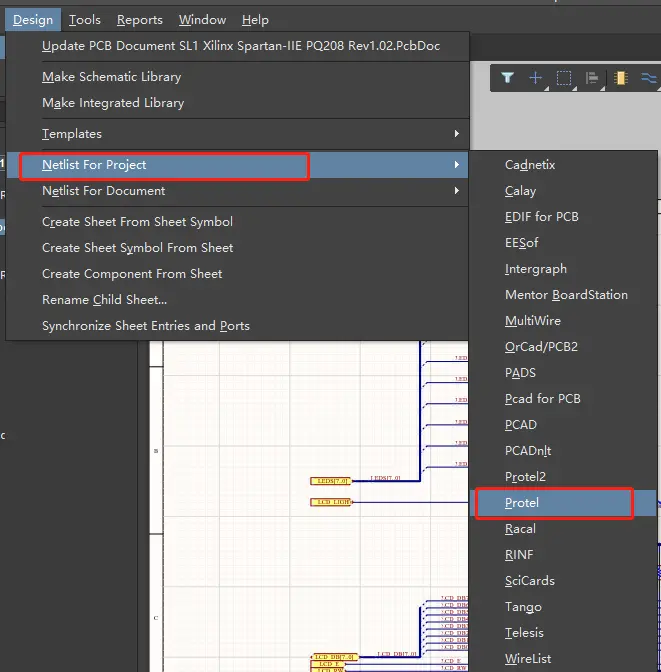

“Design”-“Netlist For Project”-要使用网络表的软件(比如Protel)

其他步骤和上一步,但原理图生成网络表一样。

1.5.3. 元器件报表(BOM)

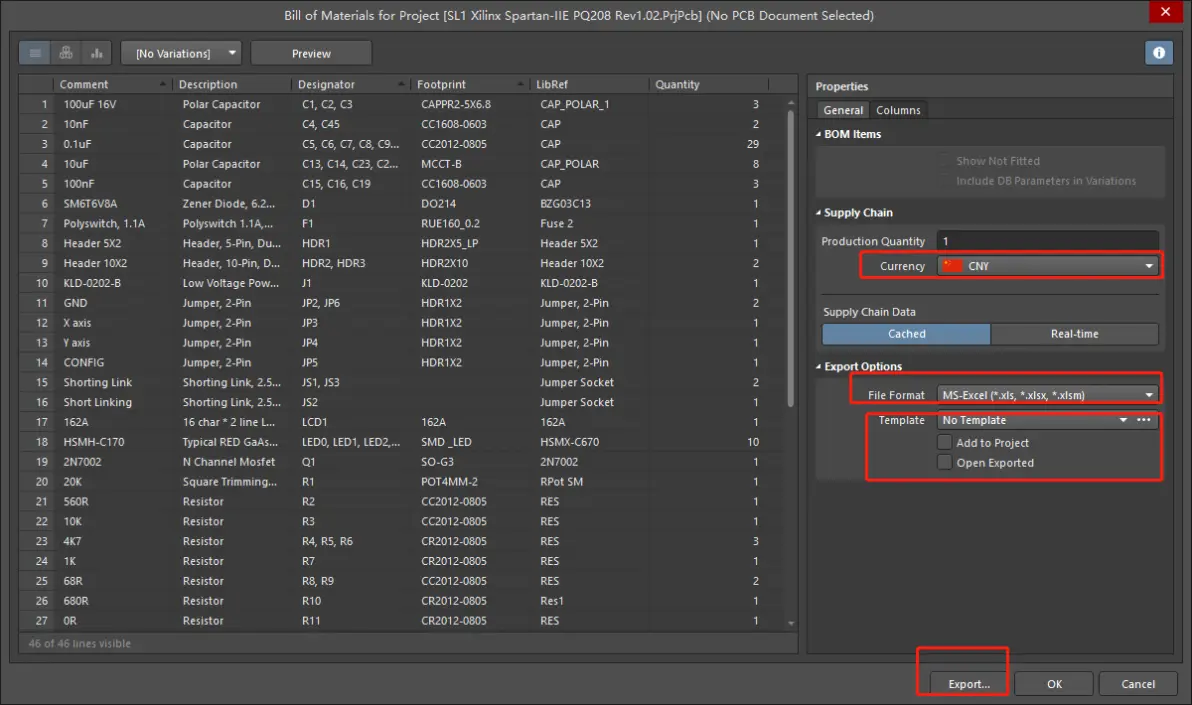

初级生成元器件报表的方式可以直接使用菜单栏的“Reports”-“Bill of Materials”。

可以设置导出元件表的格式,使用的模板。

这个可以参考我的视频: https://www.bilibili.com/video/BV14r4y1K73B/

尤其应该学习自己定义模板,按照指定的模板生成BOM。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。