Altium designer 20已就绪,AD20新功能详解

据美通社消息,2019年12月3日,Altium正式推出了新版pcb设计软件 ——Altium Designer 20。 据悉新的版本将进一步节省布线时间。“Altium Designer 20 改变了PCB设计”,Altium首席技术官Sergey Kostinsky说:“此版本的高级功能使得任何类型,无论是简单还是复杂的电路板设计都变得更加有效率。”

官方也对更多的升级细节做出了解释,为大家罗列Altium Designer 20 的新功能。

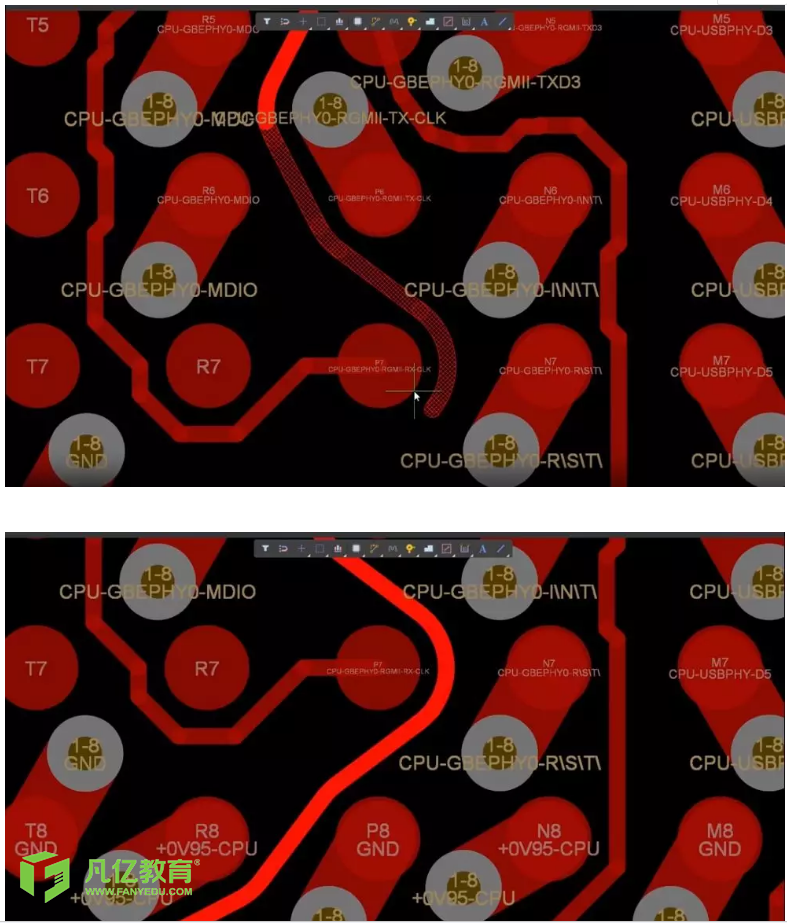

任意角度布线

在高密度板上绕开障碍物进行专业操作,并且深入到您的BGA中走线,从而无需额外的信号层。借助智能避障算法,您可以使用切向弧避开障碍物,从而最有效地利用您的电路板空间。

如上图正在走的这根高亮红色线,它从BGA密集的管脚阵列中左冲右突,游刃有余,就像赵子龙在长坂坡七进七出救少主,如入无人之境!

就是这么任性!

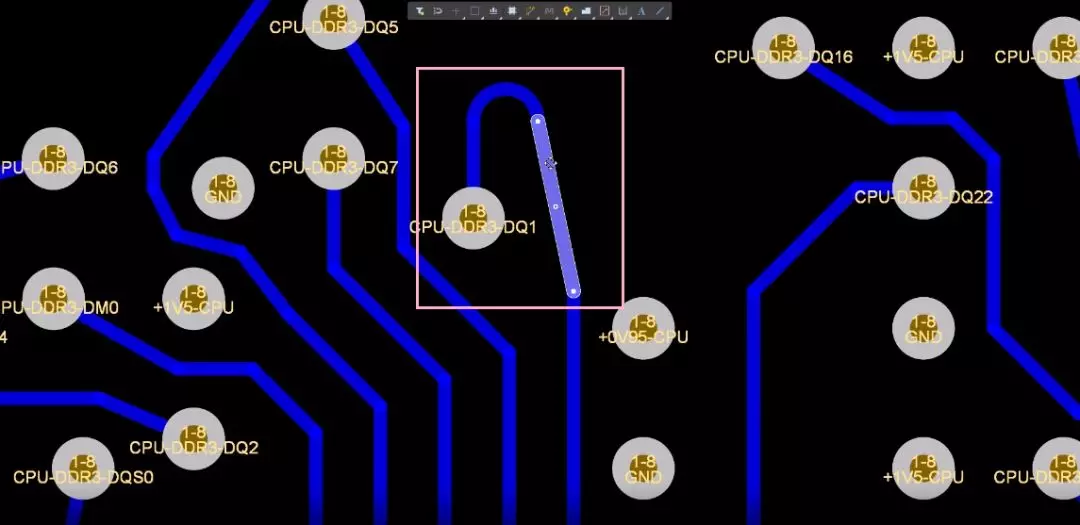

不光走线的过程中可以任性地以任意角度走线,自动使用切线和弧线在走线过程中遵守规则保持安全间距,对于之前已经走好的折来折去不够机动灵活的走线可以一键修正。如下图。

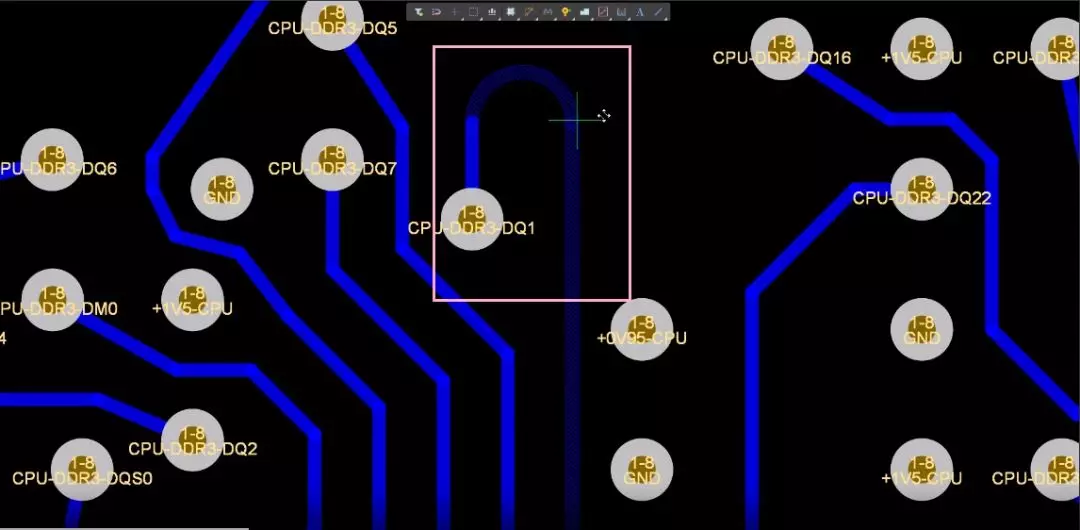

先将之前走好需要修整的线选中,然后点一下命令,结果如下图,超赞!

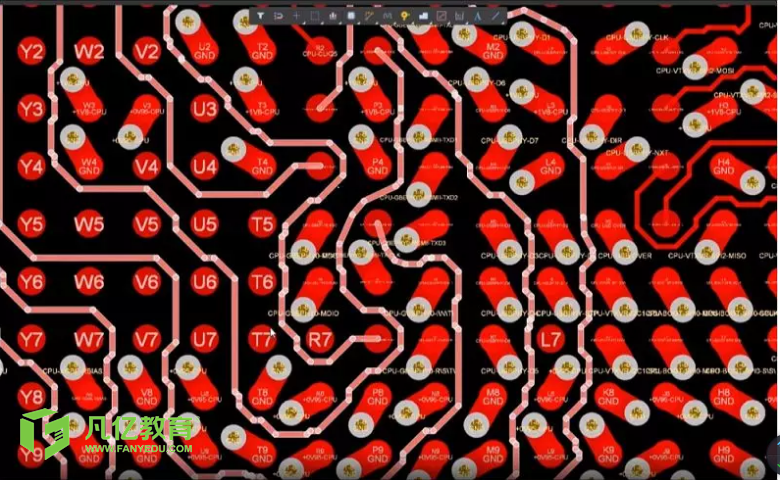

走线的平滑处理

对走线进行编辑以改善信号完整性是很耗费时间的,尤其是当您必须对单个弧线以及蛇形调整线进行编辑的时候。 这就是为什么Altium Designer 20合并了新的布线优化引擎和高级的推挤功能以帮助加快该过程,从而提高生产率的原因。

比如上图框框内是想处理的走线,只需要点击要处理的那一段,然后鼠标一拖。如下图。

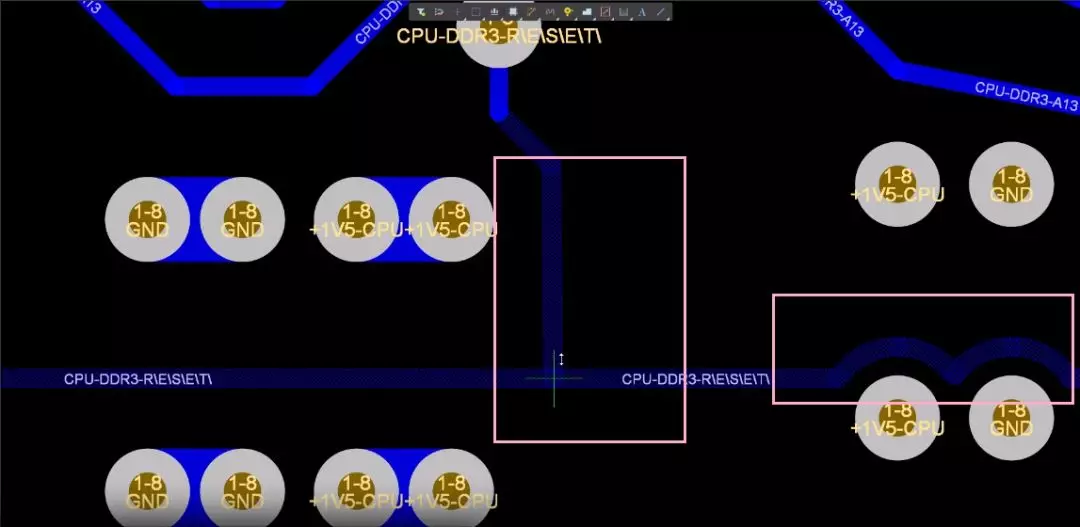

在修整走线的时候还可以推挤,如下图所示,想要把框框内的一截线拉长些,又不影响其连接。

推挤的过程中会实时处理,遇到障碍物能推挤就推挤,不能推挤惹不起的躲得起,自己闪避。

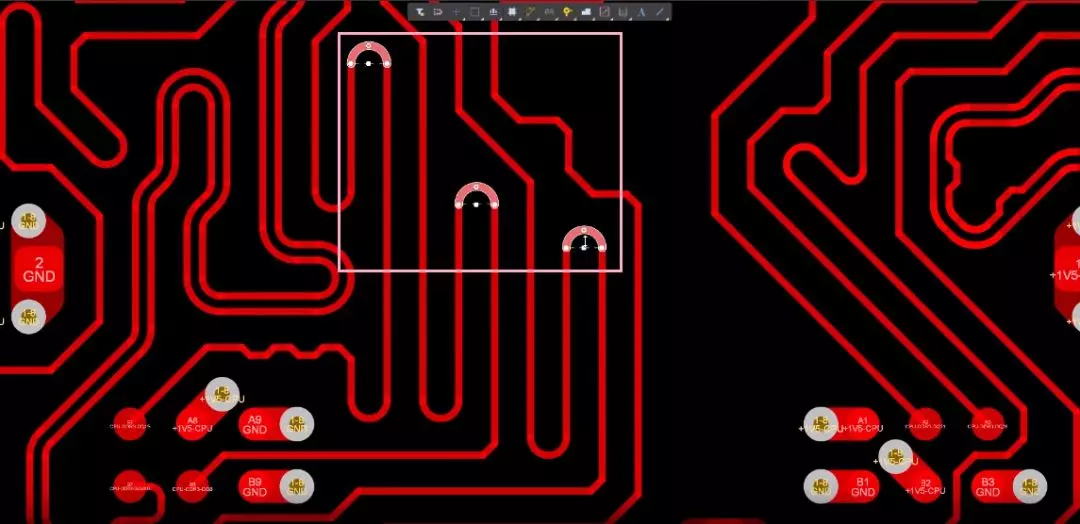

还可以对多根线同时修整处理。如下图,选取三段圆弧线。

对它们上下移动的过程中,同时推挤。

新的原理图增强

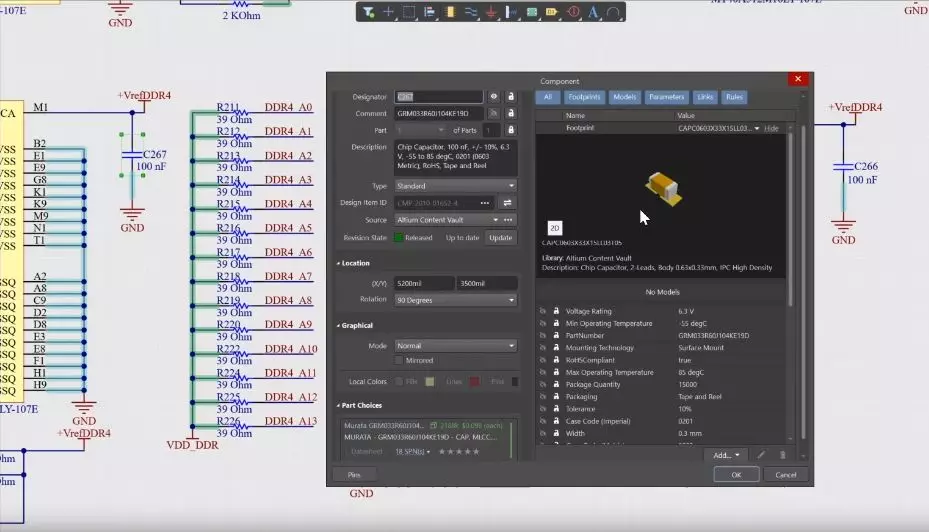

Altium Designer在其原理图编辑器上进行了改进,引入了新的DirectX引擎,即时编译功能以及更加简化的交互式属性面板。

原理图动态数据模型。不必要的大型原理图重新编译会占用大量时间。这就是为什么 Altium Designer 要使用新的动态数据模型,该模型可以在后台进行增量和连续编译,而无需执行完整的设计编译。

原理图视觉效果增强。Altium Designer 中的 DirectX 可以为您带来流畅,快速的原理图体验。这种新的实现方式可以平滑缩放,平移甚至极大地加快了复制和粘贴功能的速度。

重新设计的交互式属性面板。该交互式属性面板更加简化并且界面友好。通过更新的属性面板可以完全清晰地操控设计对象和功能。实时查看相关属性,供应商信息,甚至生命周期信息。

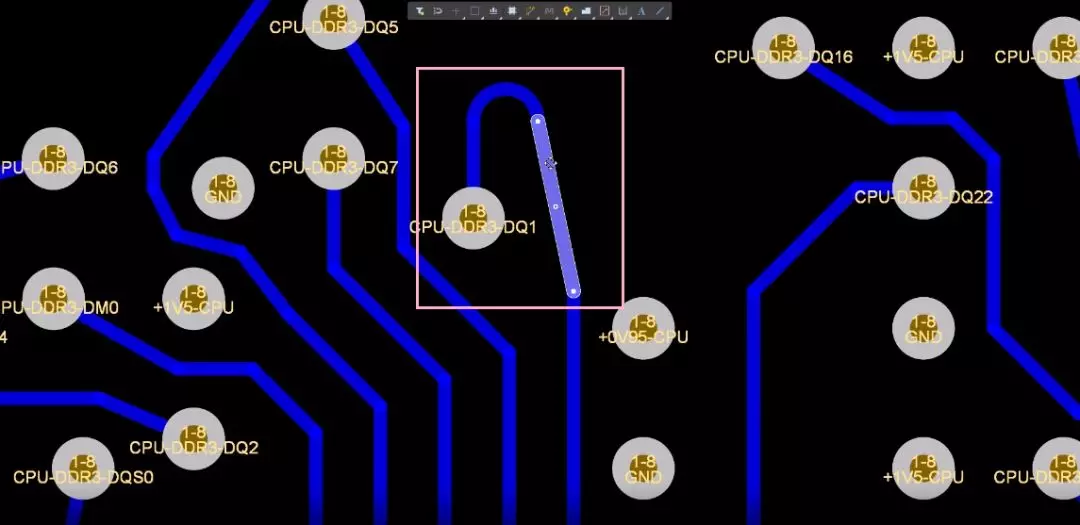

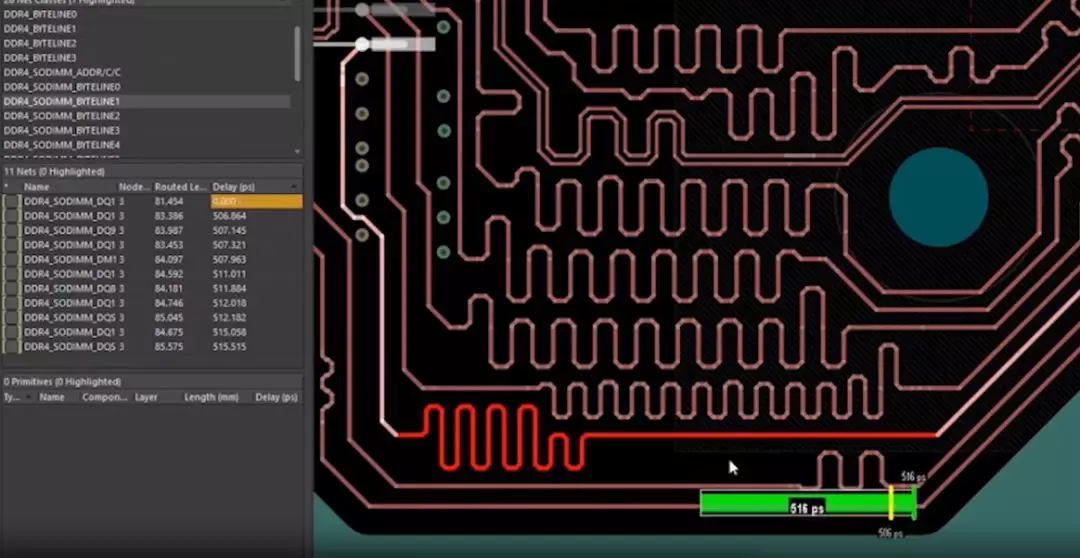

基于时间的长度匹配

高速数字电路取决于准时到达的信号和数据。 如果走线调整不当,飞行时间会有所变化,并且数据错误可能会很多。Altium Designer 20计算走线上的传播时间,并为高速数字信号提供同步的飞行时间。

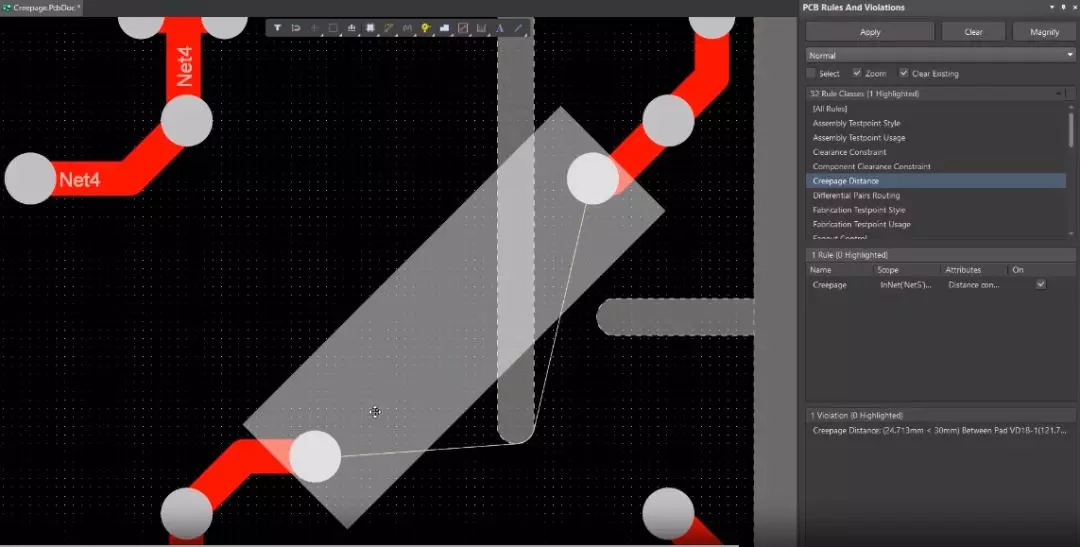

爬电电压规则

在高电压电路中,爬电是一个问题,会引起泄漏电流,从而危害您的设计。 Altium Designer 20具有可以帮助您避免爬电带来影响的新功能。

爬电是什么玩意?

几乎所有PCB设计软件工具都将所有间隔通称为间距Clearance。实际上一切在绝缘表面上的导电对象之间应用的间距,比如焊盘到焊盘,焊盘到导线,导线到导线的间隔参数,都是爬电距离,而不是我们常说的间距。通过空气在导电元件之间的间隔才是间距。毫无疑问,通用术语“间距规则(Clearance)” 将继续用于工程师的设计和EDA工具中,作为我们通常意义下的间距(不管它到底是爬电距离creepage还是间距Clearance)。但是,在高电压电路应用的场合,爬电距离和传统意义的间距还是有很大差异的,这个是设计师需要特别注意的地方。一般来说,爬电要求总是大于或等于相关的间距要求。

在有限空间中实现混合技术设计的高压间距规则有一套当前标准。根据IEC60950标准的定义:

PCB 间距(Clearance) :通过空气测量的两个导电对象之间或导电部件和设备的边界表面之间的最短路径。也是我们常见并常用的间距。

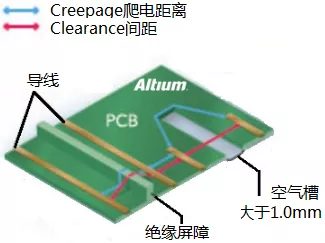

爬电距离(Creepage): 通过沿着绝缘材料表面测量的两个导电对象之间的最短路径。如下图所示。

如下图为包含有绝缘屏障或电路板上加开空气槽的PCB设计例子,更能清楚明了地了解爬电距离和间距的不同。

如何解决间距不足的问题间距是在空气(视线)中测量的,因此在布局层面可以做到合理布局,以减少所需的间距。通过使用绝缘材料并且在可能的情况下通过双侧组装可以实现间隔的显着减小。绝缘材料可以是高压节点之间的片状屏障。由于高的部件是表面安装的,可以将需要间距的电路放置在板的相对侧上。处于相同电位的相同高电压电路内的节点通常需要注意与低电压电路间距。一种好的方法是在电路板的顶部放置高压电路,在底部放置低压电路,用于控制和监测。低压电路通常不具有高压电路所所需的边界表面(壳体)爬电要求。

如何解决爬电距离不足的问题我们知道,爬电距离是绝缘表面上的电节点之间的间隔。在我们的讨论中,这意味着PCB表面或内部层上的导体之间的空间。但是进一步扩展元件将受到产品包装体积的约束,因此需要有一些其他策略,在允许更高的封装密度情况下,同时满足所需的爬电距离。

上图显示了用以增加爬电距离的各种情况

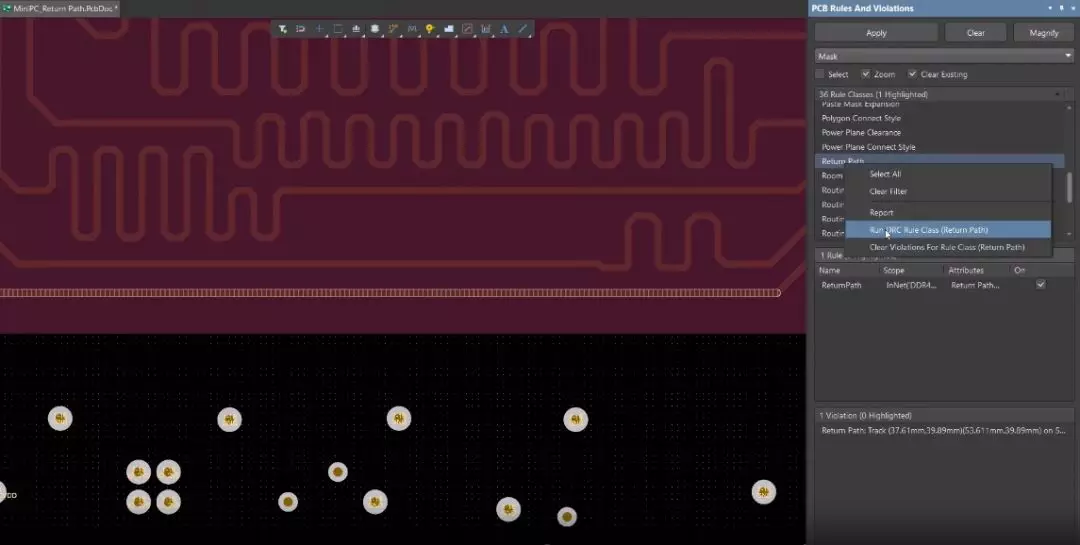

返回路径检查除非提供适当的返回路径,否则高速信号会产生电磁场,这可能导致串扰,数据错误或辐射干扰。 正确的返回路径可使噪声电流通过非常低的阻抗返回到地,从而消除了这些问题。 Altium Designer 20将监视返回路径并检查所有参考多边形的返回路径完整性,因此无需手动执行此操作。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...