DRC检查是依据自行设置的规则进行的。例如自己设置的最小间距是8mil,那么实际PCB中,出现小于6mil的间距就会报错。

并不是DRC有错误的板子就不能使用,例如丝印的错误不会影响电气属性。接下来简单分析几种常见的错误。

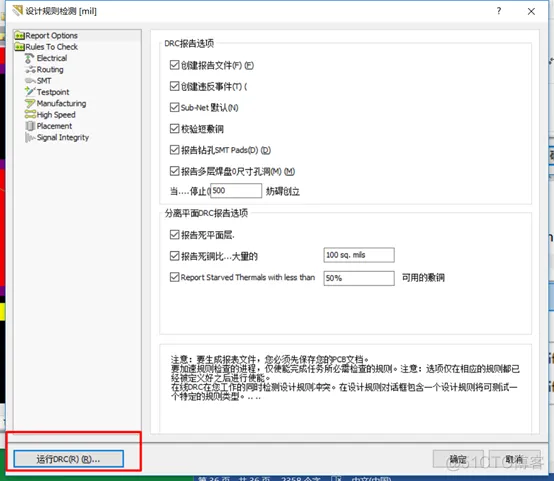

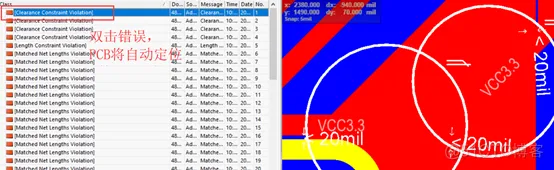

运行DRC以后,会弹出一个页面和message。只看Message,双击message可以快速定位错误。

错误类型

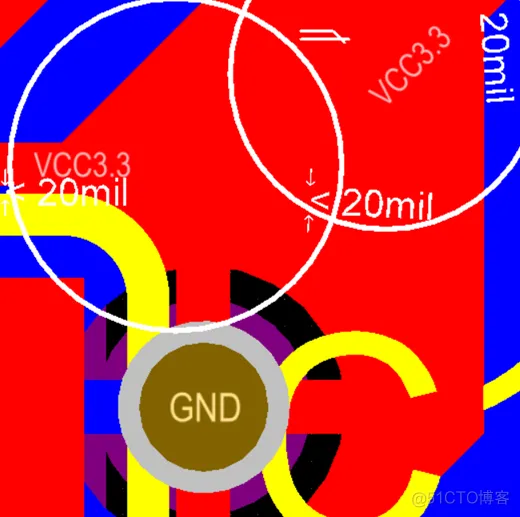

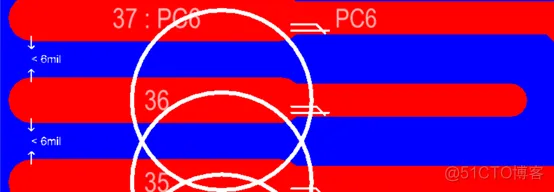

[Clearance Constraint Violation]

间隙约束违规,一般是敷铜的网络会设置间隙约束,例如网络属性为VCC3.3的导线和GND的敷铜连在了一起,其实只要间隙小于规定值例如20mil,就会报错。

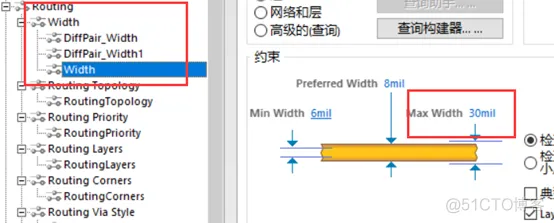

问题 [Width Constraint Violation]

宽度约束违规

这根线的宽度是40mil

但是定义的线宽最大为30mil

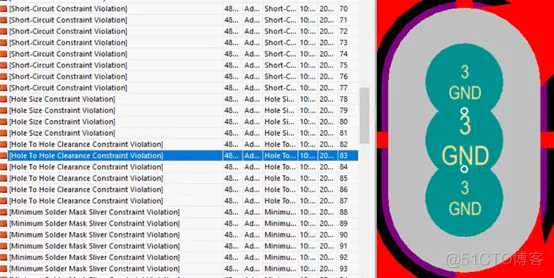

[Short-Circuit Constraint Violation]

短路,不同的网络被强行接在一起。

Hole Size Constraint Violation]

过孔大小不合适

Hole To Hole Clearance Constraint Violation

孔和孔接到一块了

以下是网络上的一些

1.Rule Violations Count

违反数

2.Short-Circuit Constraint (Allowed=No) (All),(All)

短路约束=不允许)(全部),(全部)

3.Un-Routed Net Constraint ( (All) ) 26

Un-Routed净约束(所有)26岁

4.Clearance Constraint (Gap=9mil) (All),(All)

间隙约束(间隙= 9 mil)(全部),(全部)

5.Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (Conductor Width=10mil) (Air Gap=10mil) (Entries=4) (All)

功率平面连接规则(救济连接)(扩展= 20 mil)(导体宽= 10 mil)(气隙= 10 mil)(条目= 4)(全部)0

6.Width Constraint (Min=8mil) (Max=20mil) (Preferred=15mil) (All)

宽度约束(Min = 8 mil)( Max= 20 mil)(优先15例mil)(全部)

问题应该出在你设置和实际的冲突,你的Protel所设置的最小线宽是25mil,最大线宽也是25mil,默认线宽还是25mil,这本没错,但可能是你的某根GND线不是25mil,或者你用了覆铜,而覆铜的线条(Track Width)也不是25mil,所以才出错!建议在Design 的Rule里设置一下Width Constraint的最大和最小线宽,调整到合适范围,就不会报错了。

7.Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)

高度约束(Min = 0 mil)( Max = 1000 mil)(优先= 500 mil)(全部)

8.Hole Size Constraint (Min=1mil) (Max=150mil) (All)

孔尺寸约束(Min = 1 mil)( Max = 150 mil)(全部)

修改尺寸,设计孔大于你设置的规则的值

9.Hole To Hole Clearance (Gap=6mil) (All),(All)

洞孔间隙(间隙= 6 mil)(全部),(全部)

引脚安全间距问题,一般是封装的问题,如果确定封装没问题,这个错误基本你可以忽略。

10.Minimum Solder Mask Sliver (Gap=1mil) (All),(All)

最低焊接面罩银(间隙= 1 mil)(全部),(全部)

你的某个元件的焊盘间距 大于1mil,你可以选择该规则或者把封装中的焊盘间距改大一点。

11.Silkscreen Over Component Pads (Clearance=1mil) (All),(All)

丝网印刷在组件垫(许可= 1 mil)(全部),(全部)

顶层丝印与元件焊盘距离近(小于1mil)

按D、R将规则中的Silkscreen Over Component Pads 改小一些就可以了

12.Silk to Silk (Clearance=1mil) (All),(All)

丝印丝印(间隙= 1 mil)(全部),(全部)

两个丝印之间的距离太近,这个错误可以忽略

13.Net Antennae (Tolerance=0mil) (All)

网络天线(耐受= 0 mil)(全部)

14.Clearance Constraint (Gap=6mil) (InComponent(U1)),(All)

间隙约束(间隙= 6 mil)(InComponent(U1)),(所有)

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。