摘要:

电感是诸如低噪声放大器、功率放大器、滤波器、振荡器、阻抗匹配网络以及 DCDC 转换器等模拟、射频和微波电路中的重要元件之一。应用中需要电感具有高品质因数和自谐振频率,有限的寄生耦合,占用更小面积以及易于版图实现和制造。近年来,三维集成电路设计和制造技术得到了很大的发展。硅通孔(Through-Silicon-Via,TSV)是实现三维多层芯片堆叠的关键技术,它可以为多层芯片在垂直方向提供高深宽比的互连。利用 TSV 和再分布层(Redistribution Layer, RDL)金属实现三维结构的螺旋电感是一种新的选择,它可以利用芯片的垂直方向,占用较小芯片面积以取得更高的电感密度。本文基于 TSV 的三维集成电感的结构特点和主要结构参数,利用电磁仿真软件 ANSYS HFSS,研究分析了各工艺参数和设计参数对集成电感的感值、品质因数以及自谐振频率等的影响,为三维集成电感的设计和应用提供指导。

关键字:ANSYS HFSS、三维集成电感、仿真、Q因子、电感值

1、三维集成电感结构和参数

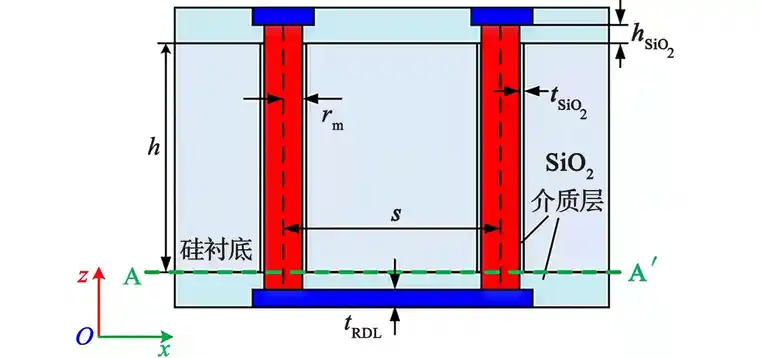

图 1.1(a)和(b)分别是三维集成电感的主视图和侧视图。基于 TSV 的三维集成电感的螺旋导体结构由硅通孔(TSV)和金属再分布层(RDL)构成,形似螺线管,线圈中间添加介质,从而实现可以储存磁能的电感器。图中可以看出,匝数为 N的三维集成电感包含 2N 个 TSV,它们排列成一个 N 行 2 列的矩形矩阵;每一段衬底下层的 RDL 金属连接同一行的两个 TSV,而每一段衬底上层的 RDL 金属连接相邻行不同列的两个 TSV,此外,电感的输入输出端口都在衬底上层 RDL。

(a) 主视图

(b) 侧视图

图1.1 三维集成电感截面图和俯视图

基于 TSV 的三维集成电感的电感值和性能由工艺参数和设计参数决定,工艺参数取决于采用的工艺制程,包括 TSV 的尺寸参数和 RDL 金属的尺寸参数。在设计三维集成电感时,可以通过调整设计参数来得到特定电感值和特定面积的电感,设计参数包括电感匝数、TSV 排列的距离等。三维集成电感中的 TSV 呈矩阵形式分布,所有参数都在图1.1中进行了标注。如下表1介绍了三维集成电感的工艺参数与设计参数及其取值大小。

2、三维集成电感等效电路模型

电感的单π型等效电路,其中 Cline 为电感金属线之间的寄生电容,R0 和 L0 分别为金属线的寄生电阻和寄生电感,Cox为氧化层电容,Rsub 和 Csub 指衬底的寄生电阻和寄生电容。

3、基于HFSS仿真建模及结果

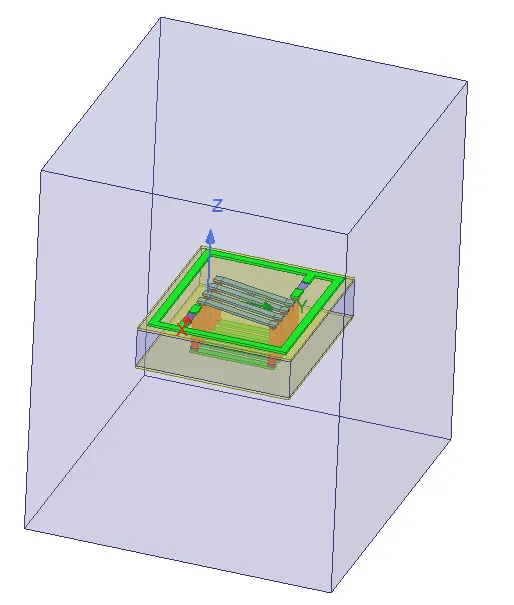

图3.1 HFSS仿真模型

基于ANSYS HFSS设计仿真模型如图3.1所示,介质为玻璃,分别对三维集成电感的电感值、品质因数、电容值以及电阻值进行仿真计算。其中电感计算公式为;Q因子计算公式为;电容计算公式为;电阻计算公式为。

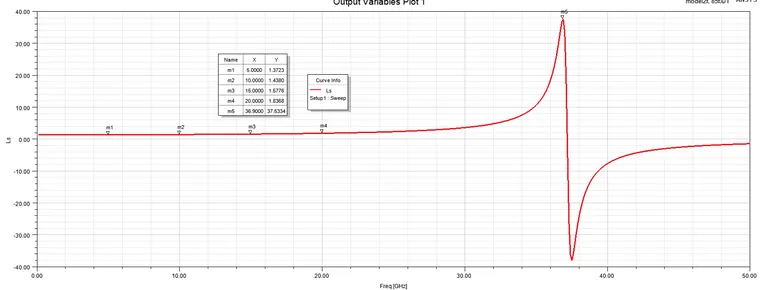

图3.2 电感值vs频率

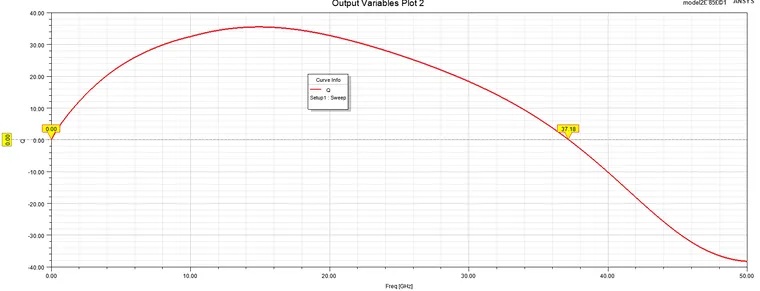

图3.3 Q因子vs频率

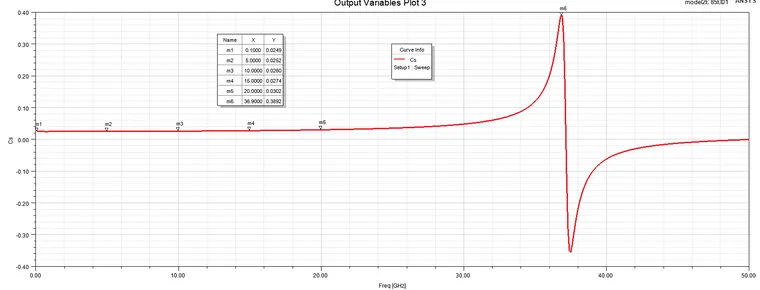

图3.4 电容VS频率

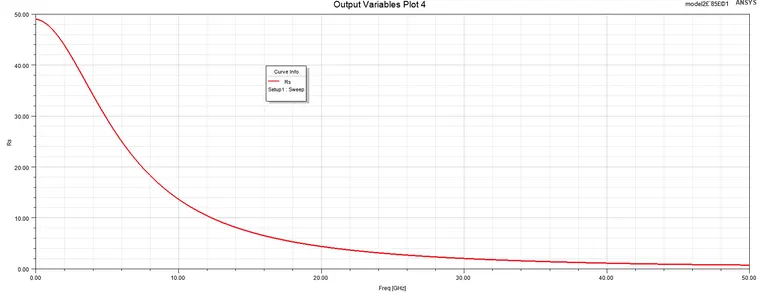

图3.5 电阻VS频率

仿真结果如图3.2-图3.5所示。可见,在频率较低时,电感值稳定在直流电感值 1.4nH 附近,而在自谐振频率点(37.18GHz,电感值为0 的频率点)附近电感值迅速增大,这是三维电感发生谐振的缘故。当频率大于自谐振频率时,电感值为负,此时三维集成电感不再表现出感性。品质因数随着频率的增大先增大后减小,品质因数峰值为 35.9,所处频率点为 15GHz,当超过自谐振频率时,品质因数也变为负。电感正常工作时,对地电容为0.02pf。由此可以看出,三维集成电感要在自谐振频率以下应用,并且工作频率离自谐振频率越远,电感越稳定,损耗越小。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。