多年来,设计人员一直在仿真中考虑封装寄生效应package parasitics 的影响,从使用简单的一阶模型(如理想电感+电阻)到更复杂的spice梯形网络,最后到使用三维电磁仿真器充分提取封装的s参数。对于封装加PCB通道,目前最常用的方法是将封装和电路板作为s参数或宽带SPICE模型独立地提取出来,并在电路仿真器中结合这两种模型。但由于工作频率高、信号速度快、集成器件复杂等因素,这种方法的局限性越来越大。

封装与PCB(或封装与电路)之间的耦合对性能有着不可忽视的影响。实现复杂封装和PCB,或封装和电路的仿真有几个挑战:电磁求解器的容量和精度,自动化,易用性,可接受的仿真时间。

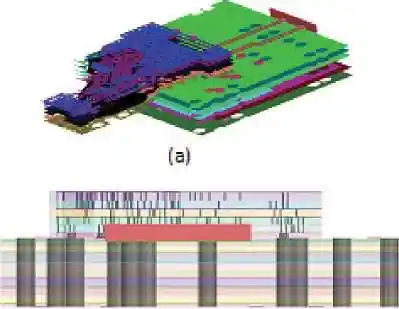

PCB和封装设计人员深知在更高层次的系统仿真中,提取其精确的设计模型是多么重要。采用三维全波电磁仿真和自动自适应网格划分方案,可提供提取全波s参数模型所需的精度水平。然而,设计人员在尝试使用三维电磁仿真来解决复杂的设计时面临着一些挑战,如图1所示。电路板和封装器件通常采用电子设计自动化(EDA)工具进行设计,需要引入到三维电磁仿真工具中。这些设计包括多个介质层、电源和接地层、信号层、大量过孔(与焊盘定义相关)和键合线。

第一个挑战是从EDA工具中导入数据库,但不包括应用于设计的手动修改,但要保留跟踪、焊盘、焊线、网络和引脚的数据库信息。导入几何体后,其他仿真模拟设置(例如,端口定义)需要易于使用,避免耗时的工程工作,并为非专业用户提供可访问性。最后,三维电磁仿真工具需要强大的网格、求解器和高性能计算功能,以将仿真时间缩短到可接受的水平,同时提供准确度。本文详细介绍了一种用ANSYS®HFSS™3D Layout进行整合了封装和PCB电路板的三维电磁仿真的新流程。

图1. PCB电路板的封装:(a)3/4视图(b)侧视图

第一个创新是为Ansys HFSS提供替代接口,Ansys HFSS是进行三维全波电磁仿真、精度和速度的黄金标准工具,适用于具有分层结构和设计的流程。设计条目是一个二维布局,具有用于创建三维结构的相关叠层定义(图2)。

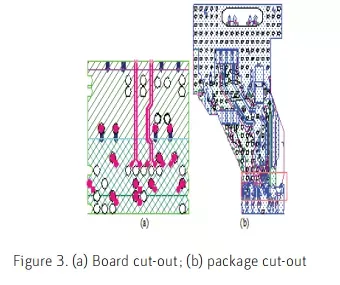

此接口类似于电路板和封装设计人员在经典EDA流程中使用的接口。通过读取*.brd、*.mcm、*.sip或ODB++,可以导入完整的数据库设计。所有信息,制图图元drawing primitives、网络、焊盘padstack、焊线bondwire和堆栈定义stack-up都在3-D布局界面中转换。此外,维护绘图原语允许定义参数,如轨迹宽度,这在简单多边形中是不可能的。一旦导入之后,可以通过选择感兴趣的网格或使用多边形指定区域来裁剪布局的一部分。使用*.brd文件导入整个PCB电路板,然后通过选择几个网络创建一个裁剪设计。使用*.MCM文件导入完整的封装,然后通过选择感兴趣的网络创建一个切割设计。

图3显示了封装和PCB电路板的俯视图。请注意,封装和PCB电路板并不具有相同的叠层,如果您想在一次仿真中将PCB电路板和封装结合起来,这可能会是一个挑战。HFSS3D layout支持层次结构,这意味着您可以通过简单的复制/粘贴将具有不同堆栈的两个设计组合起来。

此外,维护制图图元允许定义参数,例如轨迹宽度,这在简单多边形中是不可能的。导入后,可以通过选择感兴趣的网络或使用多边形指定区域来剪切布局的一部分。使用*.brd文件导入整个PCB电路板,然后通过选择几个网络创建一个被剪裁过的局部设计。使用*.mcm文件导入完整的包,然后通过选择感兴趣的网络创建剪切设计。图3显示了组件和电路板的俯视图。请注意,包和板没有相同的堆栈,如果要在一个模拟中组合PCB电路板和封装,这可能是一个挑战。HFSS3D layout流支持层次结构,这意味着您可以通过简单的复制/粘贴将具有不同堆栈的两个设计组合起来。

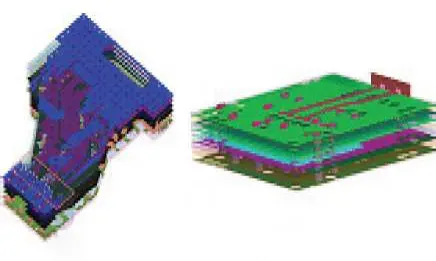

图4显示了封装,PCB电路板以及复制/粘贴整合了封装和PCB电路板设计结果的三维视图。整合封装和PCB电路板的设计清楚地表明,必须使用有限电介质才能正确地表示物理结构,因为封装的电介质层必须仅在封装所在的位置绘制。电磁求解器使用的有限元法(FEM)处理任意的三维结构和有限的介质层。

图4.封装设计、PCB电路板设计、复制/粘贴后的PCB电路板的封装

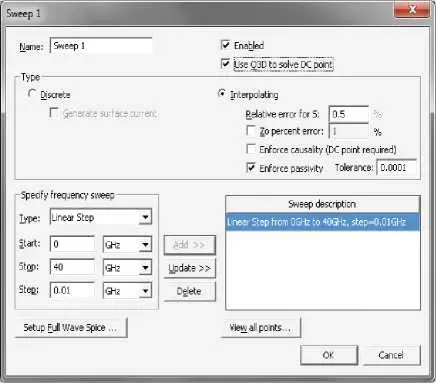

导入设计后,在运行模拟之前还需要执行几个步骤。第一步是定义激励。由于实现了显著的自动化,此步骤非常简单,只需选择一个边缘或过孔并将其转换到一个端口(图5)。创建端口后,还需要三个步骤:定义仿真设置、频率扫描和空气腔大小。这些都是通过在相关属性窗口中输入参数来完成的。仿真设置定义解算器用于创建初始网格和完成自动自适应网格过程的参数。有几个选项允许用户根据仿真的结构优化设置。对于这种特定的设计,解决方案频率设置为20 GHz(用于自适应处理的频率),因为我们希望仿真结果为0 GHz到40 GHz的带宽。将基函数的阶数设置为混合阶,并选择迭代求解器。频率扫描设置是根据提取模型的最终用途定义的。在大多数情况下,提取的模型用于时域电路仿真,结合有源模型(驱动、接收)来评估封装和板对传输信号的影响。例如,可以评估眼图 eye diagram 性能。即使提取的模型可以是宽带SPICE模型,默认格式也是S参数。

S参数文件需要验证特定的时域电路模拟标准:

频率扫描设置提供了与这些标准相关的特定选项(图6)。通过选中“使用Q3D求解直流点”选项,将调用准静态求解器来精确计算直流点。用户可以选择离散扫描,对其模拟扫描的所有频率,或使用自适应有理函数插值方法执行扫描的插值扫描。对于宽带模拟,插值扫描比离散扫描快得多,但在某些情况下,可能会导致非被动或非因果结果。用户可以选择为插值扫描强制被动性和强制因果关系。通常,强制执行被动性就足够了。

在这种情况下,我们使用插值扫描,并选择“使用Q3D解决直流点”和“强制无源性Enforce passivity.”选项。关于因果性,非因果结果的一个常见原因是使用了没有定义频率依赖性的材料特性。在该仿真中,我们使用了频率相关的材料属性。

图6. 频率扫描属性窗口

本文的第一部分强调了为PCB电路板和封装设计人员提供自动化和用户友好界面的重要性。传统、繁杂的经典三维电磁仿真器用户界面是非专家用户更广泛地使用这些工具的主要阻碍之一。另一个阻碍可以通过这个问题来说明:运行我的仿真和分析结果需要多长时间?Ansys HFSS 3D layout以比您预期更快的速度回答了这个问题,这要归功于以下几项:

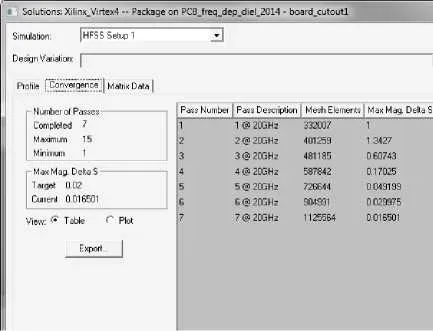

图7. 收敛表

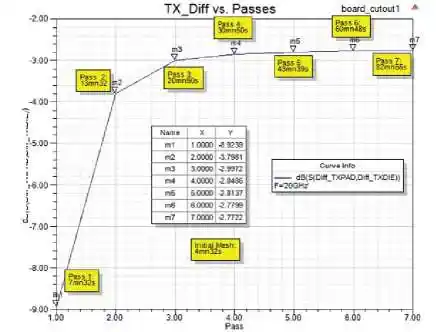

自动自适应网格过程基于迭代网格细化,识别需要细化网格的区域,以减少两个解决方案之间的误差。图7显示了说明自适应网格过程进展的收敛过程。经过七次收敛后,达到接近0.01的误差,网格单元数略超过100万。图8显示了连接封装和PCB电路板的TX差分对在20GHz(自适应频率)下相对于自适应通道的插入损耗。采用16核进行自适应处理。使用Phimesher,创建初始网格的时间不到5分钟;在过去,使用标准经典网格器所需的时间明显更长。第三次通过是在21分钟后完成的,最终解决方案的为数值+/-10%,这意味着在20分钟内您可以完成这个复杂设计的健全性检查。第五次通过是在44分钟后完成,数值小于最终解的+/-2%。第五遍、第六遍和第七遍之间的数值变化表明收敛已经实现,确保在1小时20分钟内获得选定精度的最佳网格。

图8. TX差分对相对于自适应通道的插入损耗

对于多层几何结构,如印刷电路板、封装和集成电路,phi mesher提供了非常快速的初始共形四面体网格生成。这些结构通常表现出高度的几何复杂性,与许多走线、过孔、焊盘和焊球或凸点相关。这种复杂性可能导致初始网格生成时间接近甚至超过电磁仿真本身的总时间。与传统的有限元网格技术不同,传统的有限元网格技术对给定的几何结构不作任何假设,phi mesher利用了有关这些分层设计的叠加特性的知识。phi-mesher将层分解为一组凸多边形,从中导出三维凸多面体来填充层内的体积,然后进一步处理为保角四面体以形成初始三维四面体网格。该算法避免了三维有限元网格划分中常见的复杂而耗时的创建和销毁交换过程。所有复杂的计算都是在二维而不是三维中进行的,从而进一步增强了算法的鲁棒性和可扩展性。最终结果是,对于这些类型的复杂分层结构,与通用的三维有限元网格技术相比,phi mesher可以减少30倍或更多的网格时间。

在0 GHz至40 GHz范围内进行频率扫描,以提取所需带宽内的s-parameter模型。后处理允许自动识别来自单端终端的差分对。结果可绘制为单端端子或差分对。各种结果如下(图8插入损耗(单位dB);图9接收(RX)和发送(TX)两个差分对的回波损耗(单位dB);图11 RX和TX差分对之间的隔离度)。根据规格,设计人员将确定板载封装器件的使用频率范围。

图9. 两个差分对的损耗与频率的关系

Ansys HFSS 3D layout为封装、IC在印刷电路板上的仿真和提取提供了一种创新的工艺。强大的自动化功能可使设计人员快速,轻松地将电路板和封装设计从现有的布局设计流程转移到3-D电磁仿真器,为仿真做好准备。自动自适应网格划分过程,更快的网格划分和高性能计算能力可提供当今压缩和竞争性设计周期所需的精度水平和速度。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。