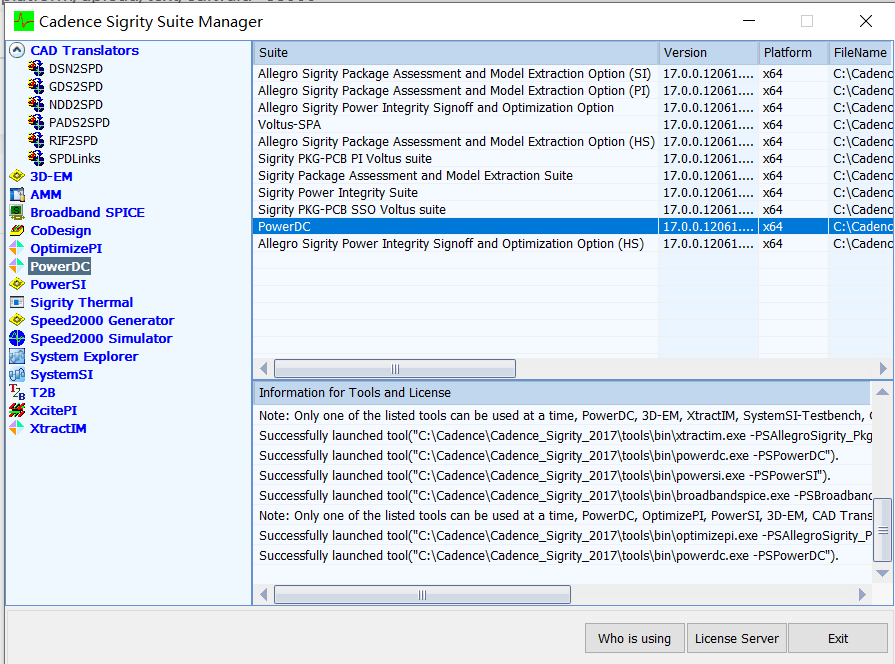

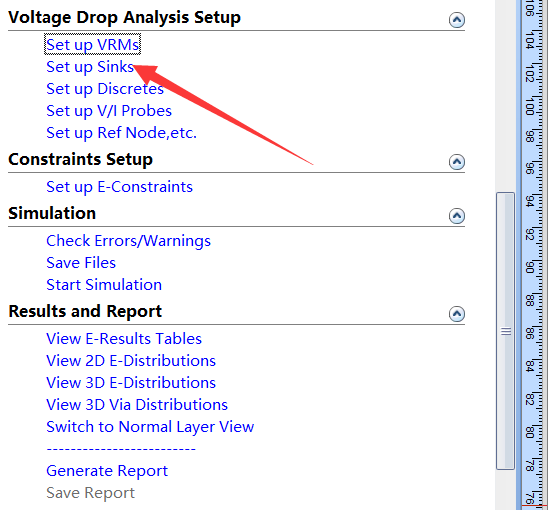

2.在左边的工作流程中找到单板直流压降分析:

单板直流压降分析

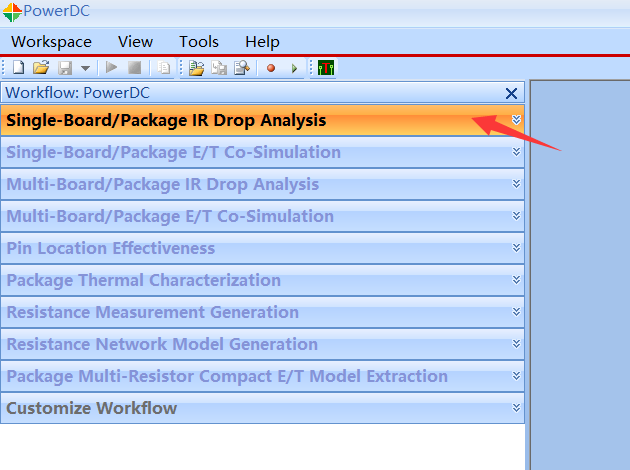

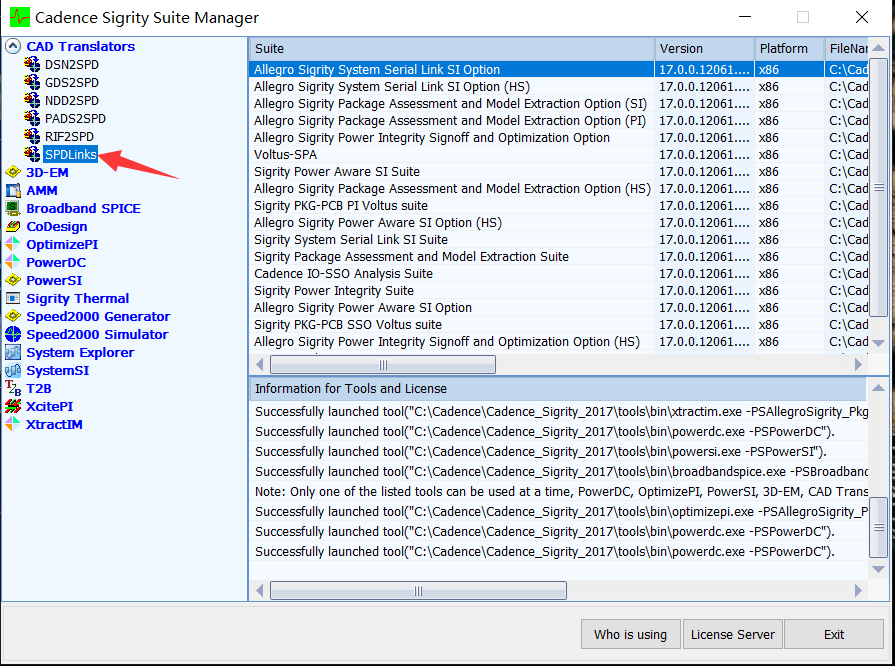

3.创建一个workspace,并且导入一个layout文件,(这里需要主要的是powerDC和powerSI使用的layout文件都是spd格式),当我们用allegro画好了pcb文件,它是brd后缀的,需要通过下面的插件:

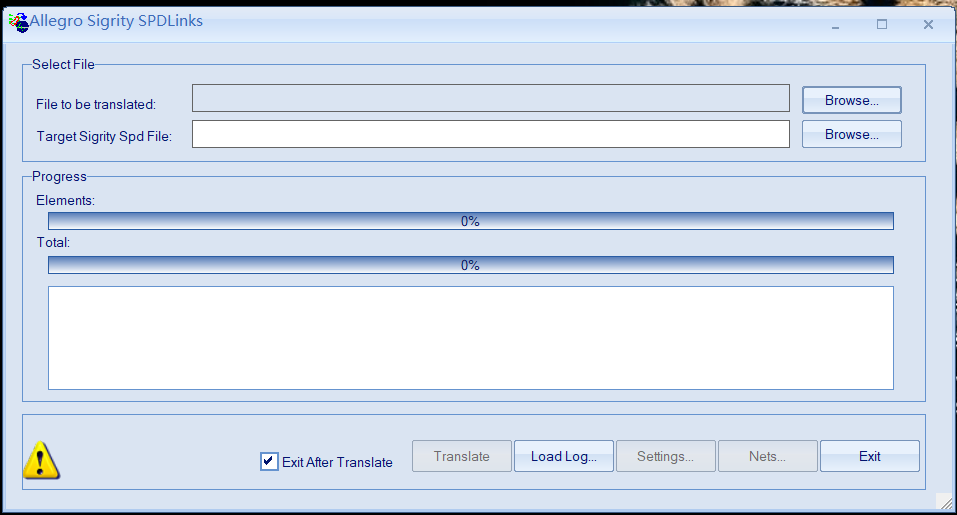

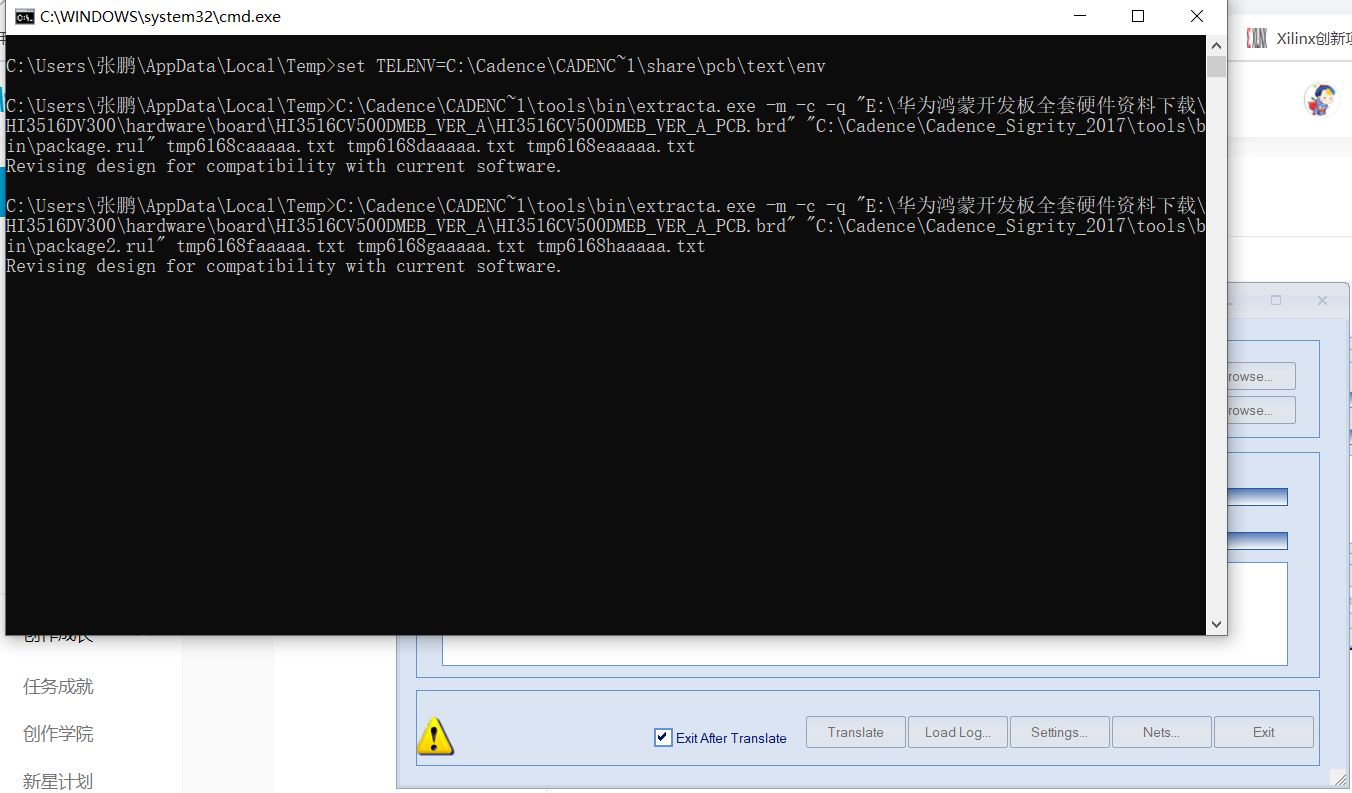

找到brd文件的位置,然后转换为spd文件,直接点击translate:

出现这样的窗口:

等待转换完成即可。

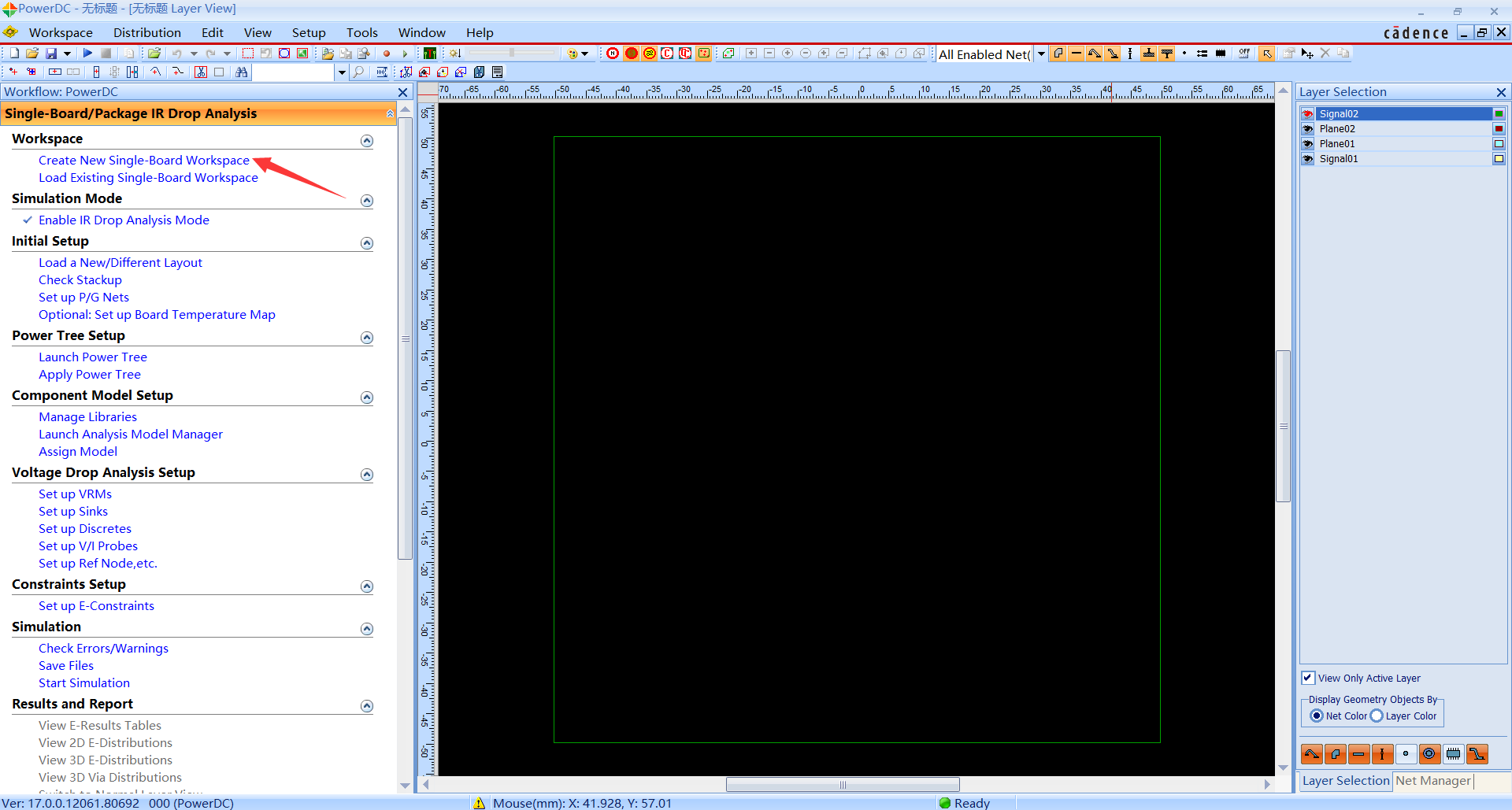

在powerDC中,首先create一个workspace:

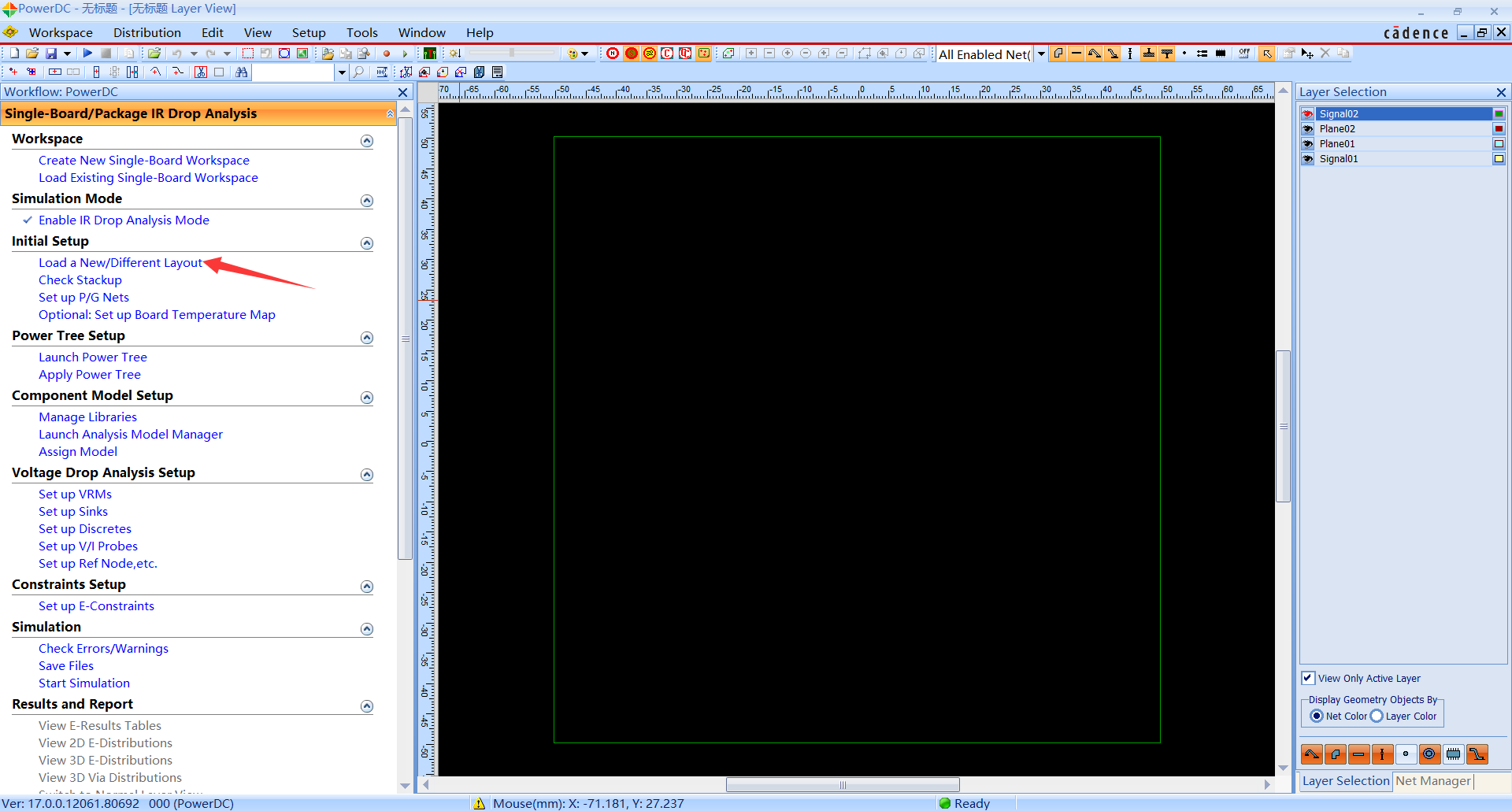

然后导入刚刚转换成功的spd文件:

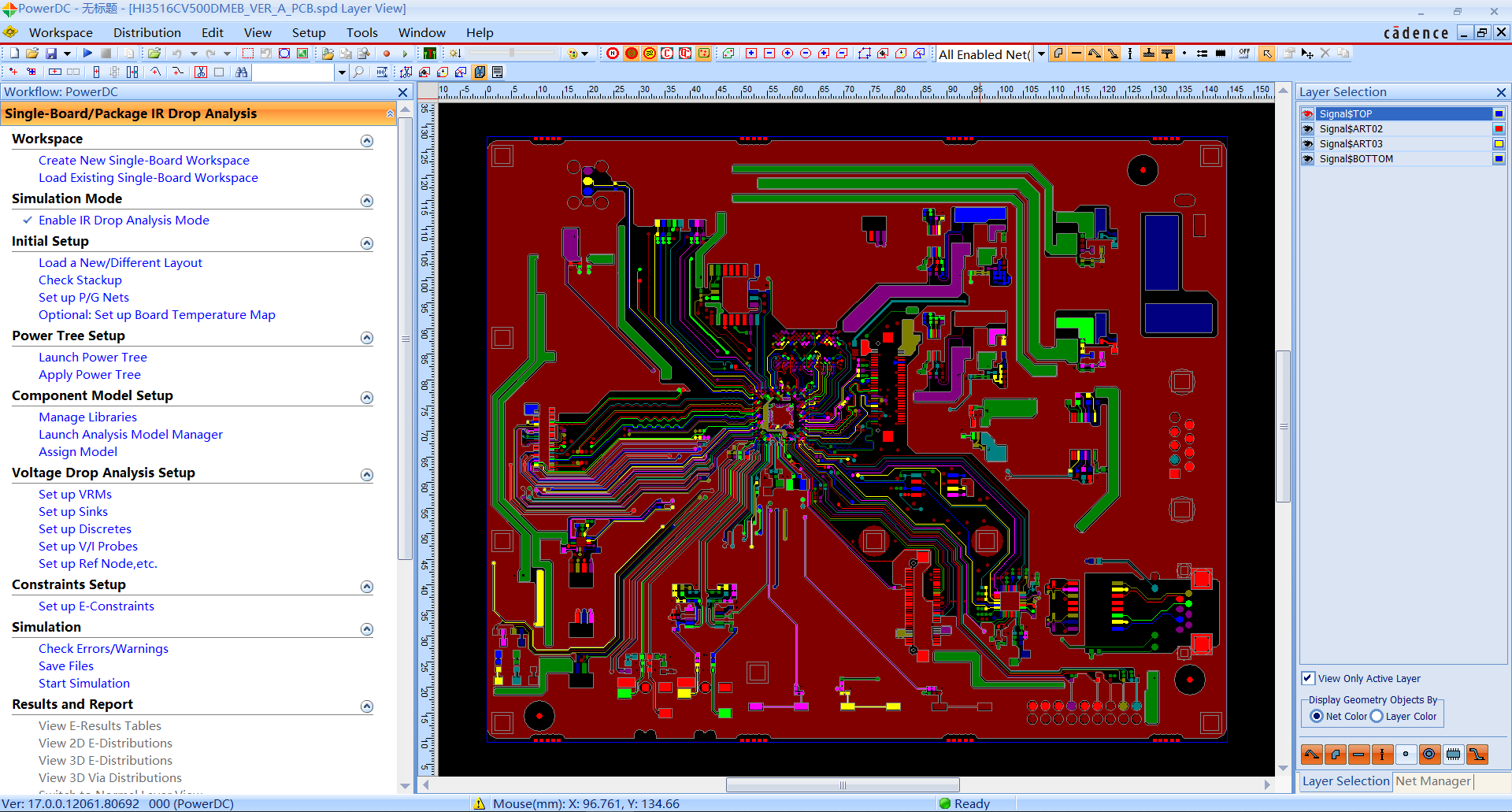

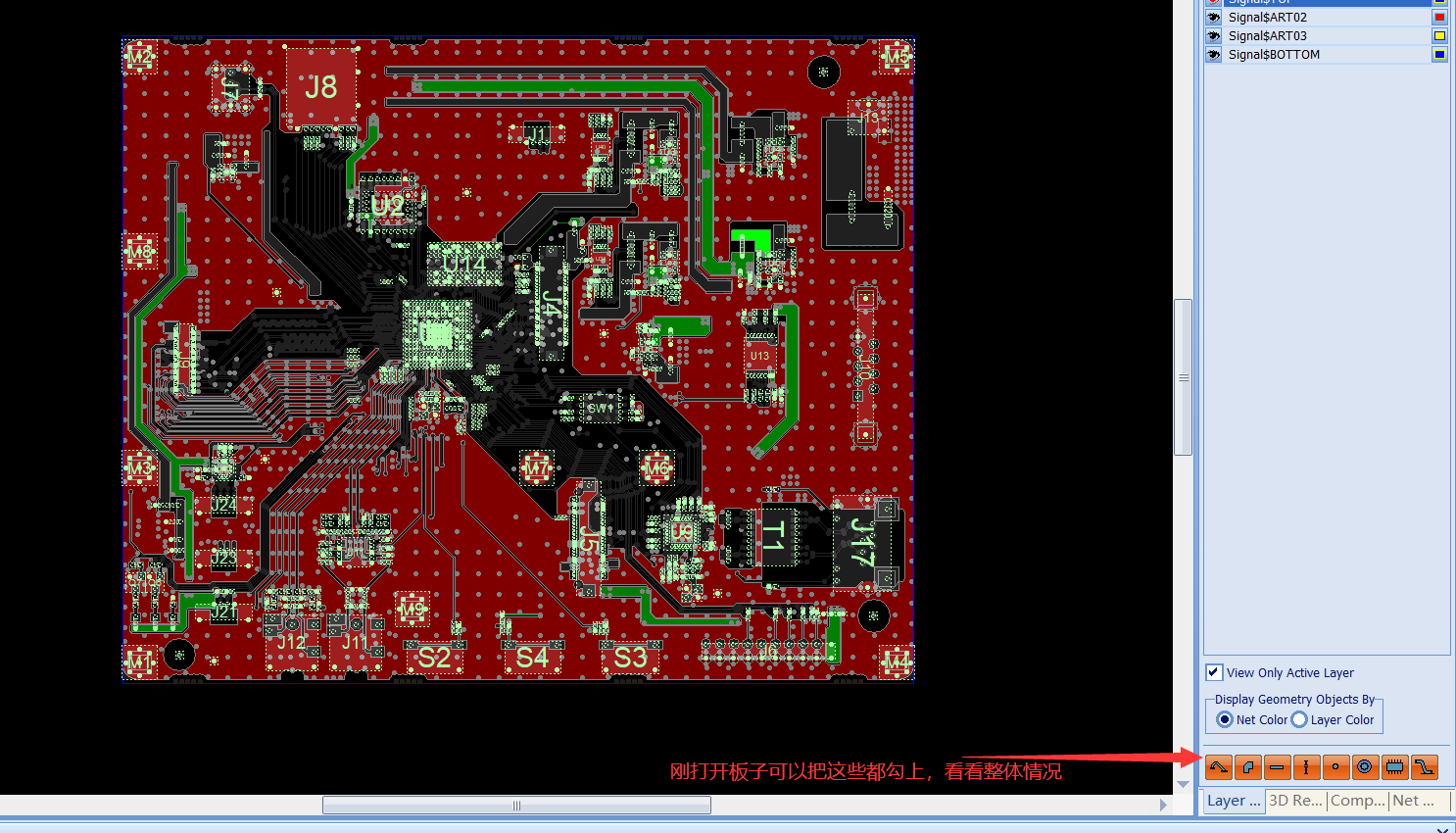

导入之后,界面如下:

然后按照左边的工作流程,一步步执行即可。

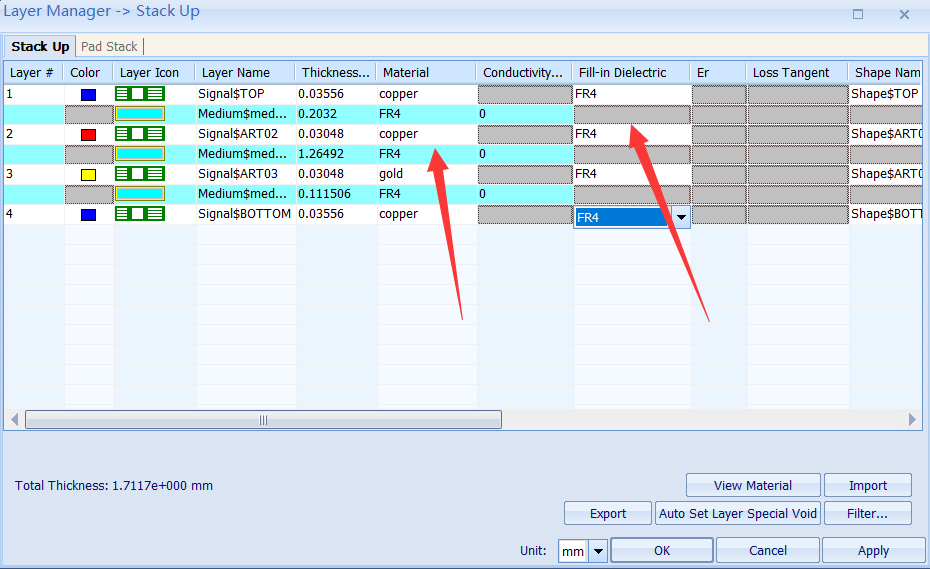

check stackup:就是检查pcb板层与pad的材料,厚度,介电常数设置等,这些数值一般在画好pcb之后自动产生了。需要注意的是:signal层一般都设置为copper,medium层一般都设置为FR4.另外fill-in Dieletric的绝缘物质也选择为FR4.

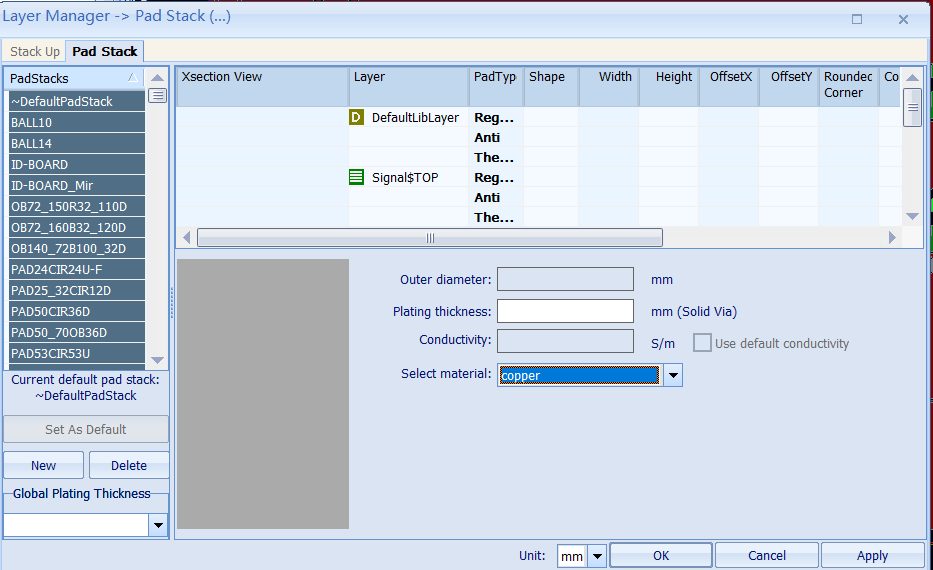

pad stack的材料也设置为copper,直接全选然后设置为copper。

然后就是setup 电源和地网络:

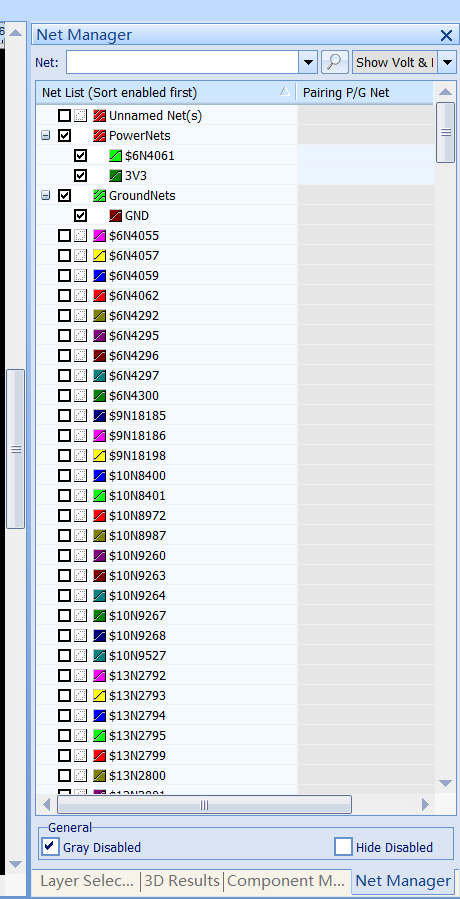

选择你要仿真的电源和地网络,然后把电源信号分到power group,地信号分到gnd group。

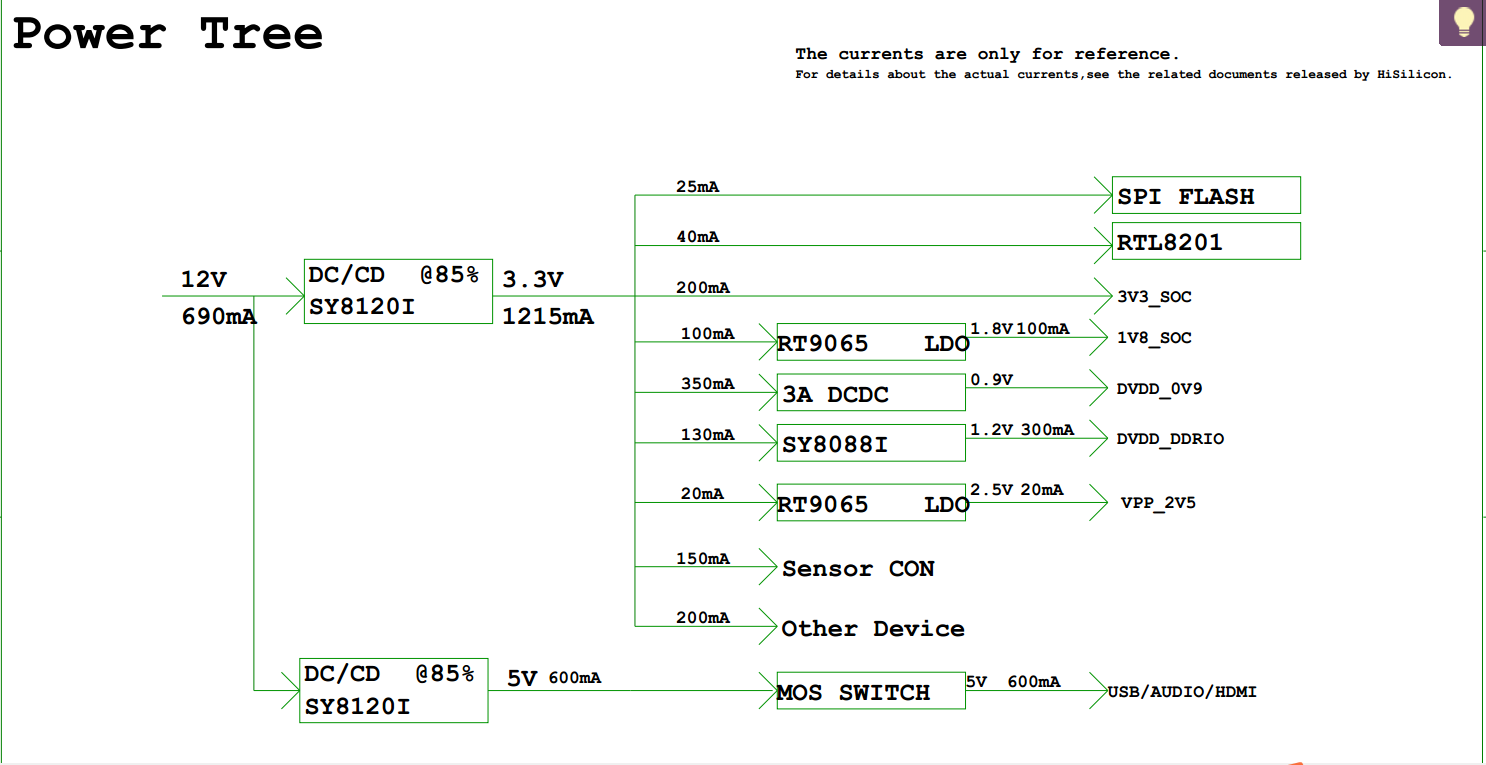

这里,既然我们要仿真电源压降,就必须要先看看power tree(pdf版本的,凑合看吧,以后再单独做一节sigrity生成的power tree)。

power tree

从上图可以看出,12v的输出直接到一个DC/DC,输出两路3.3v和5v,并给出了每路的电流(手动点赞)。3.3v的输出有非常多,这里我们就SY80881作为3.3V的负载端,看看输出在350mA的情况下,到达SY80881的电源压降能有多大。

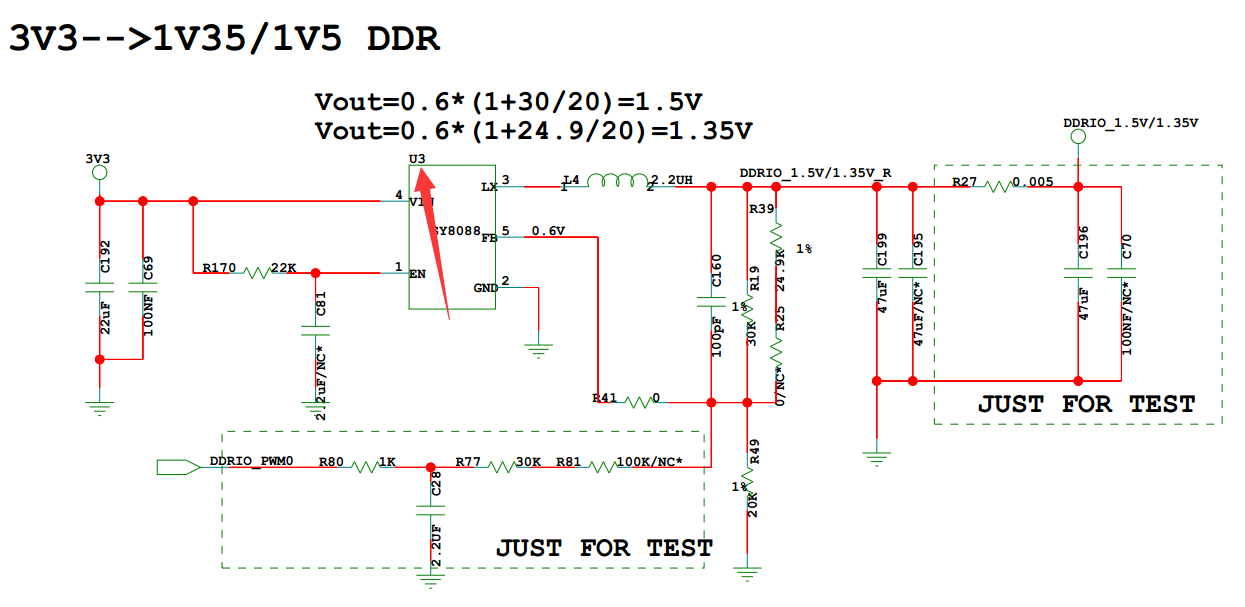

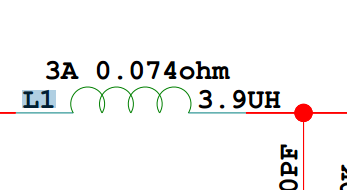

从原理图可以看到U5输出端LX经过一个L1到了3v3的net,然后3v3这一个电源供给很多芯片,这里我们选择U3作为负载端(sink)。

点击setup P/G net ,弹出上拉菜单,忽略setup P/G net .

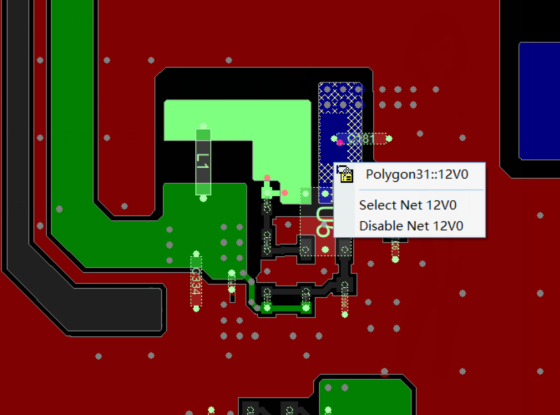

在PCB的layout如下:

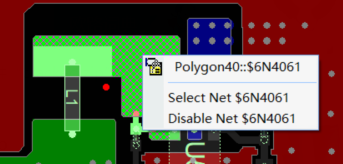

蓝色是12v0的输入,L1如图位置,中间是通过一片铜连接的,我们就需要将这片铜enable,并且设置为power group。它的名字是6N4061.

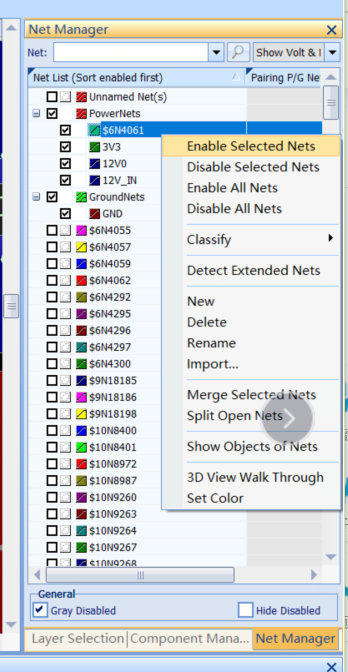

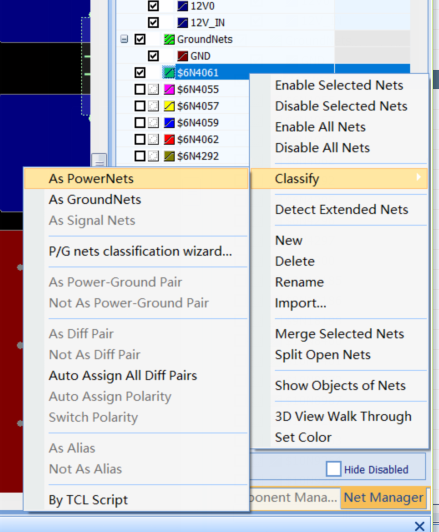

在net manager里,enable 这片铜。并且右键分类为power group。

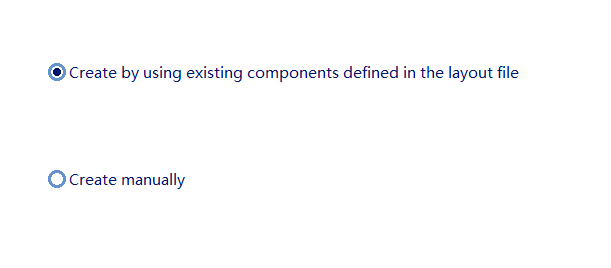

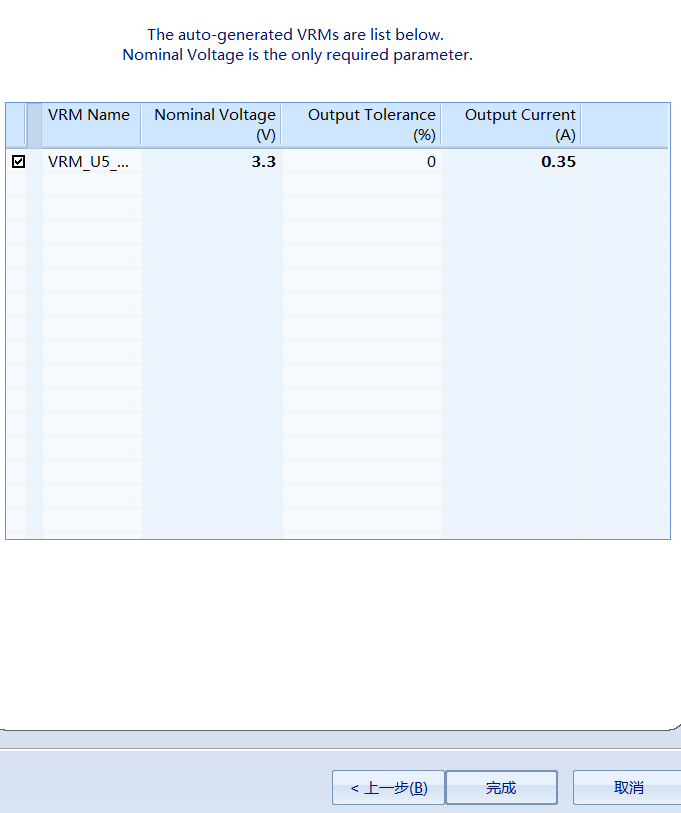

然后set up VRM,如下:

选中SY8120I.

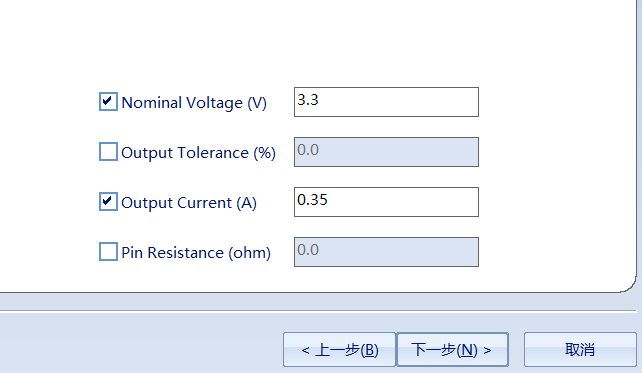

350mA是来自power tree的数值,然后点击完成。

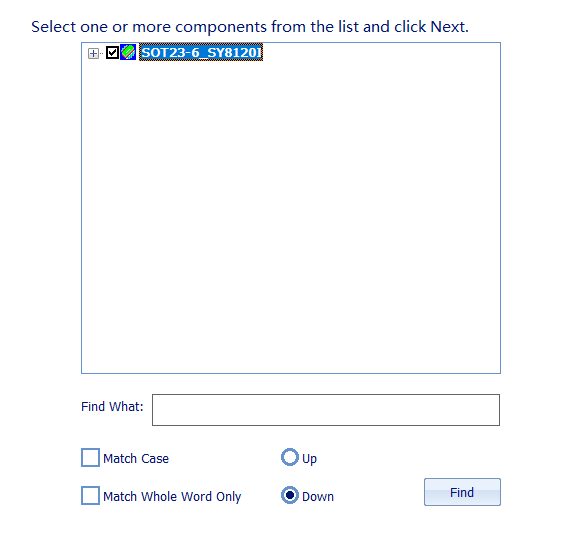

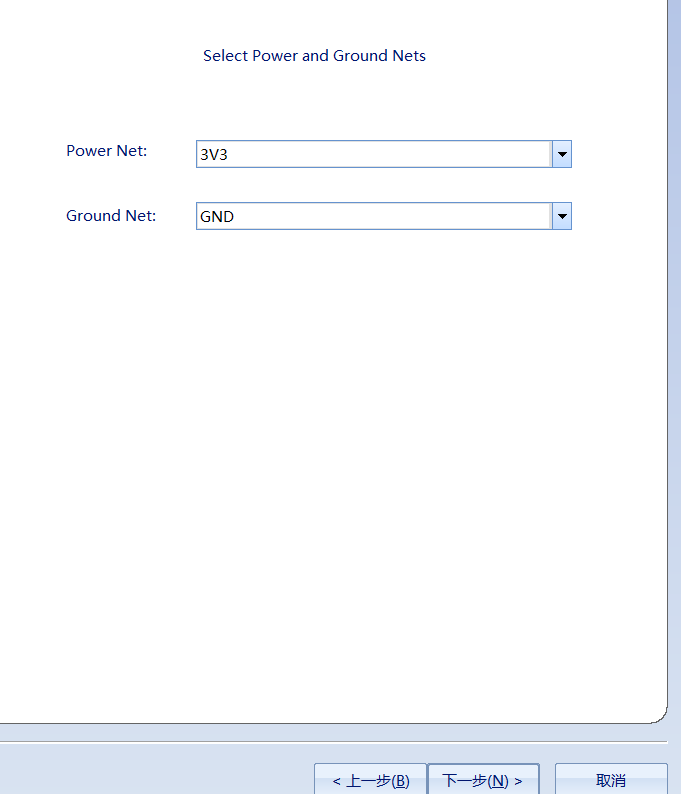

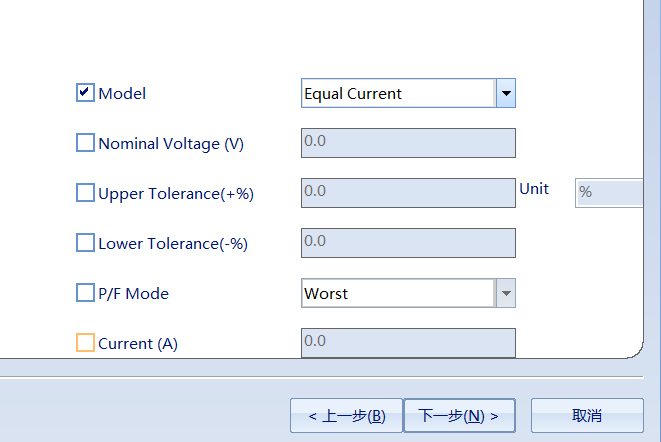

接下来set up sink。

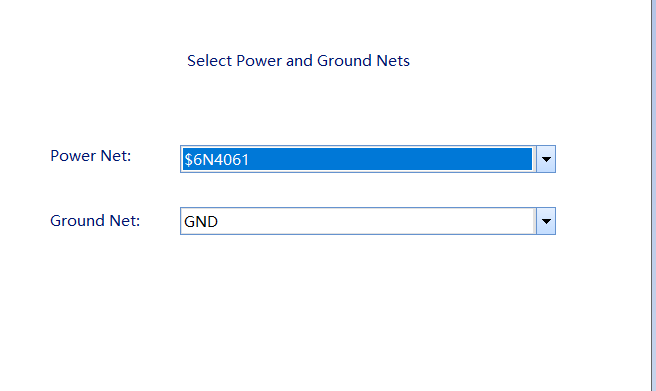

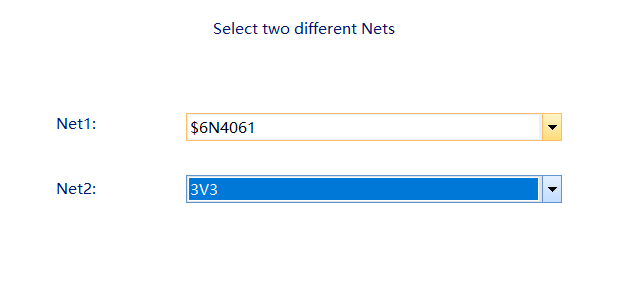

选择3v3和gnd。

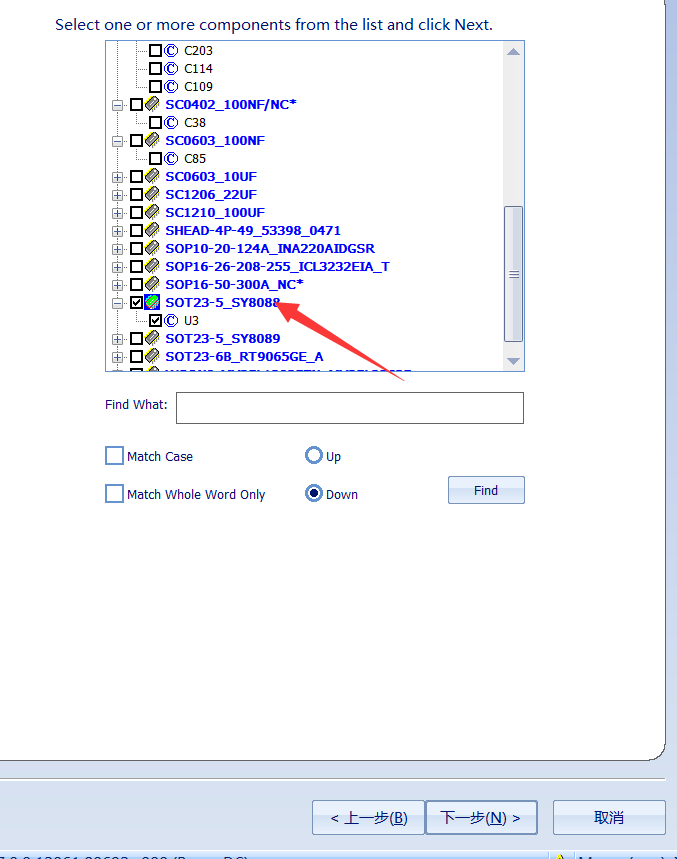

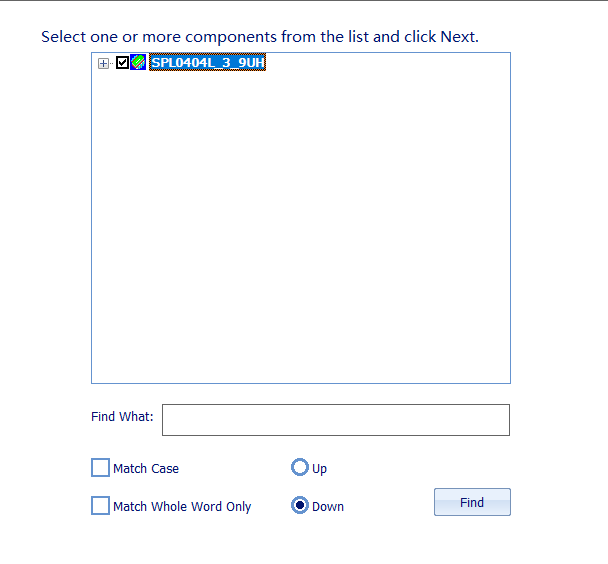

找到U3.

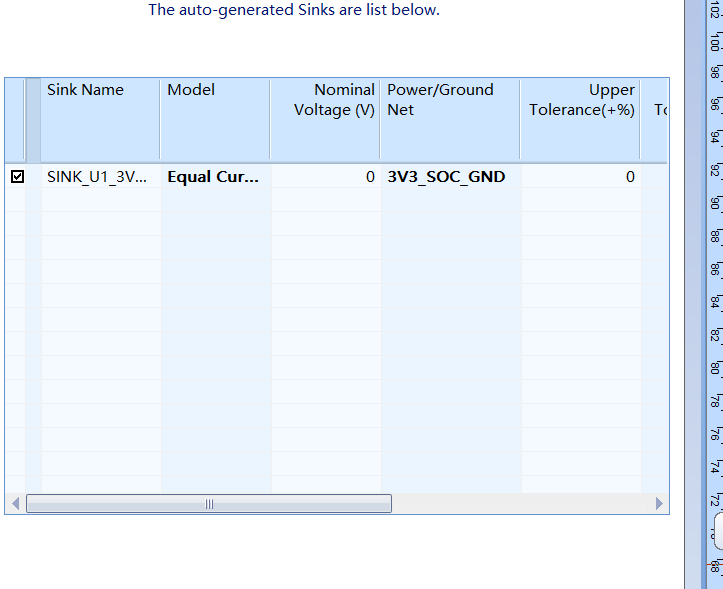

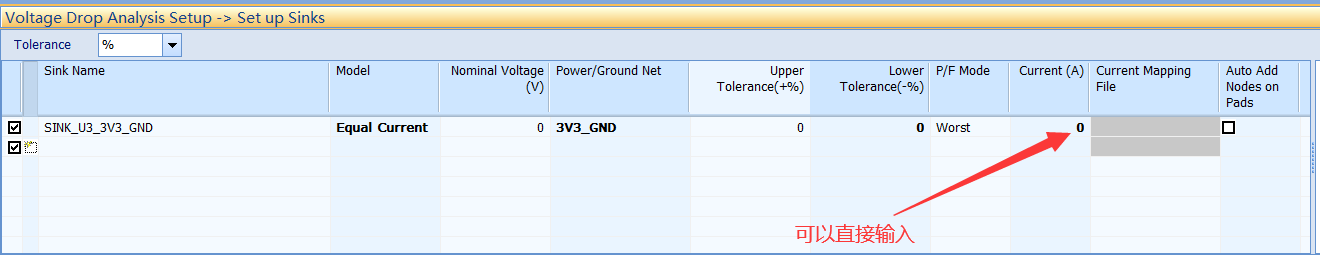

这里的current可以输入也可以不输入,等设置完成后,还可以在最下方的地方修改。

按图一直下一步,直到完成。

这里可以直接修改current。

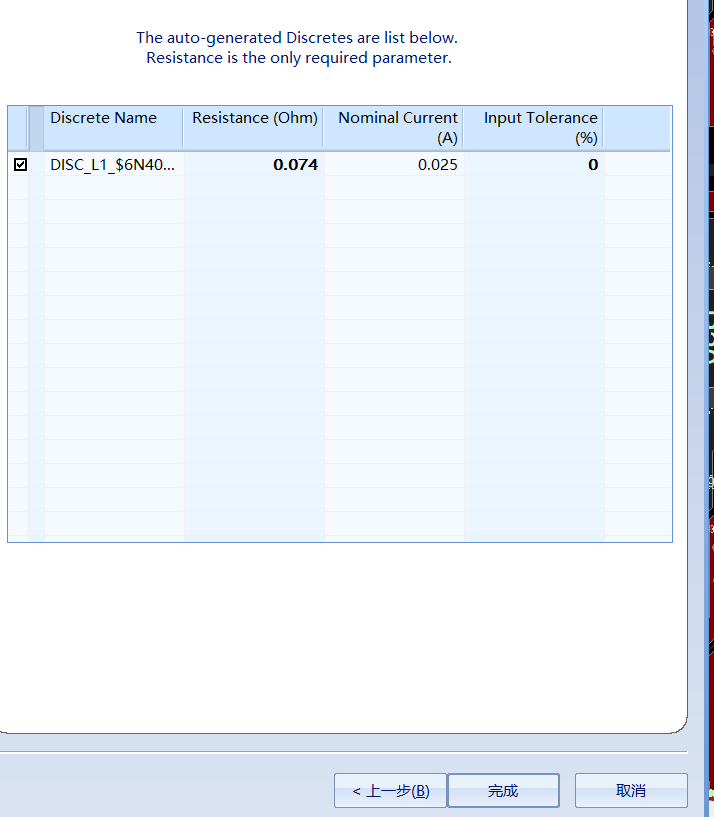

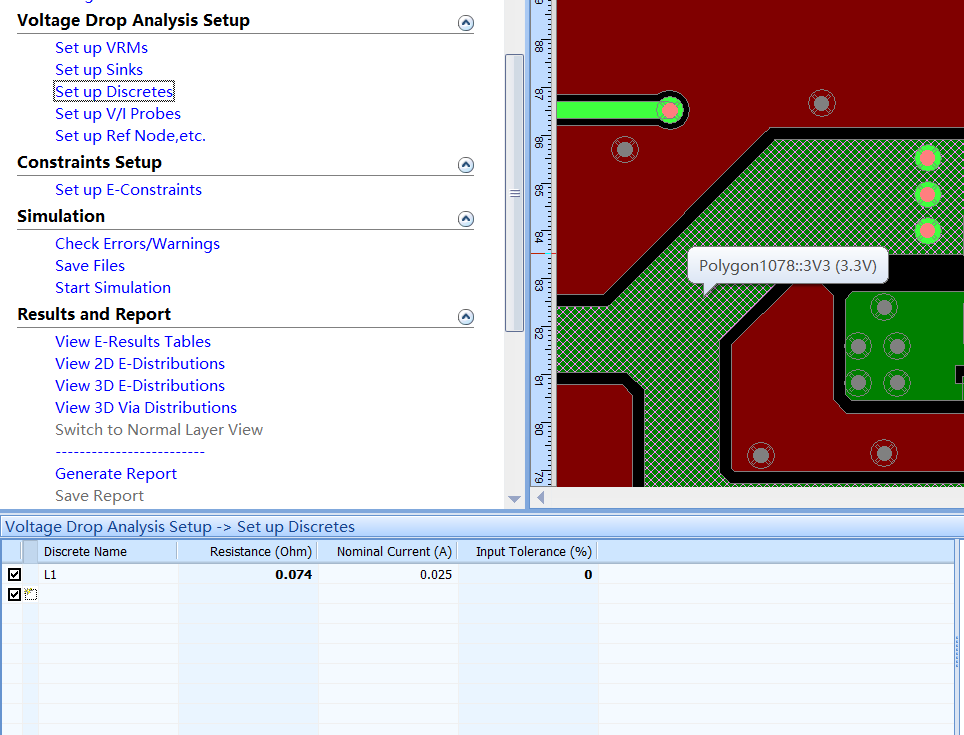

接下来设置分立元件,如下图:

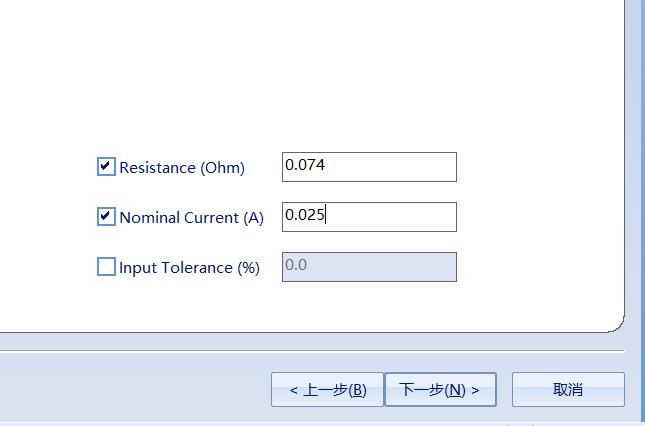

根据原理图,L1的电阻值是0.074欧姆,鼠标放在电阻值上会出现E用来编辑,将电流输入为0.025A,但是电阻值无法输入。尝试另外一种办法,将自动生成的remove。

在这里点右键会出现remove,因为我的已经remove,所以只有add了。

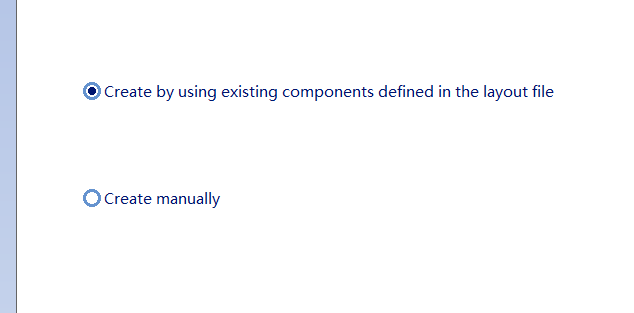

然后再点击set up 分立元件,按照下图:

设置完成是这样的:

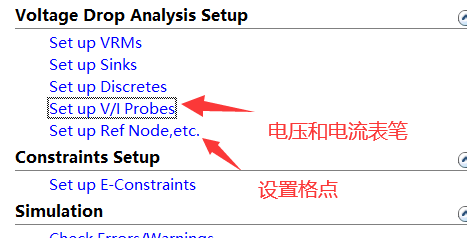

剩下的流程是添加电压和电流测试表笔,我们这里就不做了,还有设置格点的,当然格点越多最后的二维和三维图越精确,但是也更费时间和吃内存,我们就默认。

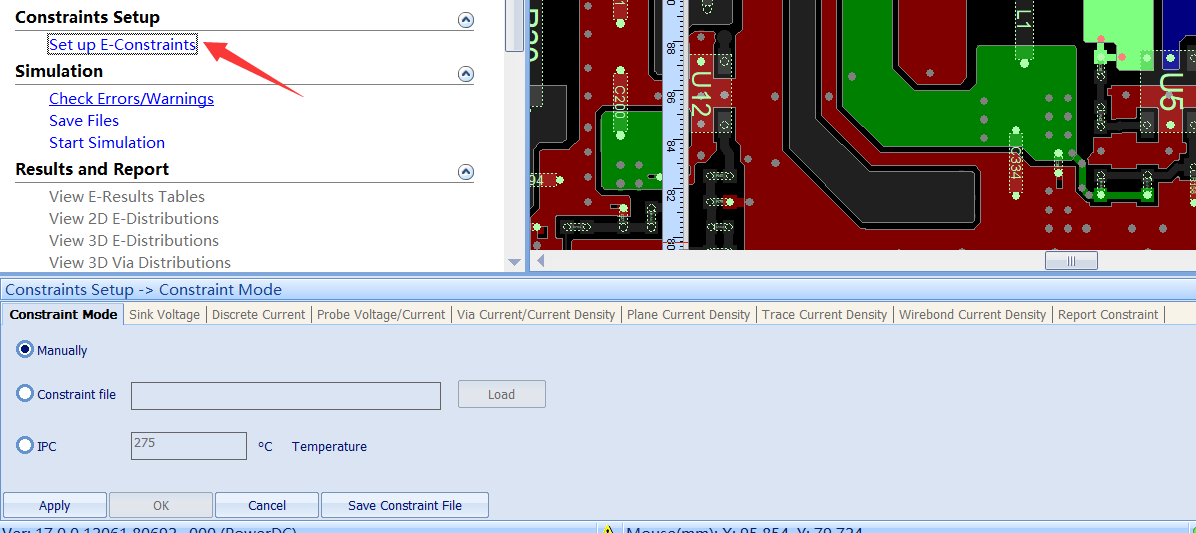

还有一个是设置约束的, 如果你知道你要求的过孔电流密度、平面电流密度、走线电流密度以及压降的容差等等,可以在这里设置,具体不清楚参数是计算的呢,可以参考IPC标准文件IPC-2152.

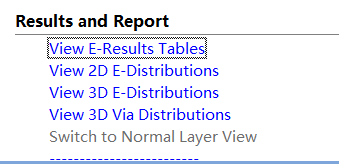

然后我们就是save file,并且开始仿真。仿真完成是这样的结果。

来回换了好几个电源网络仿真结果都是错的,这里吐槽一句,这个板子有一个问题就是,没有在DC/DC或者LDO的输出端添加网络标号,导致仿真的时候无法正确定位芯片,也就无法看到真实的仿真结果,这里凑合看一下样子吧?

电气仿真结果是:

可以看到实际输出电流为0,明显是错的。

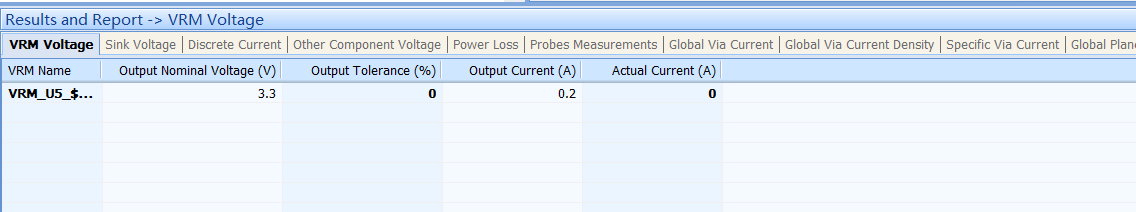

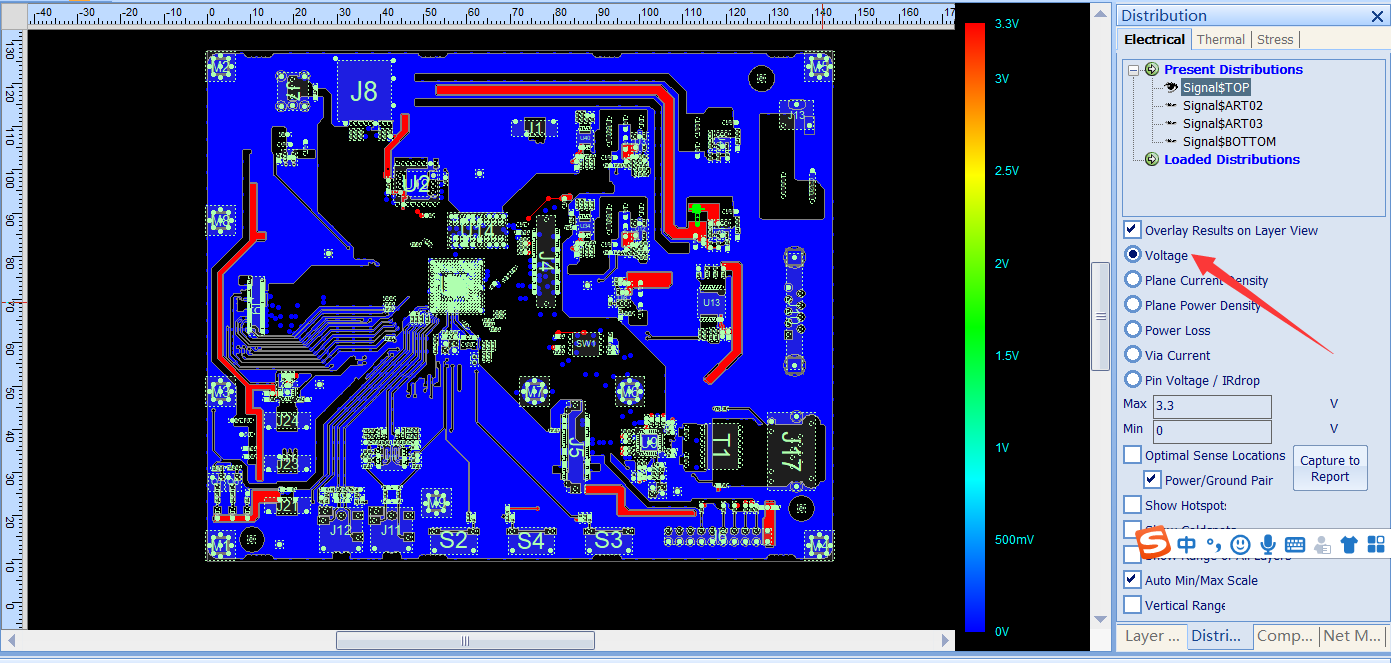

然后是电压分布:

顶层:

底层:

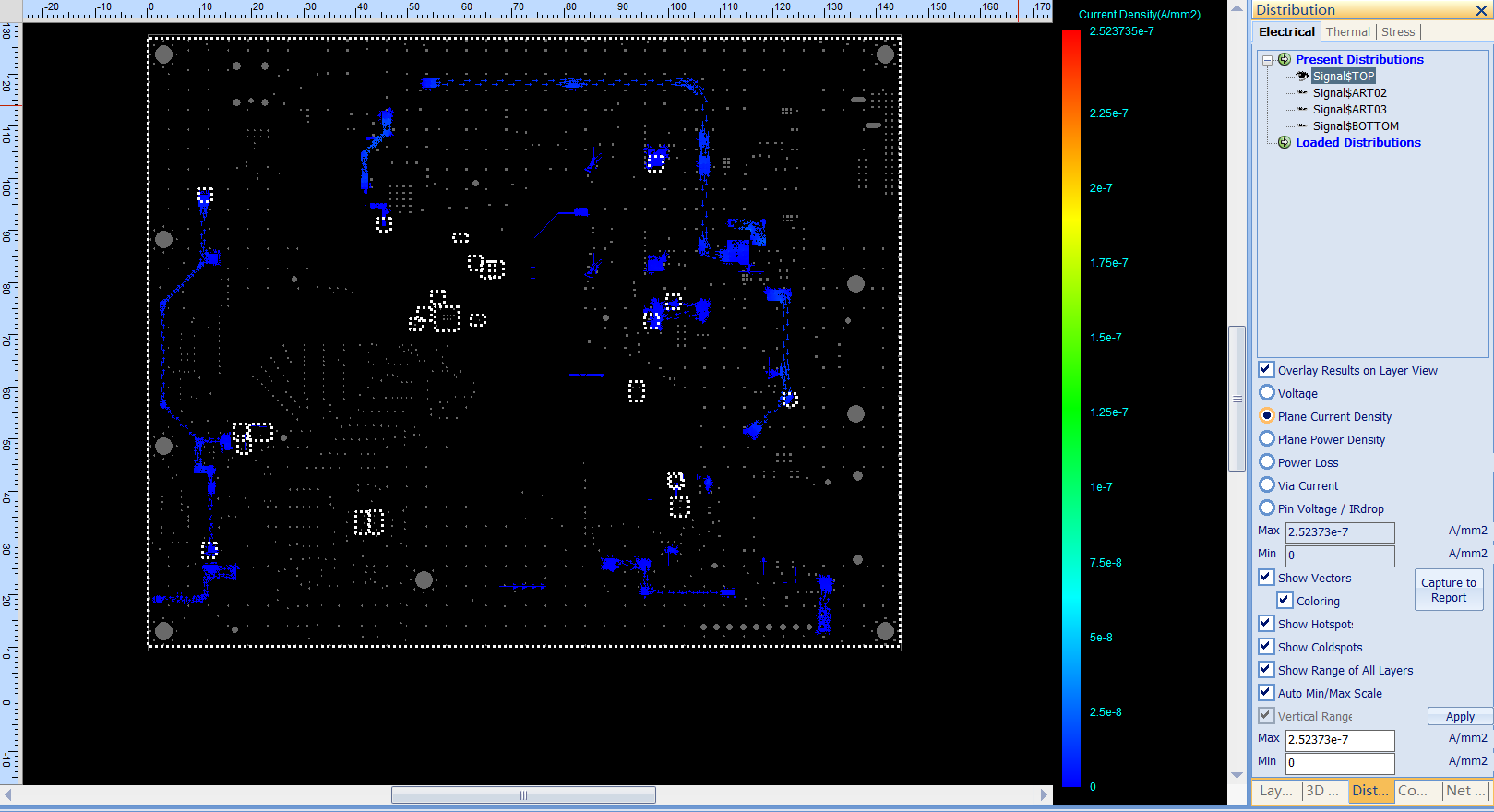

平面电流密度(电流几乎都是负的,肯定是不对的):

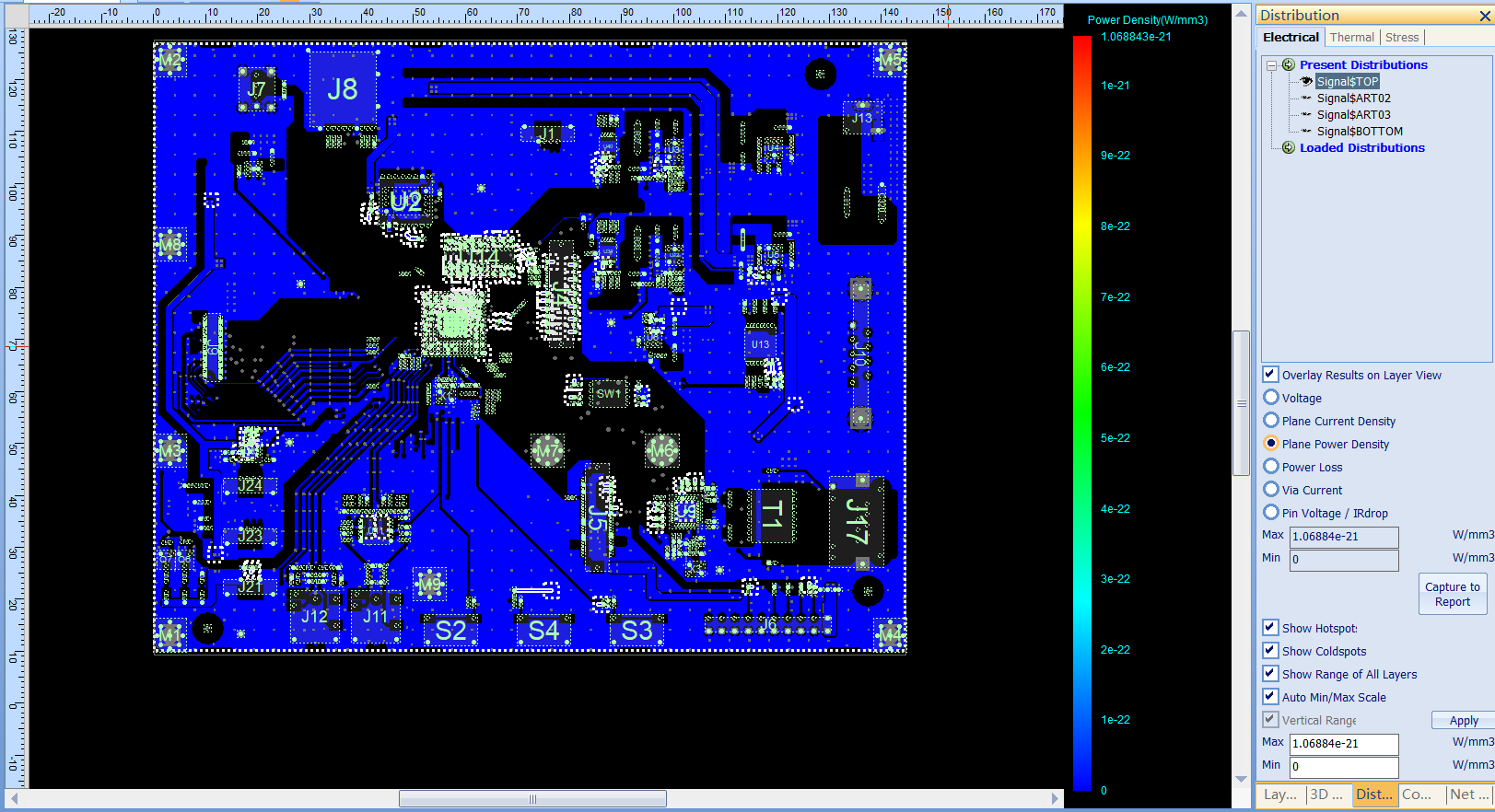

平面功率密度(也是基本为0,肯定是不对的):

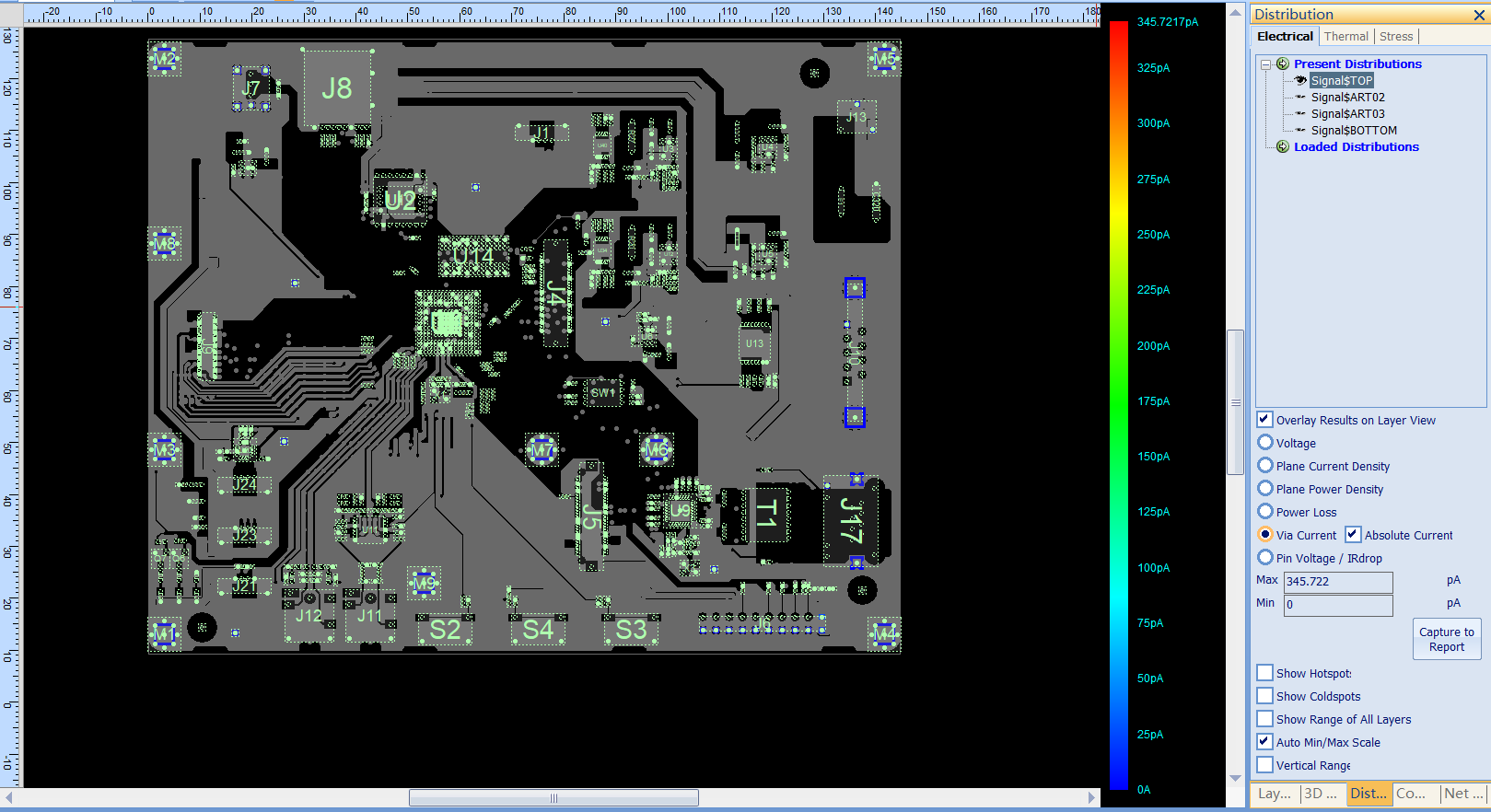

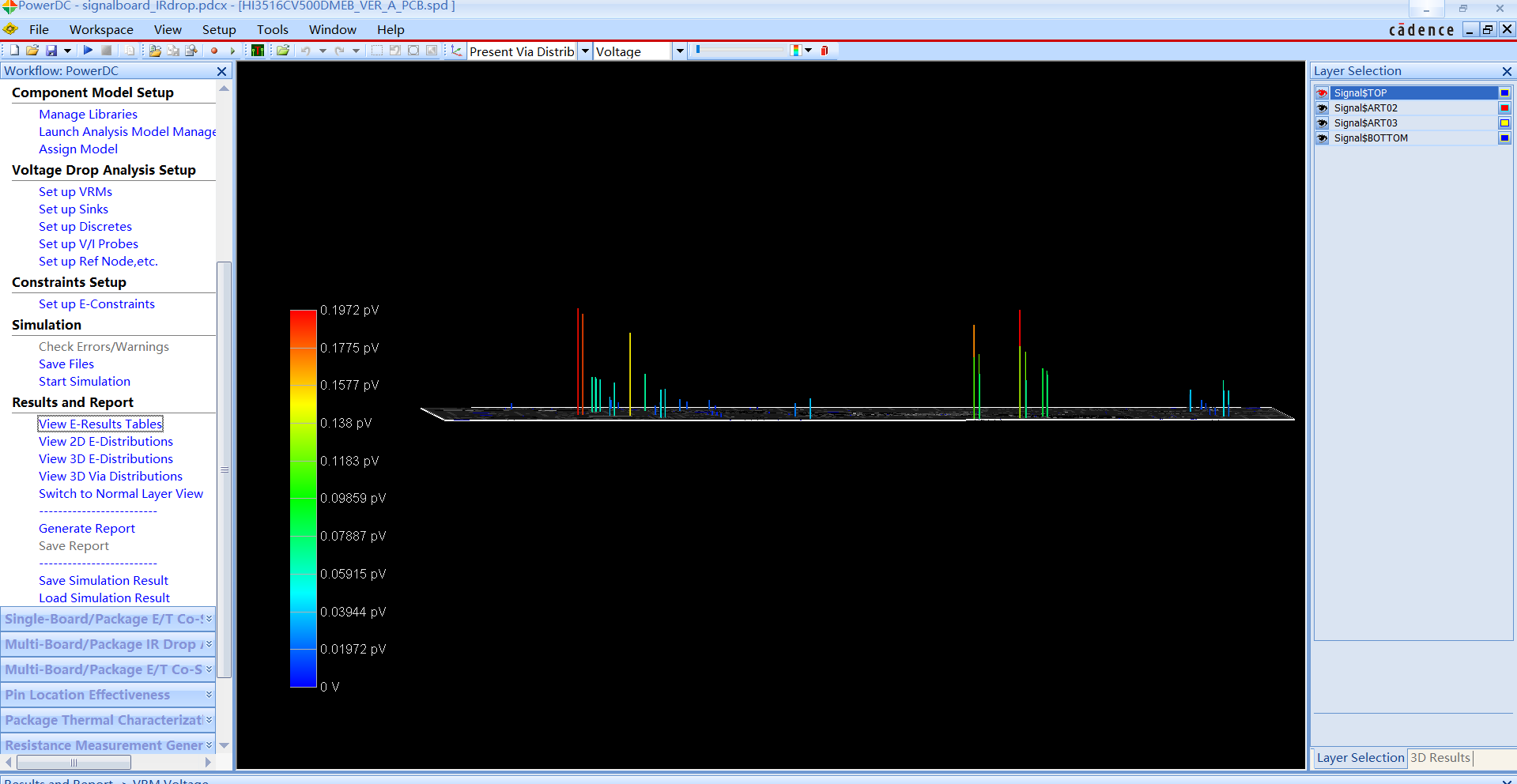

过孔电流:

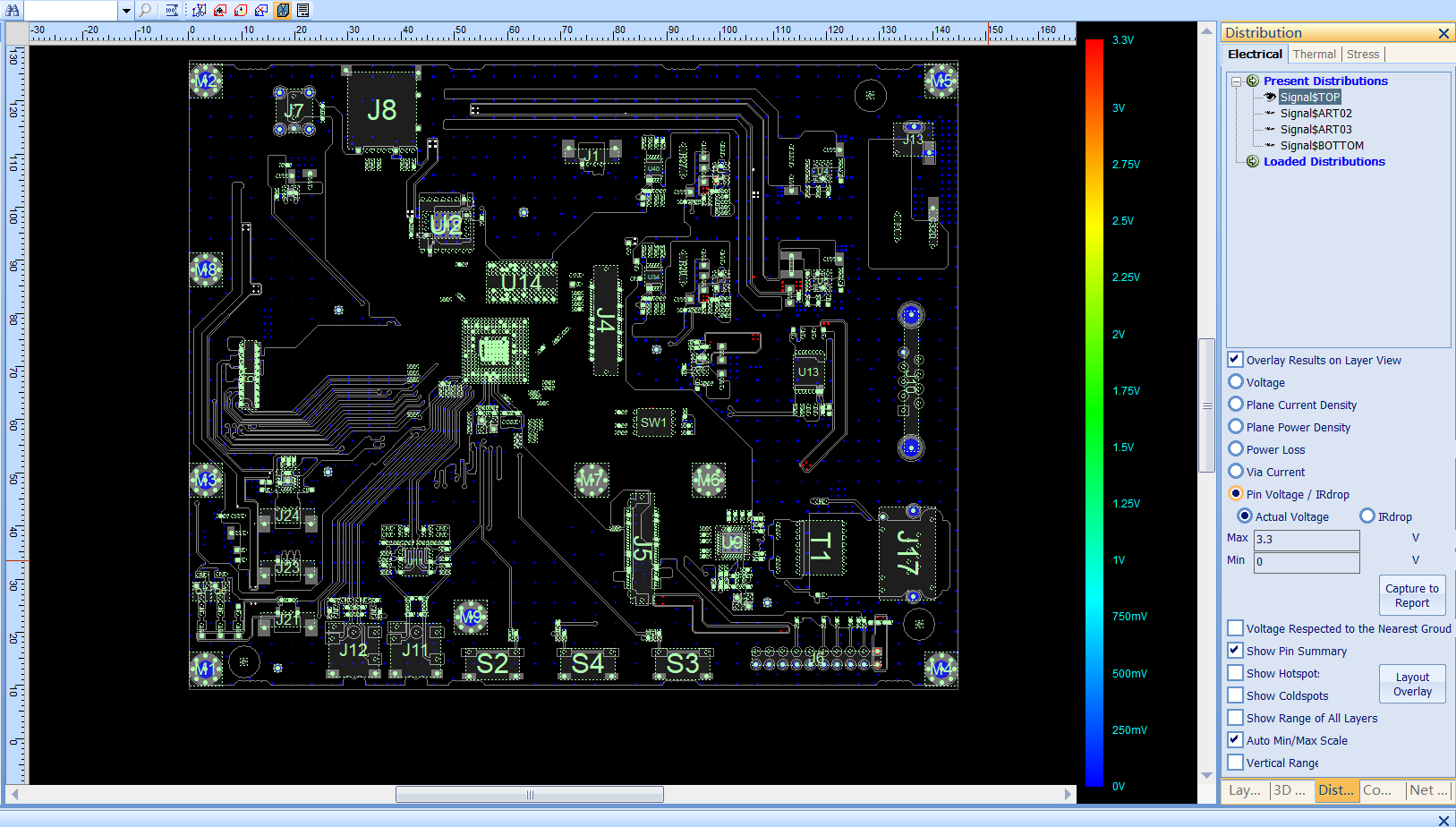

pin脚电压:

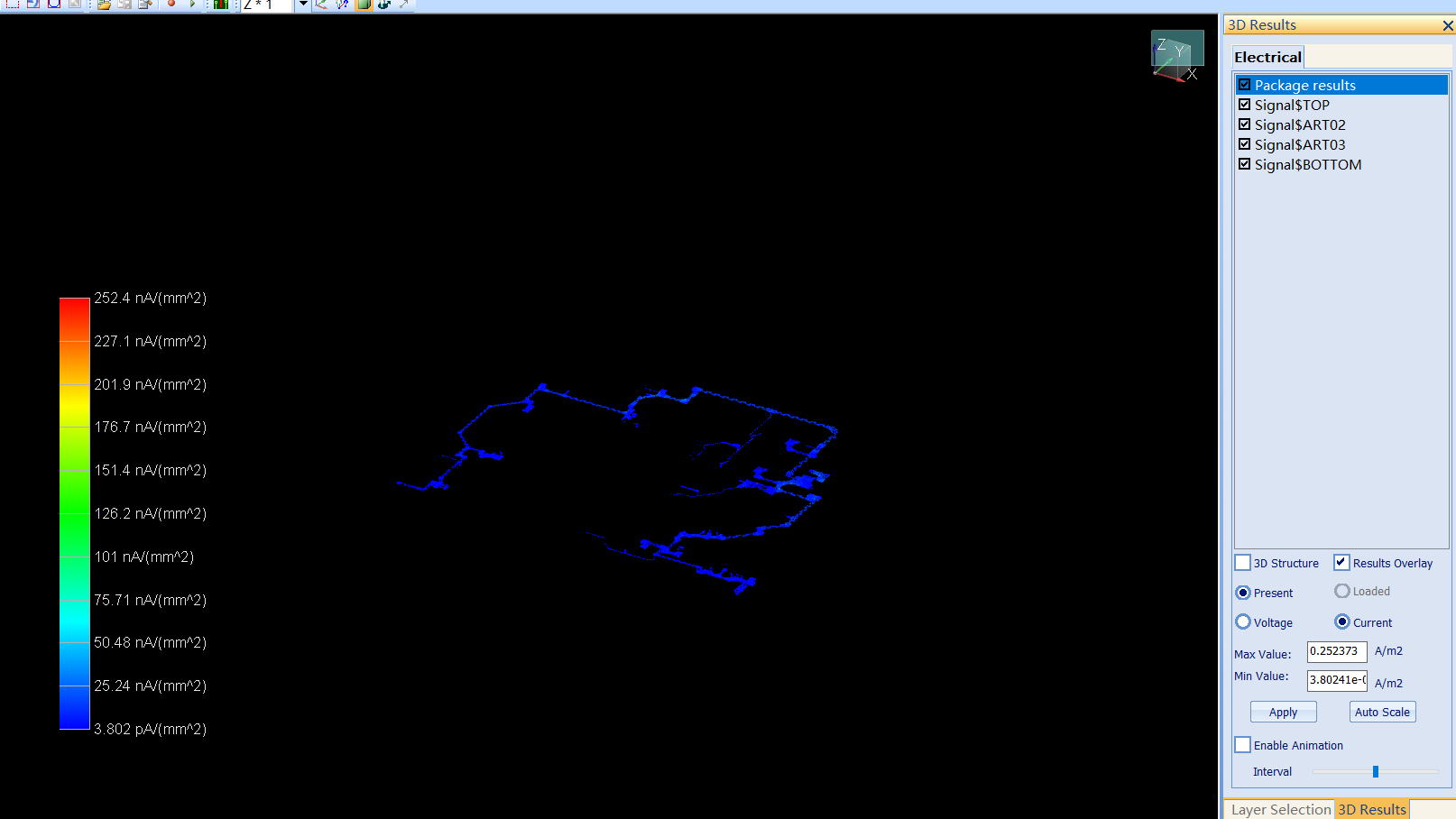

三维电流分布:

三维过孔电压:

仿真结果基本就是这样,还可以生成报告,并且打印成pdf。

再补充一下,刚打开板子可以把右下角的都勾上,另外可以去掉view actie layer,这样可以查看整版情况。

还有,刚打开板子,默认所有的net都是enable的,可以全都disenable,然后选择自己关注的网络enable即可。

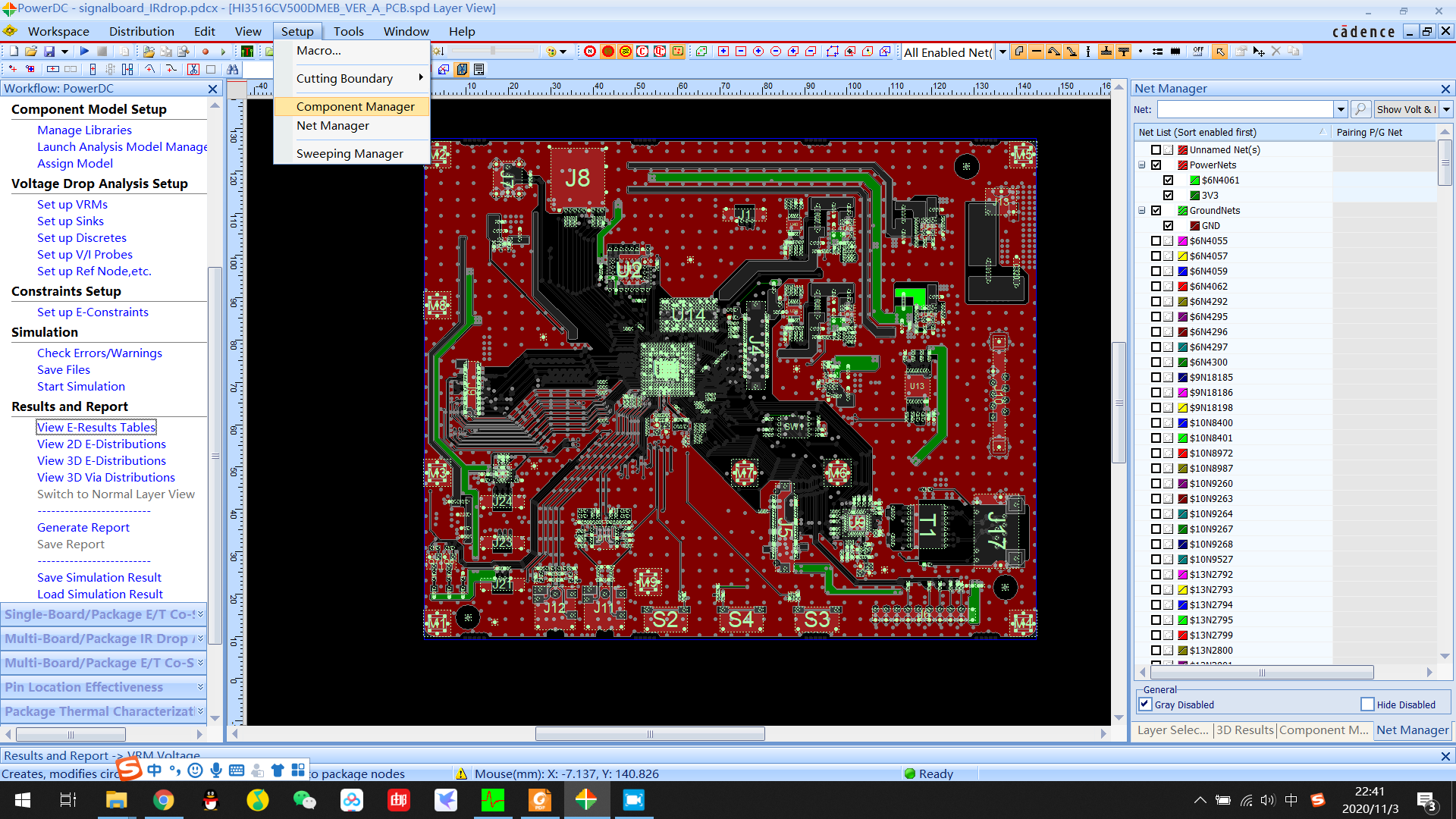

另外,右下角要是没有componet manager的话,可以这样操作:setup-->componet manager

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...