简单地说,先从PCB板厂拿到想要的参数后,输入不同的线宽,试出50Ω阻抗,此时的线宽就是我们需要的。

以下是一个八层板的例子。

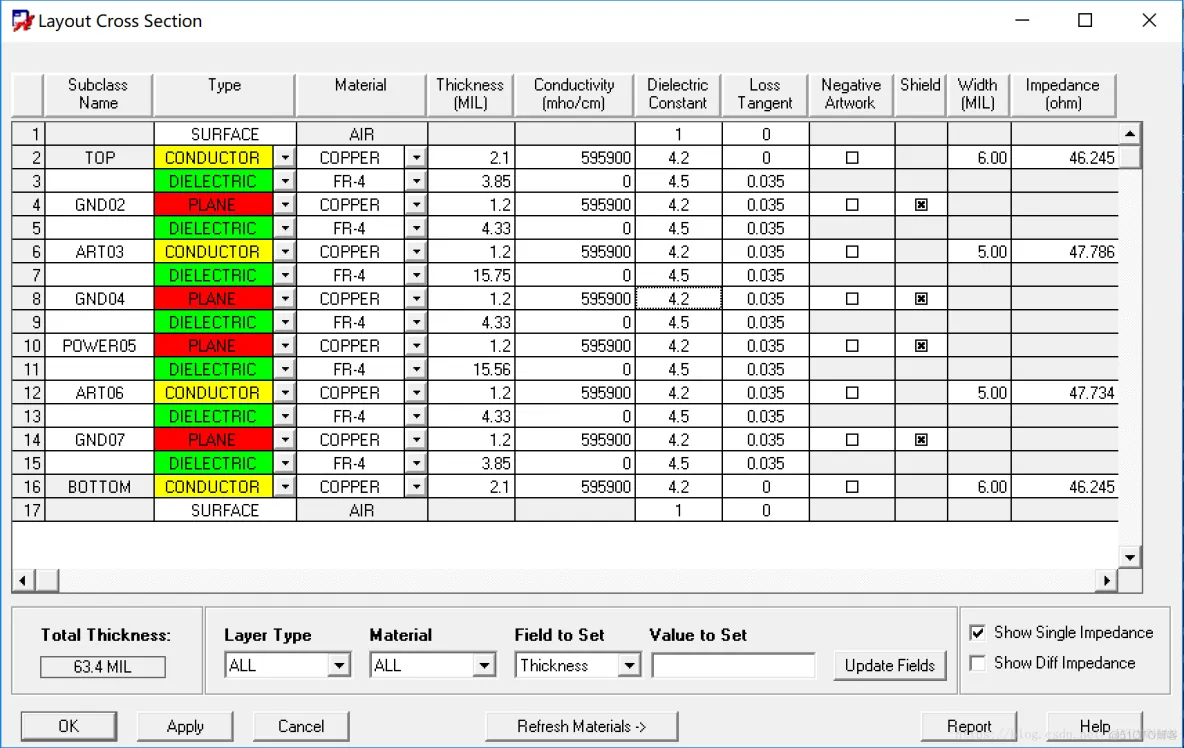

在Allegro中点击Setup -> Cross-section,可以看到下图的界面。

上图中勾选了Shield和右下角的Show Single Impedance,可以显示每一层的单线阻抗。

先以Top层为例:

Top层:Material选COPPER,Dielectric Constant(介电常数)为4.2,Thickness参数s PCB板厂提供的。

与TOP相邻的DIELECTRIC(介电层):Material一般为FR-4,Thickness参数是PCB板厂提供的,Dielectric Constant(介电常数)为4.5。

当线宽为6mil时,Allegro计算出的单线阻抗为46.245Ω。

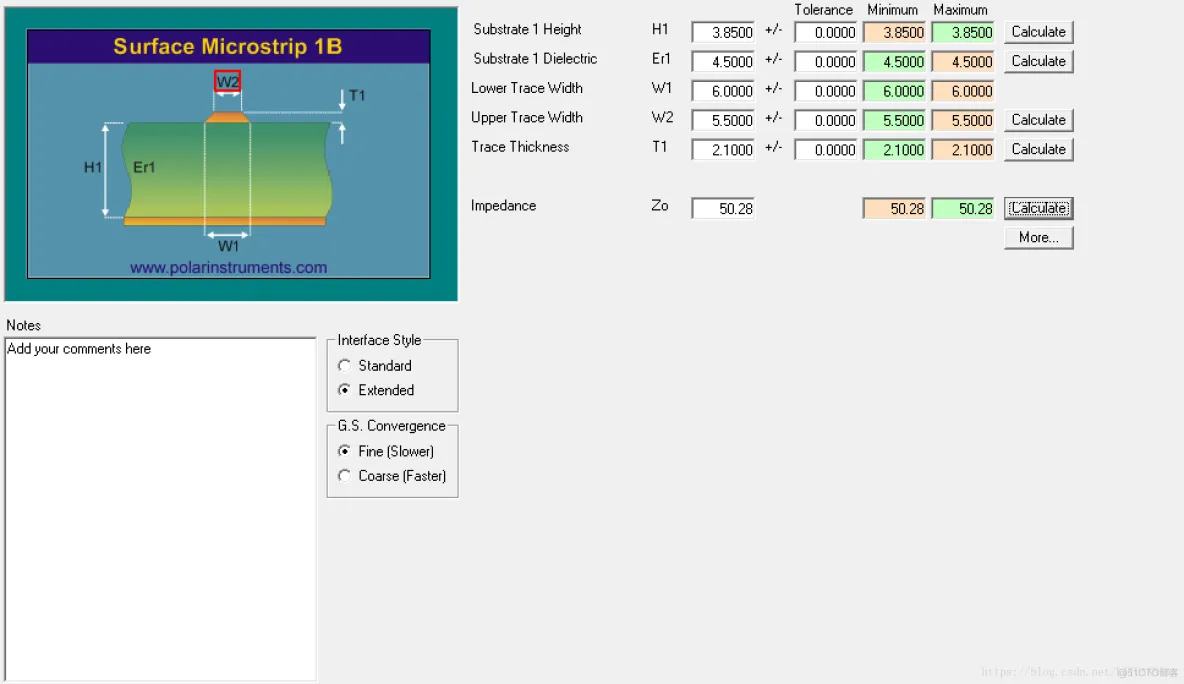

下面用Si9000计算相同参数条件下的阻抗值,以对比单线阻抗的差值。

上图中可以看出,当线宽为6mil时,Si9000计算出的单线阻抗为50.28Ω,Allegro和Si9000的计算结果差别不太大。

上图中的几个参数的含义如下:

| 参数 | 含义 |

| H1 | 介质1厚度,上图设置为3.85mil |

| W2 | 阻抗线的线面宽度,按W2=W1-0.5mil计算,上图设置为5.5mil |

| W1 | 阻抗线的线底宽度,一般说的线宽就是指W1,上图设置为6mil |

| Er1 | 介质层介电常数,FR4板材的Er=4.2 |

| T1 | 铜厚(包括基板铜厚+电镀铜厚),上图设置为2.1mil |

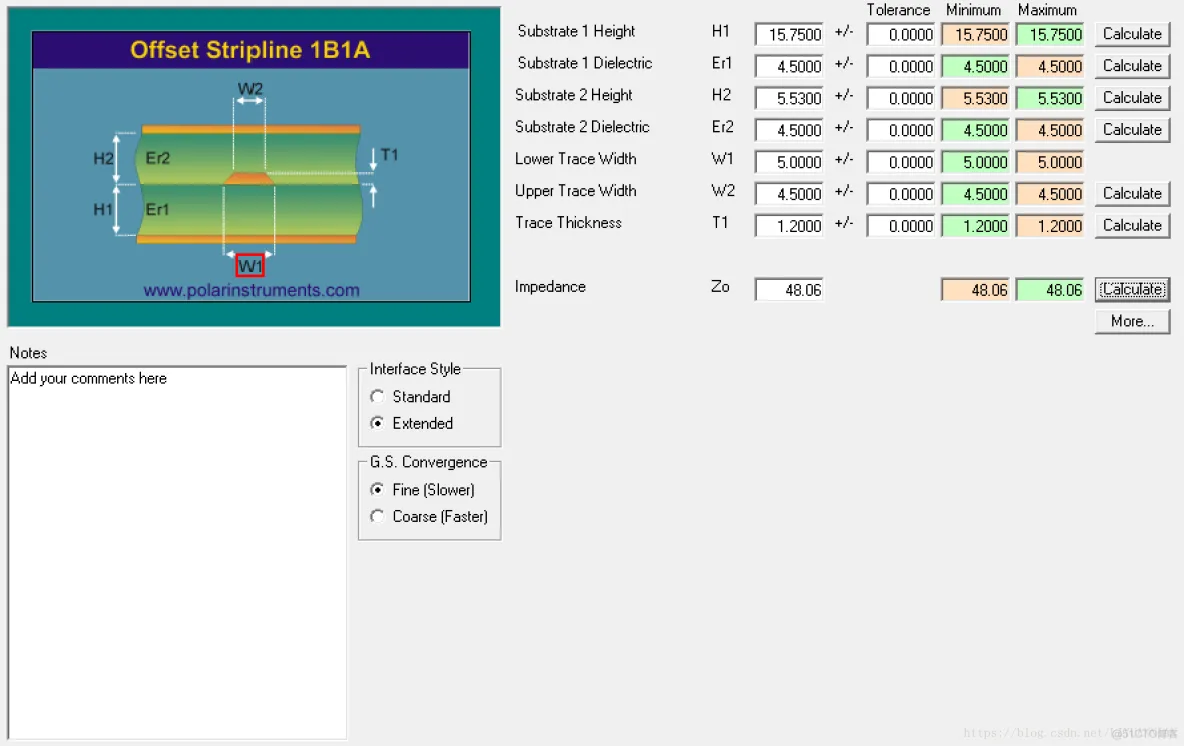

再以ART03层为例:

第1个图中可以看出,Allegro计算出的ART03层的单线阻抗为47.786Ω,下面用Si9000计算相同参数条件下的阻抗值,以对比单线阻抗的差值。

上图中H2的值设定为:ART03层厚度+ART03层上面介质层厚度=1.2mil+4.33mil=5.53mil,可以看出,当线宽W1为5mil时,Si9000计算出的单线阻抗为48.06Ω,Allegro和Si9000的计算结果差别不太大。

经过对比测试可以看出,Si9000计算出的阻抗要比Allegro计算出的阻抗稍大一点。

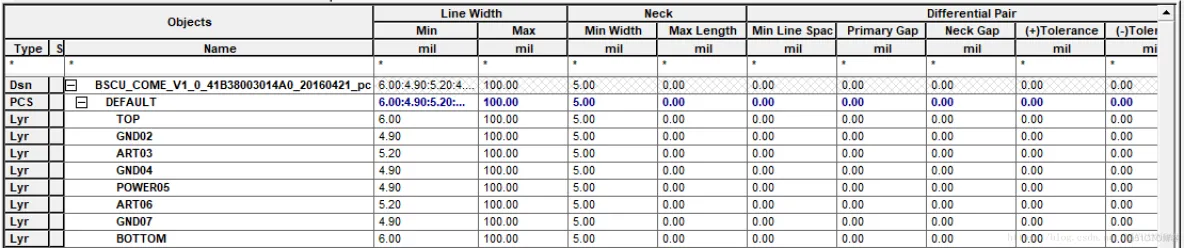

另外,拿到Top层和ART03层的单线线宽后,就可以以它们为依据,在Setup -> Constraint -> Physical -> Physical Constraint Set -> All Layers中设定Top层和ART03层默认的Line Width和Neck Width。

如下图所示:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。