原文链接:https://blog.csdn.net/qq_39299370/article/details/109580331

Cadence allegro设置差分线

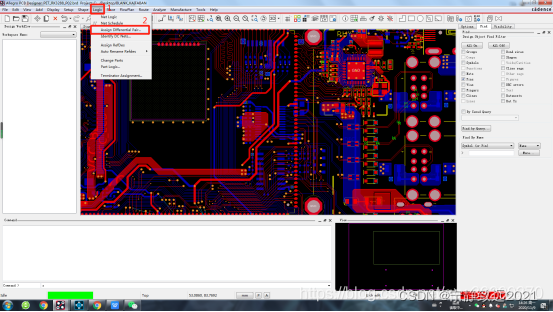

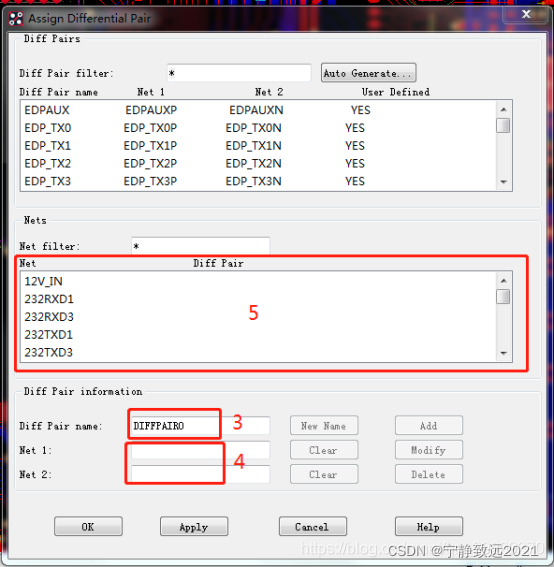

分配差分对,如下:

3 处更改差分对名字;

4 处为差分对网络,在5 处选择两个网络即可。

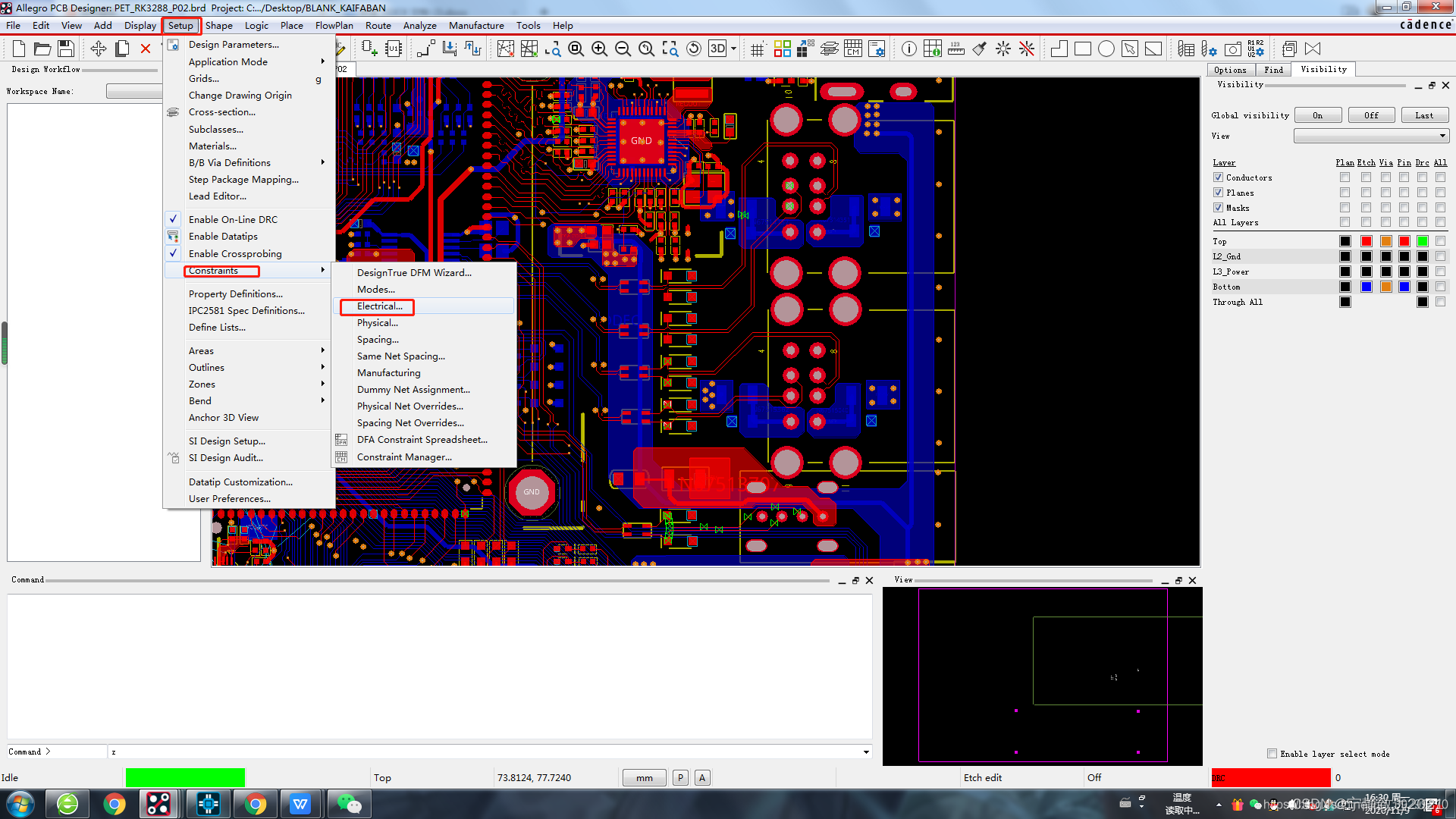

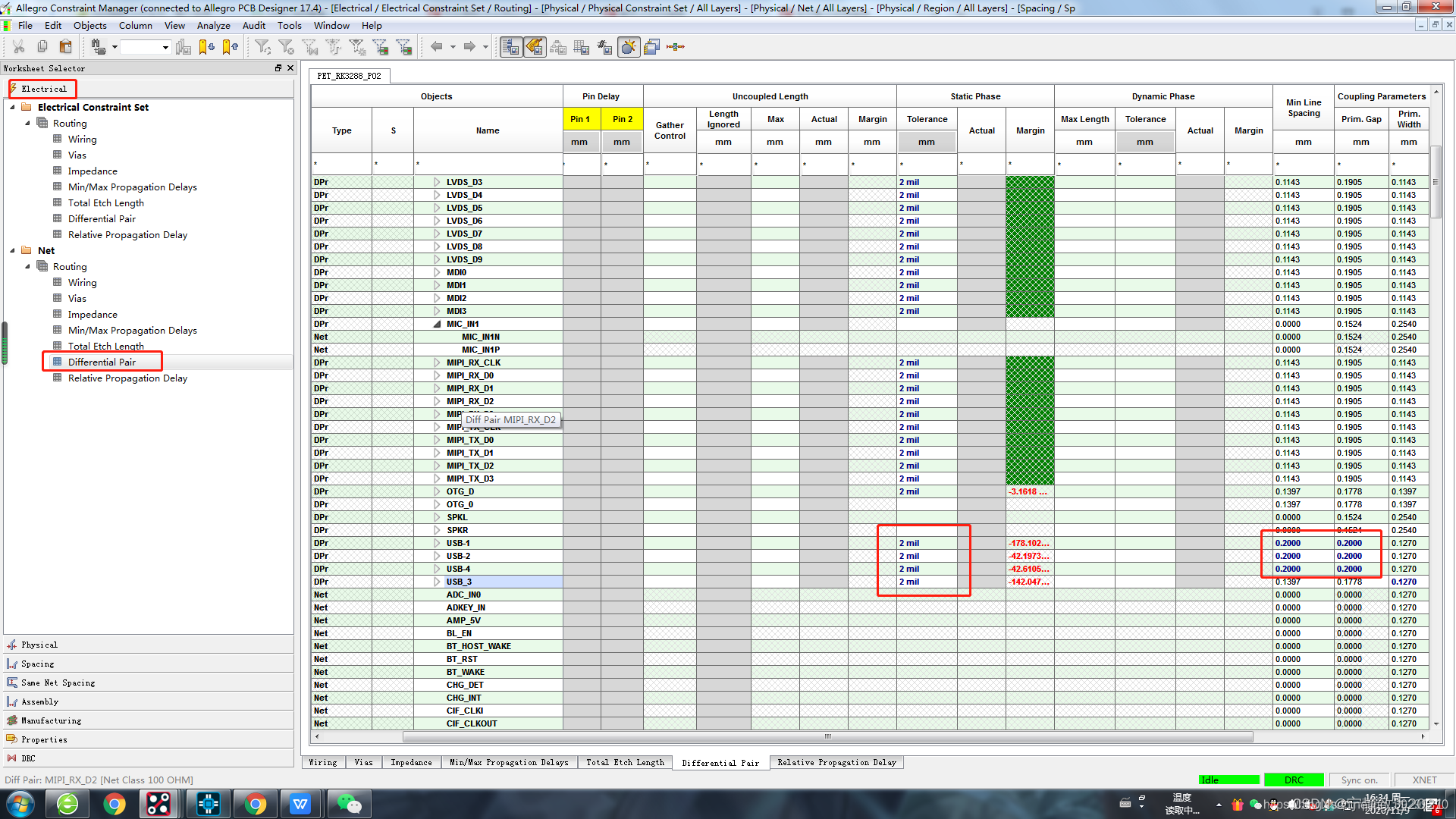

差分线间距设置:

约束管理器→ Electric →Net→routing→Differential part

Primary Gap 差分对最优先线间距(线到线间距)

Primary width 差分对最优先线线宽(线的粗细)

走线长度不等长时,选取蛇形走线。

想要单根蛇形走线,右键鼠标选择Single trace mode。

原文链接:https://blog.csdn.net/weixin_34875640/article/details/112416547

在PCB设计中由于叠构变更,导致 阻抗 的参数发生变化,如果是单端线,只需要改变线宽即可。如果是差分线,我们普遍的做法是先改变线宽,然后再去推挤,非常麻烦。今天分享一个新技能,如何快速调整差分对的线宽线距:

1.单独快速调整某一对差分线宽线距

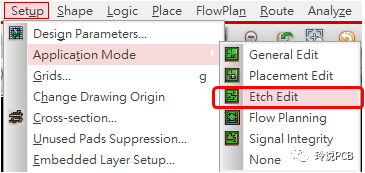

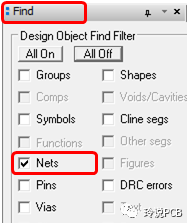

a.setup—Application Mode—Etch Edit,进入走线模式,Find只勾选Nets.

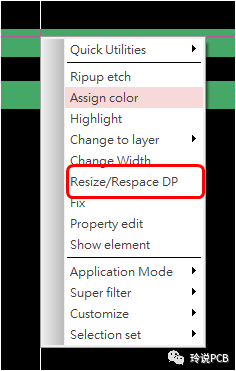

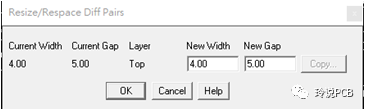

b.鼠标移到差分对上,右击,弹出如下 对话框 ,点击Resize/Respace DP。

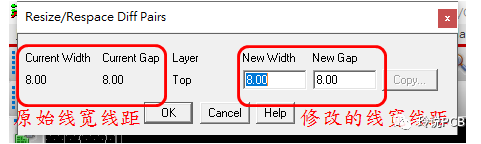

c.输入修改后的线宽线距,点击OK后线宽线距自动修改。

2. 调整多对差分线。

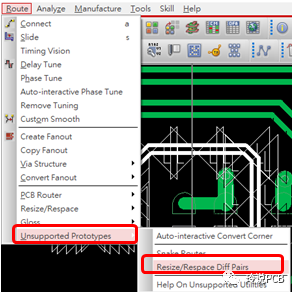

同样在走线模式下,点击Route—Unsupported Prototypes—Resize/Respace Diff Pairs,右键选择Temp group,点击需要修改的差分线,选择complete,同前面的修改步骤,所有的差分线都修改好了。

注意事项:

请先在ConstraintManager设置好线宽线距再执行此命令。

有了这个指令,效率提高很多,有用就请小伙伴点赞吧!

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删