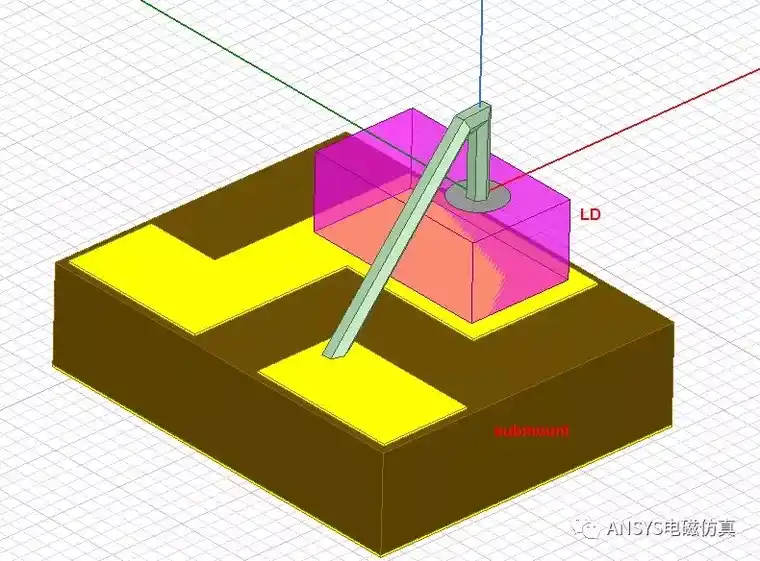

光模块TOSA的最后一个器件是LD,承载LD的submount设计也很关键,如果设计的submount本身带宽不足,前面的高速电路优化的再好也是白费功夫,正所谓行百里者半九十,深入了解自己设计的submount性能,才能整体把控模块性能。

submount各家有各家的设计方法,有基于传输线结构设计的,也有基于微小型非传输线结构设计的,不管是哪种设计方法,衡量其性能好坏的唯有插入损耗IL(3dB损耗带宽),那么该如何分析submount的带宽呢?

基于3D model的HFSS当然也是可以的,只是3D仿真的时间通常都较长,尤其是全波性能分析更费时间,如果要快速出结果,要另辟蹊径,使用Q3D+Designer的组合,正是一种又快又准的好方法。

Q3D提取submount寄生参数:

1、随意建立一个submount的模型,尺寸不限,由于是差分信号输入,因此需要建立两组source和sink,仿真结束后,可以直导出模型的HSPICE模型,不导出亦可,现在Designer支持直接导入Q3D工程模型。

2、Designer中导入HSPICE模型,分析S21,建立电路图如下:

.jpg)

从SDD21曲线可以看出,当前的submount带宽远大于25GHz,然而不要高兴的太早!!

.jpg)

加入bonding wire后的插入损耗:

submount通常跟FPC或PCB用bonding连接,如果在电路中加入bonding wire的寄生电感,又变现如何呢?如下图,在电路中加入电感L1,对它做参数扫描,电感值从0.1nH到1nH变化,步进step=0.2nH:

.jpg)

如果信号的上升沿时间tr=16ps(28Gbps速率),那么高速通道需要的最小带宽为f_min>0.35/16ps=21.875GHz,按下面的仿真IL来看,使用的金线电感不能超过0.7nH,超过0.7nH,通道的3dB带宽就小于21.875GHz,同时为了设计的余量,最好控制金线电感不超过0.5nH。

.jpg)

金线电感不超过0.5nH,长度如何控制?

如下单根0.22mm金线(直径25um)寄生电感为0.17nH,单位长度电感为0.17/0.22=0.77nH/mm,L_max=0.5/0.77=0.649mm,也就是控制电感值在0.5nH以内,金线长度不能超过649um。

.jpg)

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...