最近几年随着人工智能芯片在中国雨后春笋般的蓬勃发展,人工智能芯片以其设计规模、设计复杂度和先进设计方式引领数字芯片设计行业。特别是3D IC的采用,使得人工智能芯片的性能功耗比又上了一个台阶。但采用最先进的设计方法进行复杂的芯片设计也往往伴随着诸多挑战。

人工智能芯片的一个重要设计指标是用TOPS(Tera Operations Per Second)Per Watt来衡量。人工智能芯片设计为了追求高能效比,在设计上除了会采用最先进的芯片制造制程,一般也会采用比较先进的芯片设计架构,比如最近几年被高性能芯片设计广泛采用的3D IC设计。

虽然3D IC设计目前还有很多挑战,但其设计相对传统的芯片封装来说,芯片规模更大(支持3000以上pin脚),信号通道更短,支持HBM(High Bandwidth Memory)等,因此对芯片性能的提升是比较显著的。

在芯片制程开发难度不断加大和迫近制程极限的情况下,针对这种典型的人工智能芯片,会面临如下挑战。

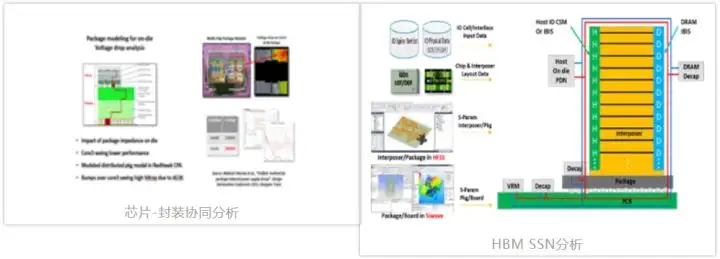

首先是功耗噪声。人工智能芯片一般功耗都比较大,在相同算力情况下,如果功耗小,无疑会更受市场青睐。如何在芯片设计阶段降低功耗是AI芯片设计的一大挑战。另一方面,AI推理或训练芯片要求芯片能从功耗很低的休眠状态(sleep mode)以极快的速度切换到功耗很高的全速处理状态(operation mode),因此电源供电必须能提供这种瞬态切换所需要的大电流,不能出现供电过冲(overshoot)或塌陷(undershoot)而造成的电压剧烈抖动。为防止这种情况的出现仅仅依靠芯片内部的电容是不足够的,还必须审慎选择interposer、封装和PCB板上的去耦电容,以协同设计的方式来保证供电网络(PDN)满足瞬态电流消耗需求。

其次是HBM设计的挑战。HBM相对于传统DDRx设计来说有更高的带宽和功耗效率,时延很低,占用面积小的特点。如果采用相似的带宽和存储大小的情况下,GDDR6的PCB占用面积是HBM2的6倍,功耗消耗多3倍,芯片设计面积接近2倍,HBM的优势比较明显。但是HBM设计实施却很困难,除了满足严苛的interposer设计规则及信号完整性规则外,还必须考虑高位宽(1024 bits或2048 bits)同步开关噪声问题。技术的发展趋势要求我们重新审视集成电路设计与验证的方法学。

Ansys eco-platform提供了从前端到后端、模拟到数字、芯片到系统的功耗、高速数据传输和可靠性解决方案。通过Ansys eco-platform提供的解决方案可以极大地帮助设计者优化设计性能,降低成本,缩短设计周期和减少设计者工作量,从而确保具有最新技术和创意的产品及时上市并占领市场,保护设计企业的利益。

解决方案

针对上述人工智能芯片在功耗、噪声及可靠性方面的挑战,采取有效的应对方法可以帮助设计者规避潜在的设计风险。Ansys可提供业界最全面的功耗、电源完整性、信号完整性及可靠性仿真解决方案。主要涵盖如下场景:

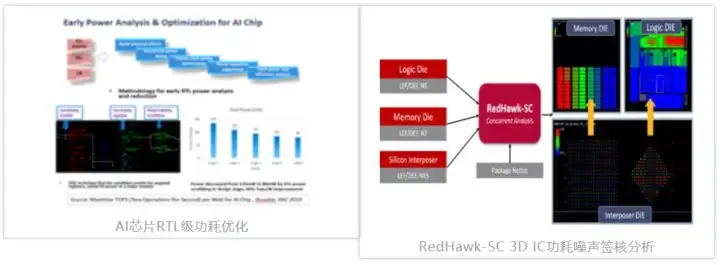

1、RTL级功耗分析及优化

Ansys PowerArtist集成了先进的功耗分析方法和自动的功耗优化技术,可以顺利实现功耗收敛,可有效地优化60% 甚至更高的冗余功耗。

2、高性能AI芯片的电源及可靠性核签分析

Ansys RedHawk-SC基于Seascape大数据分析平台,可以帮助客户顺利实现大规模高性能AI IC设计功耗、噪声及可靠性签核分析。

3、高速接口分析

CSM、CPM结合HFSS和SIwave提供全面的HBM及Serdes高速接口信号和电源完整性分析。

4、3D IC热及可靠性分析

3D IC热及结构可靠性分析。RedHawk-SC-Electrothermal结合Icepak及Ansys Mechanical 可以准确的帮助客户仿真3D IC散热及热应力带来的挑战。

Ansys是业界唯一一家可以提供针对高性能IC设计功耗、噪声及可靠性仿真的多物理场仿真方案提供商

高性能集成电路设计的挑战,要求设计者的观念从对芯片、封装和电路板孤立地分析向更加系统化全面分析的多物理场(Multi-physics)解决方案转变。例如,针对低功耗、高性能以及更严格设计规范的要求,将芯片、封装和系统(CPS)作为统一的相互影响的网络进行分析,这对于保证电路整体系统正常工作十分重要。

Ansys是业界唯一一家可以全面提供芯片设计前端到后端、模拟设计到数字设计、芯片级设计到系统设计的功耗、噪声、时序及可靠性等分析解决方案的EDA厂商。当前,在半导体设计领域排名Top20的公司,都已采用Ansys产品。Ansys的芯片电源噪声及可靠性解决方案已帮助客户完成万次以上的芯片流片成功。

典型应用案例

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...