软件

产品

目的:使用cadence ADE仿真遇到不收敛解决方案—针对dc和tran仿真。

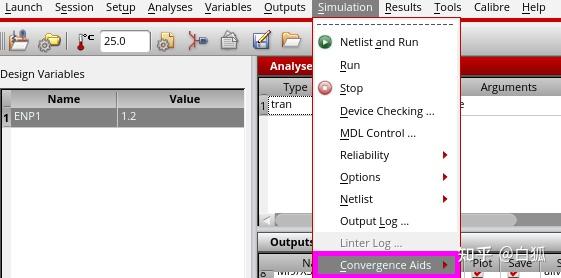

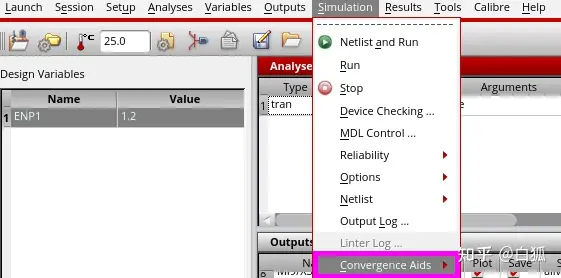

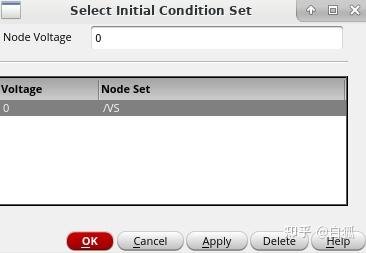

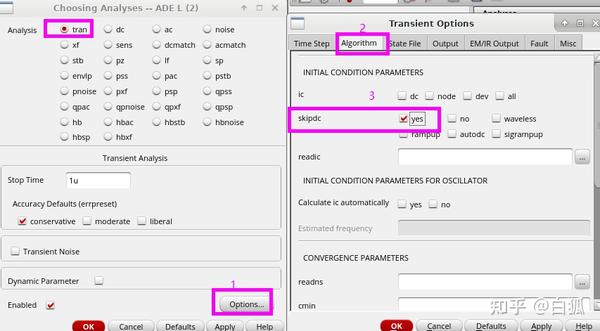

第二:使用tran仿真直接跳过去dc初态,如下:

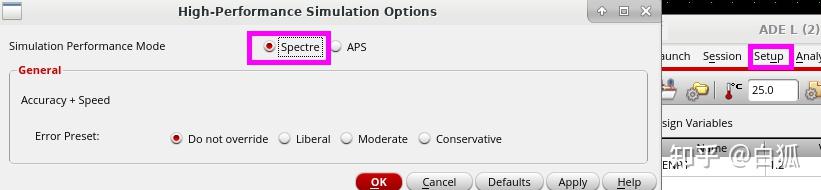

第三:ADE仿真中选择“Spectre”

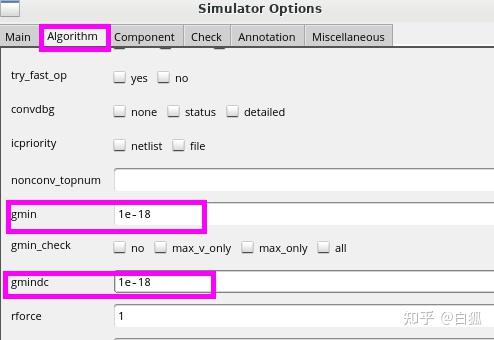

第四:修改gmin和gmindc的精度

Simulation→Options→Analog...→Algorithm→gmin和gmindc,可以将精度稍微改大些,如1e-15。

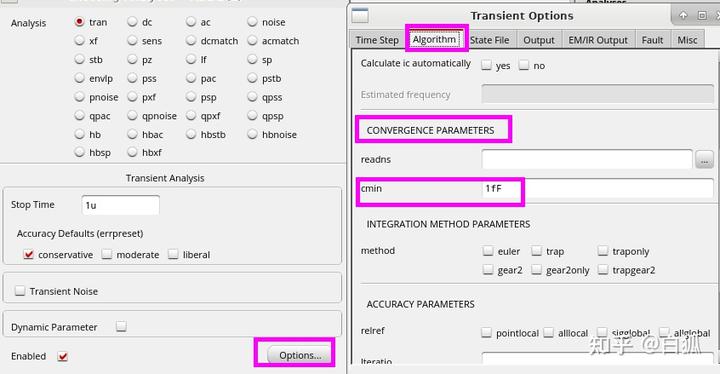

第一:给cmin加1fF电容

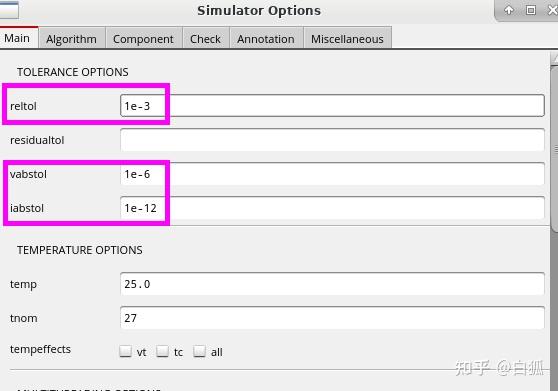

第二:修改reltol和vabstol和iabstol的精度

Simulation→Options→Analog...→Main

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。