引言

热阻值用于评估电子封装的散热效能,是热设计中一个相当重要的参数,在IC封装之前,对热阻的评估均至关重要,目前半导体使用的散热软件多数集中于ANSYS ICEPAK,ICEPAK提供了半导体领域丰富的封装模型,比如 SOP、QFP、QFN、FCBGA、WBBGA等,同时ICEPAK提供了自然对流和强制对流的JEDEC测试环境。仿真精度的准确度与JEDEC测试板子息息相关,ICEPAK提供了等效PCB测试板子,为了验证ICEPAK的JEDEC等效测试板子与实际JEDEC布线板子的仿真差异,文章对二者进行了分析。从文章脉络上看,文章首先介绍半导体封测的常用JEDEC标准,其次引进热阻的概念及分类,最后以引脚类JEDEC测试版为例,分析了JEDEC等效测试板子与实际JEDEC布线板子的仿真差异。

Part.1 ICEPAK简介

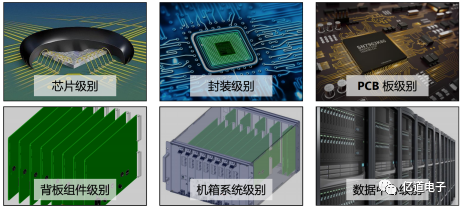

ANSYS Icepak是一款基于Fluent求解器的电子散热分析软件,是针对电子热设计,涵盖芯片级、板级、系统级、环境级全系列解决方案的高精度分析专业软件包。ANSYS Icepak被广泛应用于航空航天、能源电力、电力电子、铁路机车消费品电子产品、医疗器械等各行各业电子产品的研发和设计过程。

图1.1 ICEPAK 全面的散热解决方案

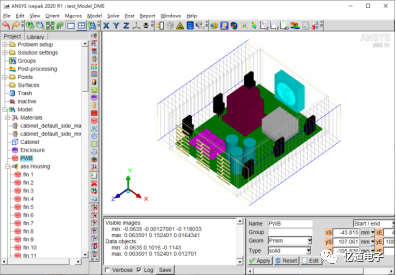

ANSYS Icepak软件包含丰富的模型库及材料,能够快速创建和模拟集成电路(IC)封装、印刷电路板和完整电子系统的电子元件散热模型。只需拖拽预定义的模型对象(包括机柜、风扇、包装、电路板、通风孔和散热器)的图标,即可创建模型,从而创建完整电子系统的模型。

图1.2 ICEPAK 快速建模功能

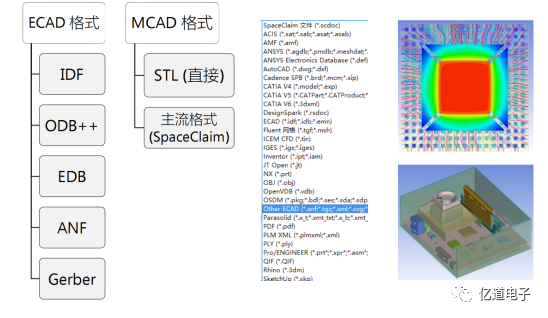

ICEPAK配合三维建模软件Spaceclaim,支持丰富的接口,可导入ECAD,MCAD文件,实现精确建模分析。

图1.3 ICEPAK 丰富的导入功能

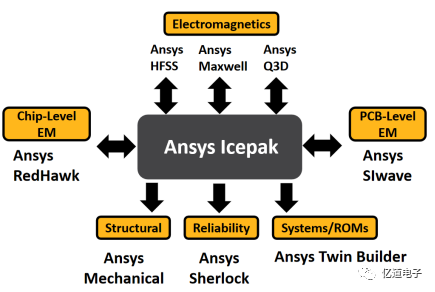

利用Workbench平台下丰富的功能模块, 搭建上下游工作实现多物理场分析,如电热分析耦合,电热力耦合分析。

图1.4 ICEPAK 全面的多物理场解决方案

Part.2 JEDEC热测试标准

JEDEC(Joint Electron Device Engineering Council)是一个推动半导体元器件领域标准化的行业组织。半导体制造商以及电力电子领域的从业者不可避免地会涉及到很多行业标准。作为大原则,无论热相关的项目还是其他项目,其测试方法和条件等都要符合行业标准。在JEDEC标准中,与“热”相关的标准在封测领域使用JESD51,JESD51系列包括IC等的封装的“热”相关的大多数标准,主要使用的JESD51标准如下:

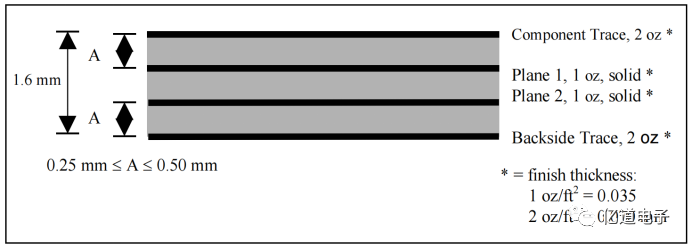

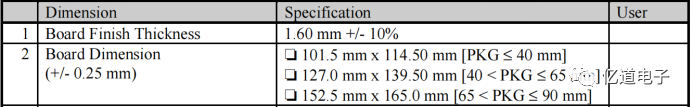

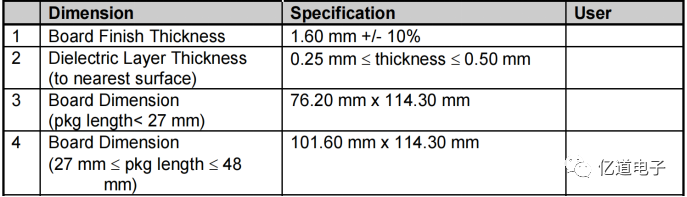

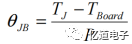

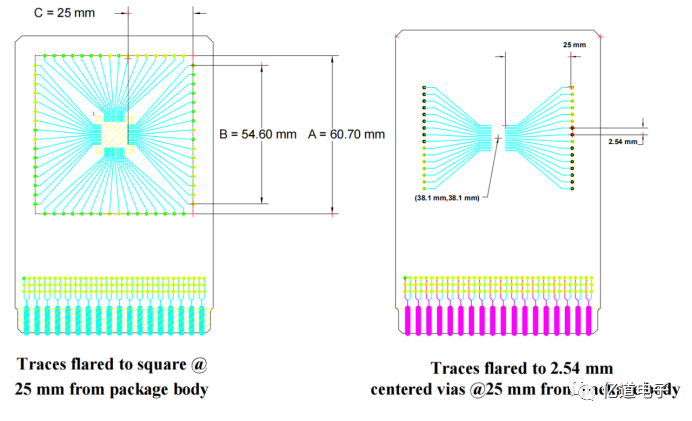

JESD51-3/5/7中规定了通常被称为“JEDEC板”的电路板。下面以JESD51-7为例:

图2.1 JEDEC 2S2P测试版

表2.2 Leaded Surface Mount 尺寸要求

表2.3 Surface Mount Package 尺寸要求

Part.3 热阻定义

在1980年代,封装的主要技术是利用穿孔(through hole)方式将组件安装于单面镀金属的主机板,IC组件的功率层级只有1W左右,在IC封装中唯一的散热增进方式是将导线架材料由低传导性的铁合金Alloy42改为高传导性的铜合金。

随着技术的提升,从1990年代开始,半导体及电子封装技术已经有了很大的进步,为了增加组装密度,组件的安装方式采用表面粘着(surface mount)技术,虽然机板采用更多电源层的多层铜箔的机板,然而所产生的热传问题却更为严重。为了增加封装的散热效能,开始将金属的散热片(heat spreader)插入封装之中。在1990年代晚期,BGA(Ball Grid Array)的封装型式开始发展,由于面数组的方式可容纳更多的锡球作为I/O,因此封装的体积大量缩小,而相对的机板的I/O线路也越来越小,使封装技术朝向更进一步的演进,产生的热传问题也较以往更为严重。

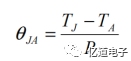

近年来由于电子产业的蓬勃发展,电子组件的发展趋势朝向高功能、高复杂性、大量生产及低成本的方向。组件的发热密度提升,伴随产生的发热问题也越来越严重,而产生的直接结果就是产品可靠度降低,因而热管理(thermal management)相关技术的发展也越来越重要。电子组件热管理技术中最常用也是重要的评量参考是热阻(thermal resistance)。早期的电子热传工业标准主要是SEMI标准,该标准定义了IC封装在自然对流、风洞及无限平板的测试环境下的测试标准。自1990年之后,JEDEC jc51委员会邀集厂商及专家开始发展新的热传工业标准,在半导体领域,采用JEDEC的热阻有三种θja,θjb和θjc 。

图3.1 典型的热设计位置图

θja是在一立方英尺密封外壳中测量的自然对流连接到环境空气的热阻,其定义如下:

θjb是连接到板的热电阻,其中TBoard是使用2s2p板在元件引线上或附近测量的温度,对于leaded package,热电偶连接在引线的脚上。对于surface mount package,热电偶附着在封装体1毫米以内的线路上。

θjc即θjcx为结壳热阻。x表示测量TCase的壳体表面,在θjcx测量过程中,热量被迫流经该壳体表面,top表示顶面,bot表示底面。所使用的表面通常是封装传热路径中的表面,通常是封装的顶部表面。

Part.4 JEDEC 2S2P测试板仿真对比

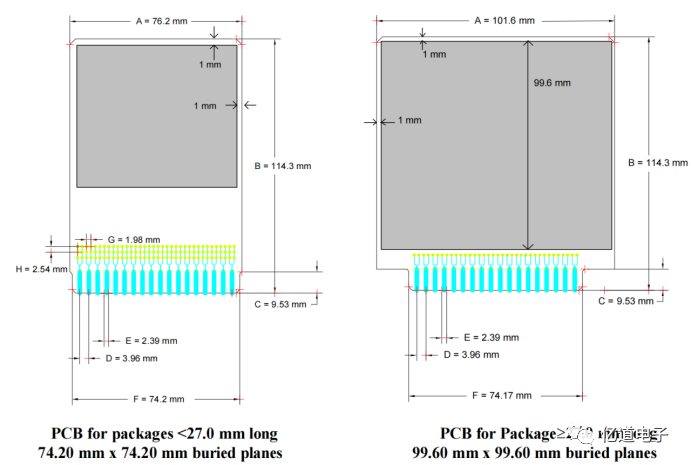

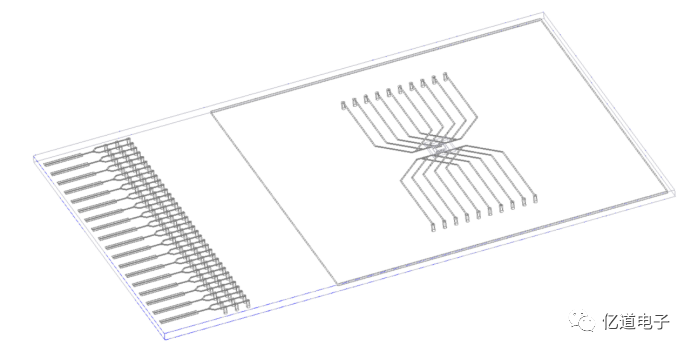

以10 leaded package为例,建立实际JEDEC 2S2P测试板与ICEPAK中JEDEC 2S2P测试板等效板子,二者进行对比分析,分析芯片最高温度Tj,以及热阻θja ,JEDEC测试版如图4.1所示和4.2所示,需要说明的是,JEDEC测试版trace个数与lead个数相匹配。实际板子和ICEPAK等效板子分别如图4.3和图4.4所示!

图4.1 Top 设计

图4.2 埋入层设计

图4.3 实际JEDEC 2S2P测试板

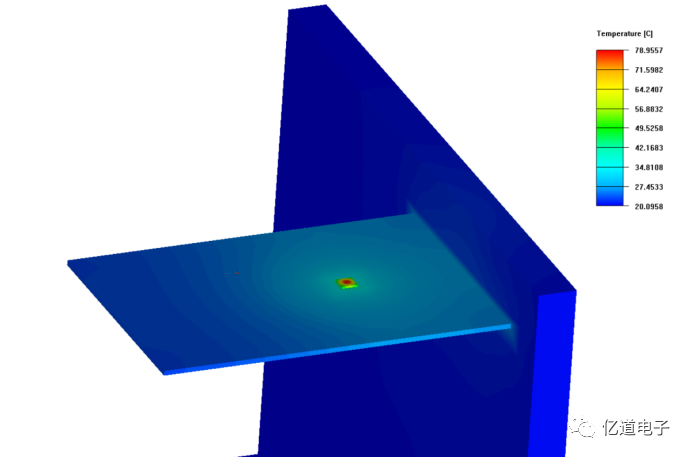

图4.4 ICEPAK 的JEDEC 2S2P等效测试板

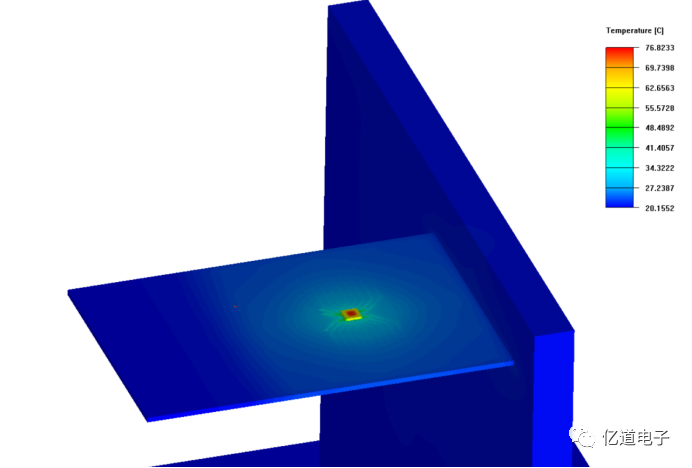

以简单的封装结构进行验证,芯片尺寸2mm*2mm*0.3mm,PAD 8mm*8mm*0.1mm,EMC CH尺寸为5mm*5mm*0.75mm.其中PAD热导率387W/m.K,EMC热导率0.98W/m.K,芯片热导率148W/m.K,功耗1W。树脂材料为FR4,热导率0.35W/m.K。ICEPAK中JEDEC板子等效参数为XY:17.9W/m.K,Z:0.38W/m.K。封装摆放位置如下图4.5所示。

图4.5 封装摆放位置

仿真结果如如图4.6和图4.7所示,从结果看,实际和等效的温度相差约2.1℃,二者温度有一定差异,但误差仅为2.7%,在可接受范围内,可见ICEPAK自带的等效PCB具有一定的精度。

图4.6 实际JEDEC板子

图4.7 ICEPAK自带等效PCB

Part.5 总结

1. ANSYS ICEPAK 具有丰富的材料及模型,具备封装级别、板级、系统级的全面解决方案。

2. 系统自带JEDEC标准环境,等效的PCB具有精度高,使用方便的特点。

3. 仿真大大节省计算时间,优化成本。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...