软件

产品

继续!

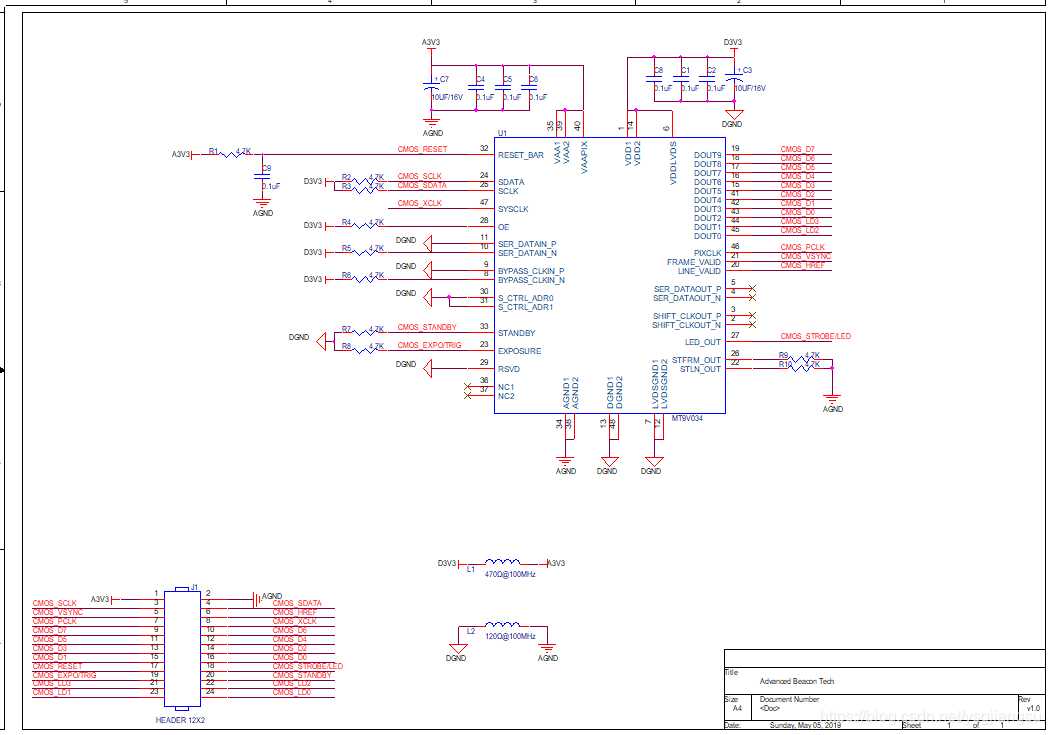

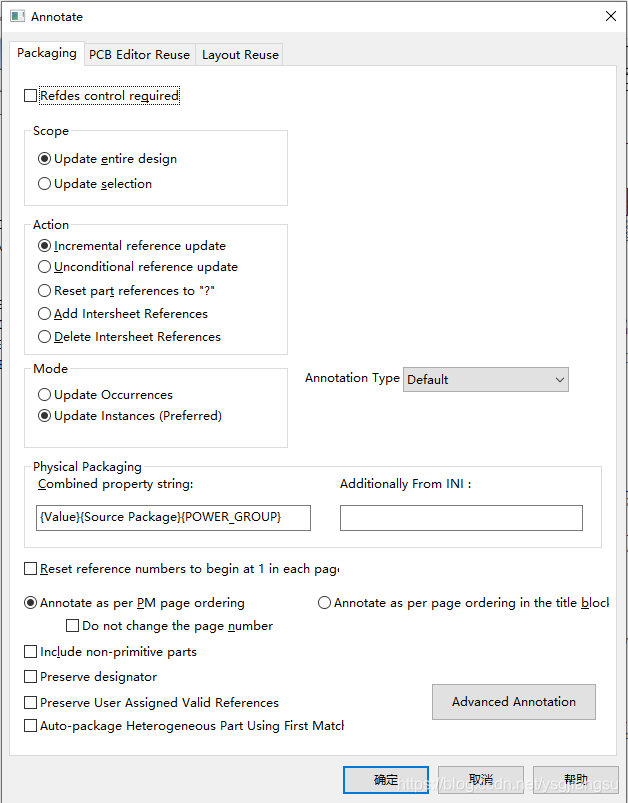

画完元件,画完封装,可以制作原理图了:

原理图具体什么内容暂且不表。

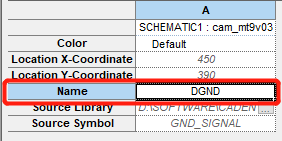

这里讲一下:用 软件 自带的CAPSYM库中的GND默认是不显示名称的。

办法:

先把名字改成你想要的名字:比如DGND

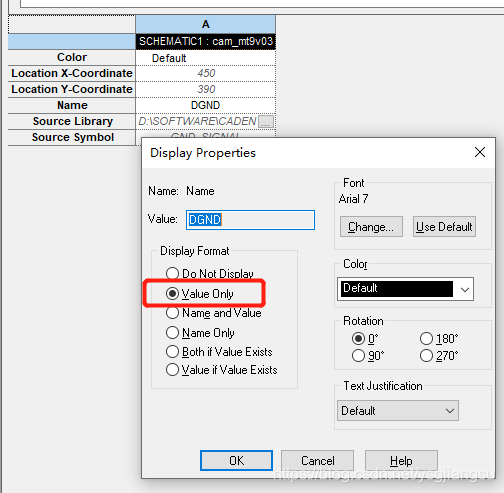

右键DGND,选择display

选择Value only,即可 解决 !

好的,继续!

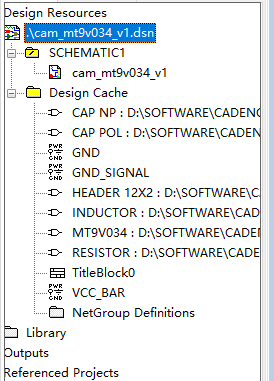

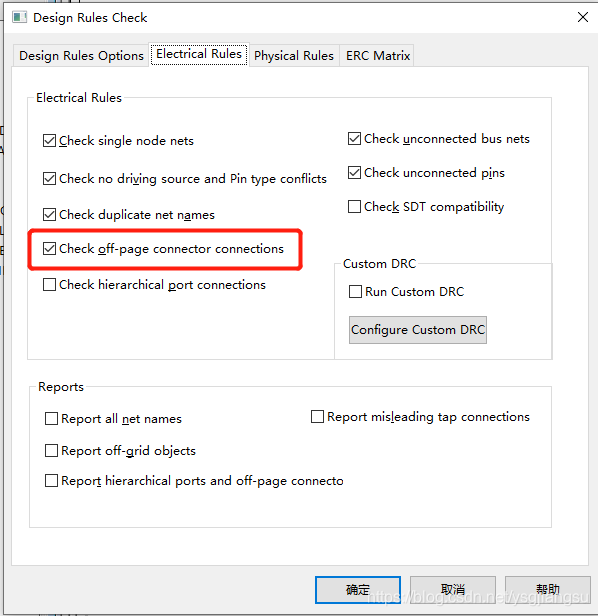

说正事,capture软件是怎么从你写的一个子串找到对应的封装的?

答案 是:它并没有找,你就是随便写一个子串都能通过电气规则检查!

********************************************************************************

*

* Design Rules Check

*

********************************************************************************

--------------------------------------------------

Checking Schematic: SCHEMATIC1

--------------------------------------------------

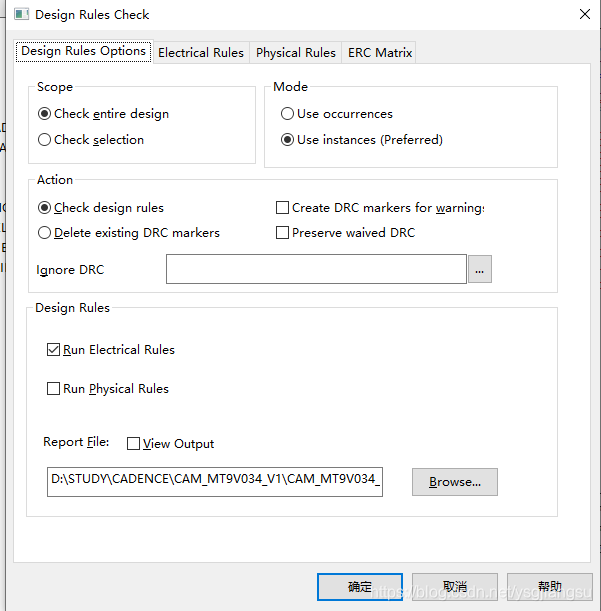

Checking Electrical Rules

Checking For Single Node Nets

WARNING(ORCAP-1600): Net has fewer than two connections CMOS_LD1

WARNING(ORCAP-1600): Net has fewer than two connections CMOS_LD0

Checking For Unconnected Bus Nets

Checking Off-Page Connections

由于我需要兼容多个 CMOS ,所以这里有两bit没有用,所以警告,可以无视。

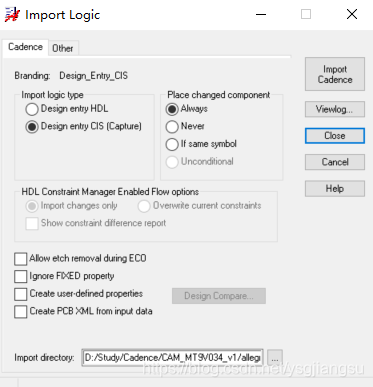

Spawning... "https://www.gofarlic.com\SoftWare\Cadence\Cadence\Cadence_SPB_17.2-2016\tools\bin\pstswp.exe" -pst -d "https://www.gofarlic.com\STUDY\CADENCE\CAM_MT9V034_V1\CAM_MT9V034_V1.DSN" -n "https://www.gofarlic.com\STUDY\CADENCE\CAM_MT9V034_V1\allegro" -c "https://www.gofarlic.com\SoftWare\Cadence\Cadence\Cadence_SPB_17.2-2016\tools/capture/allegro.cfg" -v 3 -l 31 -s "" -j "PCB Footprint" -hpath "HPathForCollision"

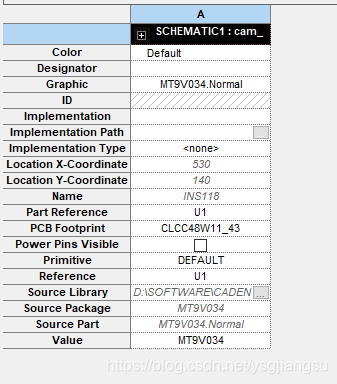

#1 ERROR(ORCAP-36002): Property "PCB Footprint" missing from instance U1: SCHEMATIC1, cam_mt9v034_v1 (134.62, 35.56).

#2 ERROR(ORCAP-36018): Aborting Netlisting... Please correct the above errors and retry.

Exiting... "https://www.gofarlic.com\SoftWare\Cadence\Cadence\Cadence_SPB_17.2-2016\tools\bin\pstswp.exe" -pst -d "https://www.gofarlic.com\STUDY\CADENCE\CAM_MT9V034_V1\CAM_MT9V034_V1.DSN" -n "https://www.gofarlic.com\STUDY\CADENCE\CAM_MT9V034_V1\allegro" -c "https://www.gofarlic.com\SoftWare\Cadence\Cadence\Cadence_SPB_17.2-2016\tools/capture/allegro.cfg" -v 3 -l 31 -s "" -j "PCB Footprint" -hpath "HPathForCollision"

INFO(ORCAP-32005): *** Done ***

说到这里,也就是说:PCB footprint压根就不会检查有效性,只会检查有无!

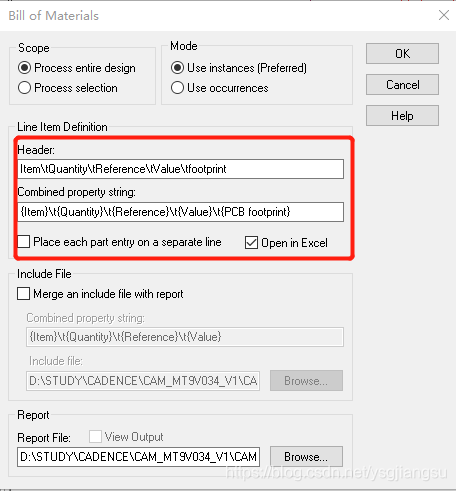

Item\tQuantity\tReference\tValue\tFootprint

{Item}\t{Quantity}\t{Reference}\t{Value}\t{PCB footprint}

好的,这样OK

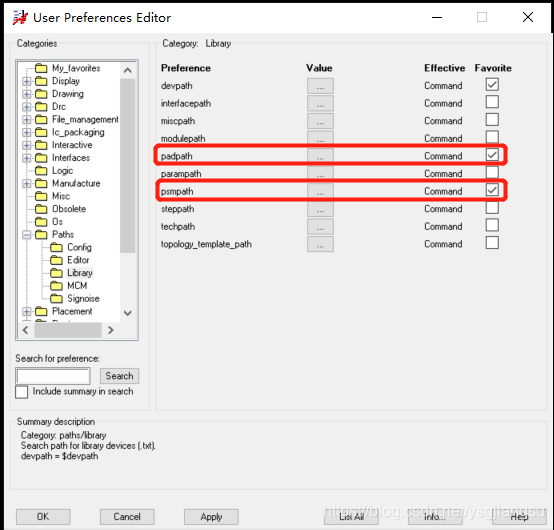

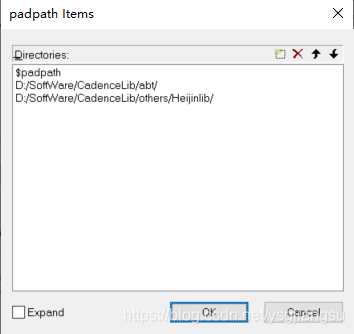

另一个软件allegro,我们 设计 封装的时候会放在某个路径下

这里的路径将影响allegro软件的封装查找,导入网表时,会按照footprint字串从库中查找对应的封装,感觉我在说废话

120Ω@100MHz,不能整中文字符,改成Ohm问题解决好了,收工!

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删