随着产品的小型化与信息化,高速信号已经进入更多的产品设计中。在进行高速 PCB 设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路越大,这些信号愈有可能吸收来自系统中任何其他网络的噪声,给高速信号带来严重的影响。

设置约束

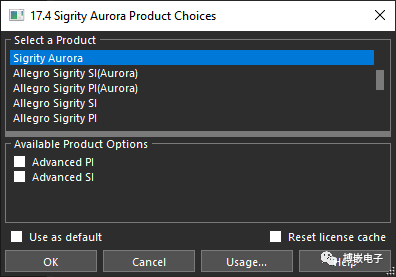

1.通过右击双击 Brain_board.brd 设计文件并选择 Sigrity Aurora 许可证来启动 Allegro PCB Editor。

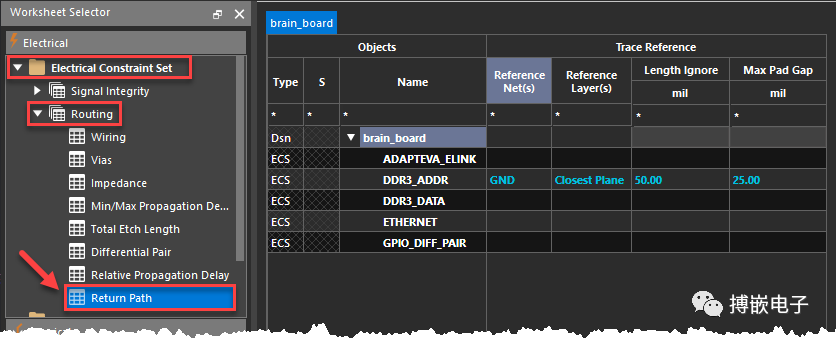

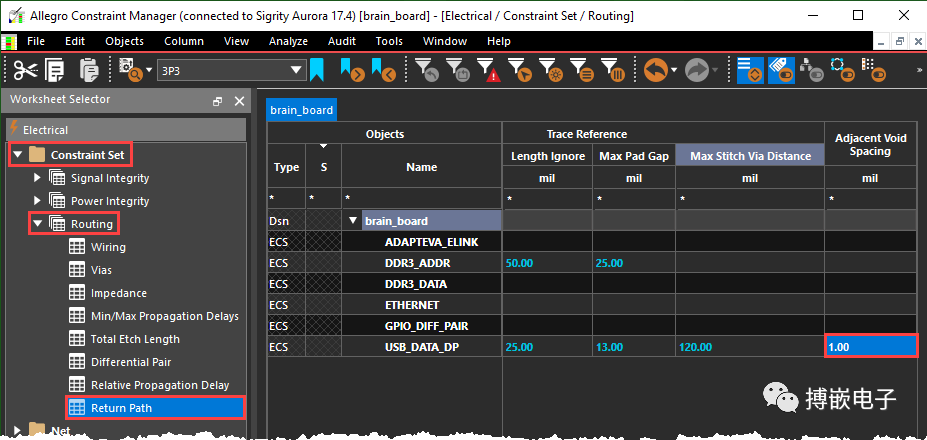

2. 打开约束管理器(Setup > Constraints > Constraint Manager)并导航到Constraint Set > Routing > Return Path工作表。

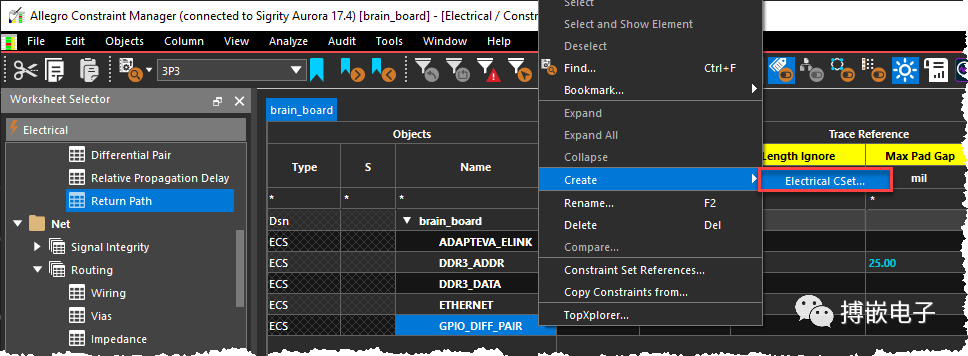

3. 在设计名称单元格上单击鼠标右键 (RMB),然后选择Create >Electrical CSet。这将创建一个新的 ECset。

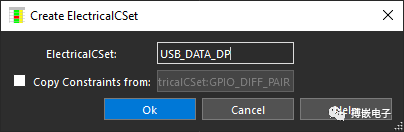

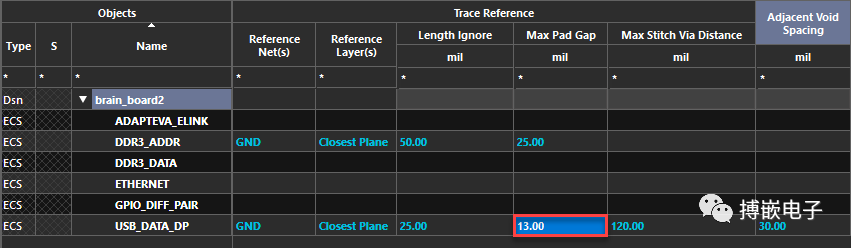

4.在 Create ElectricalCSet 对话框中,将新 ECset 的名称定义为 USB_DATA_DP 并取消选中 Copy Constraint from 复选框。此选项允许用户根据用户在 CM 上使用 右击时选择的 ECset 创建一个新的 ECset。

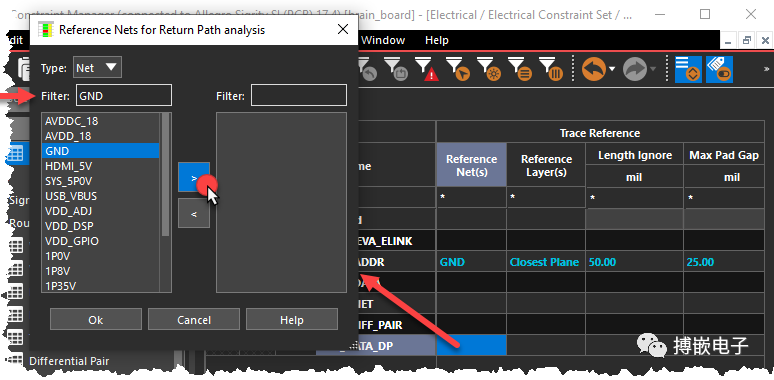

单击参考网络下的单元格,其中包含 GND。必须至少定义一个参考网络才能使返回路径检查起作用。此对话框显示具有电压属性的网络。

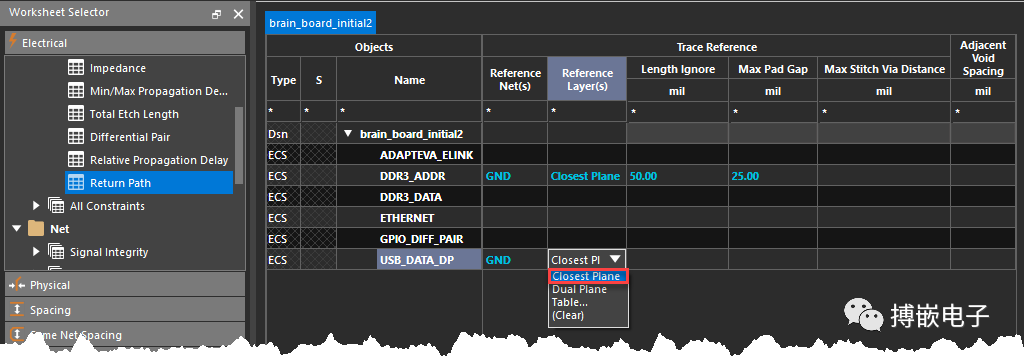

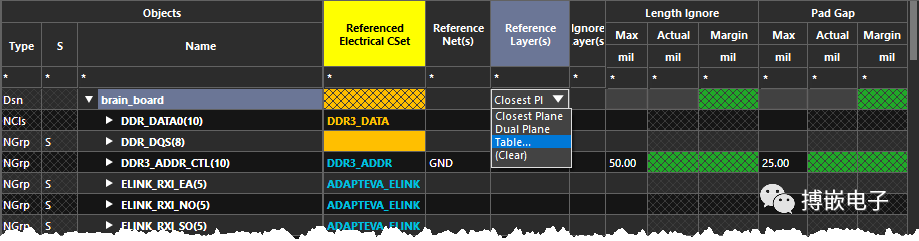

5.选择参考层的单元格并选择最近平面。这将使参考层成为最近的平面。

6.还有四个要设置的约束:

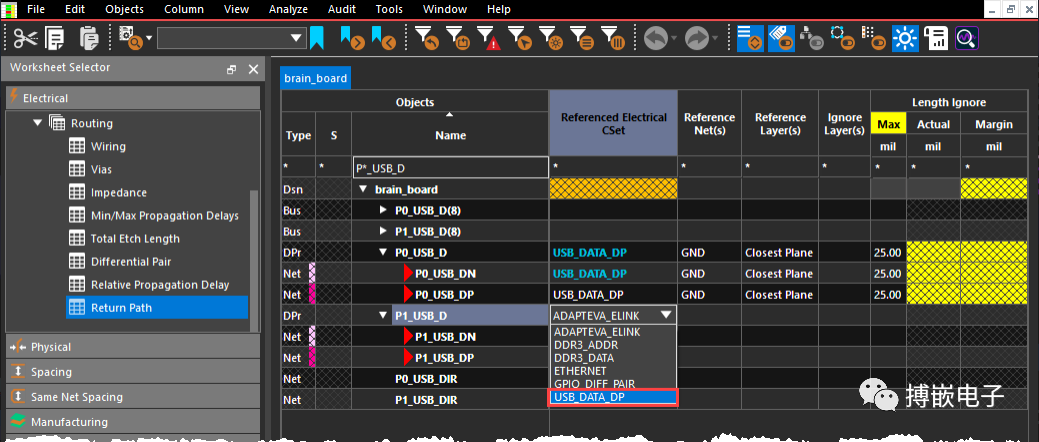

7.现在,ECset 已创建并准备好应用于设计。移动到 Net 部分并选择 Return Path 工作表。

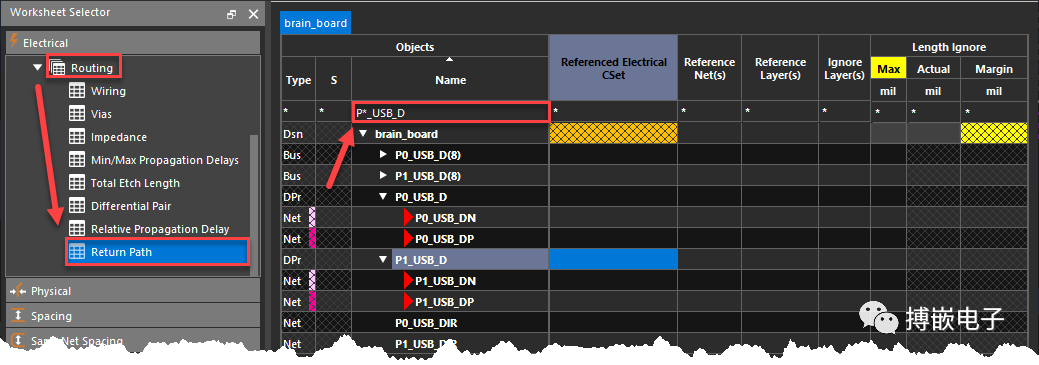

8.在对象名称过滤器中,字段类型 P*USB_D 以轻松定位 P0_USB_D 和 P1_USB_D 差异对。

9.将 USB_DATA_DP ECset 应用到 P0_USB_D 和 P1_USB_D差分对列标题中的黄色表示当前禁用了约束检查。

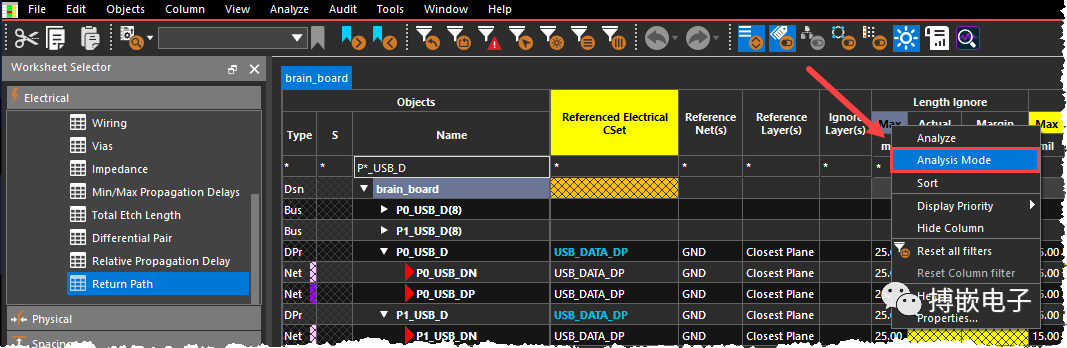

10.要启用 DRC 模式,请在 Length Ignore/Max 列上的右击 Analysis Mode。这将在它前面添加一个复选标记。

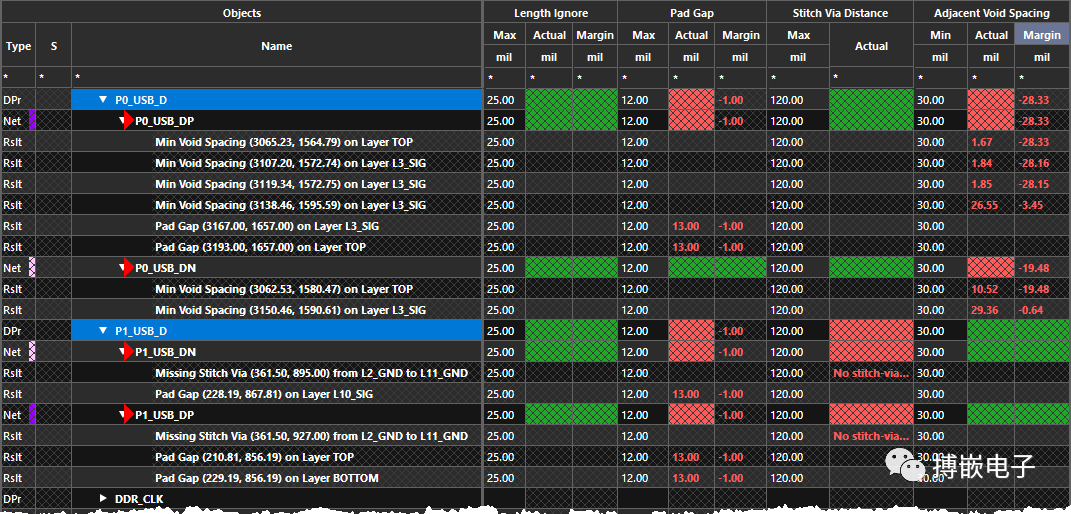

11.返回约束管理器,在 P0_USB_D 和 P1_USB_D 差分对上的 右击并选择分析。此命令将触发 CM 使用 GND 作为参考对 2 个 USB 差异对进行分析。在理想情况下,*_DP 网络的返回路径将是 *_DN 网络,反之亦然,导致通过 GND 的返回电流为零。这可能会导致 PCB 设计人员忽略最近的 GND 平面中的返回路径,但事实是不存在这样理想的差分对。不匹配的阻抗和长度,除了其他共模问题外,还会导致电流流过 GND,这意味着有必要验证这个网络的阻抗并确保它尽可能小。

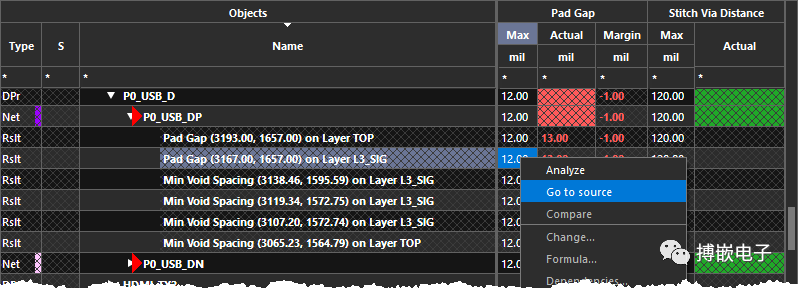

一段时间后,结果将可用。如果没有创建 DRC,则每个约束的 Actual 和 Margin 单元格将为绿色。否则,Actual 单元格将显示为红色,Margin 将显示远离所需值的值。请注意,在 13 mil 范围内的 Pad Gap 下有很多违规行为。

注意:要可视化 CM 中显示的结果 DRC 和实际值,需要将对象名称过滤器设置为 * 并手动搜索差异对。可能需要重新打开约束管理器。

使用焊盘间隙约束

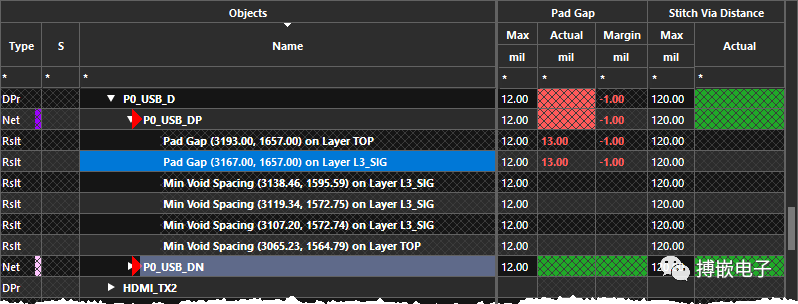

12.L3_Sig 层上的双焊盘间隙结果并单击选择。这将放大电路板上创建的 DRC。

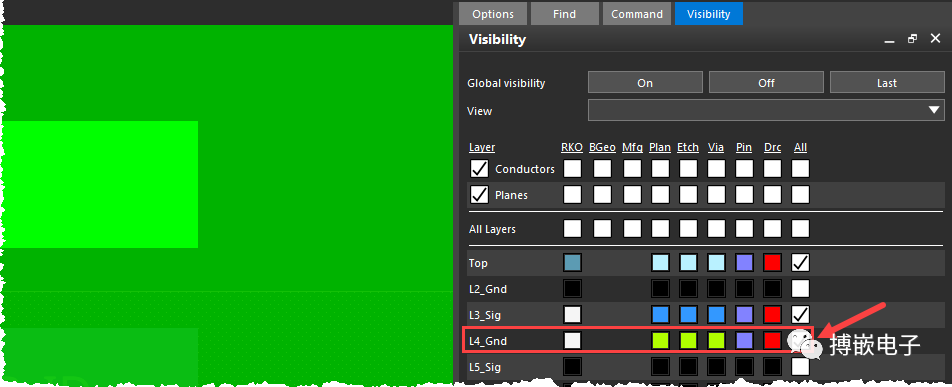

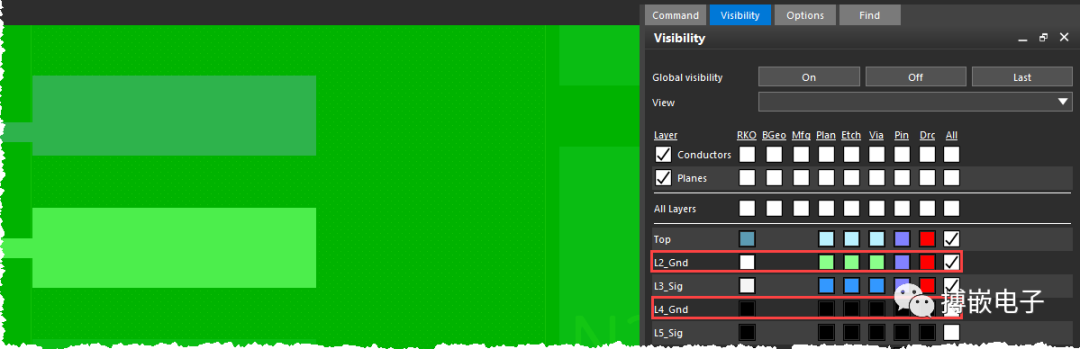

13.通过选中右侧 Visibility 选项卡中的相应 All 列来启用 L4_GND 层的可见性。

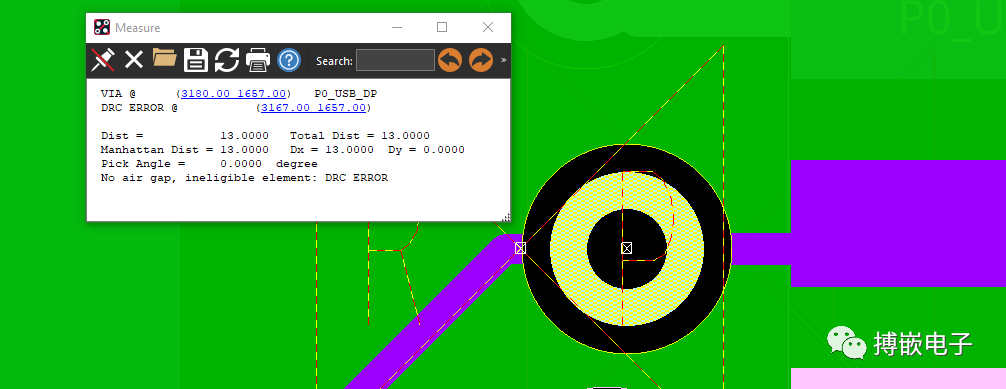

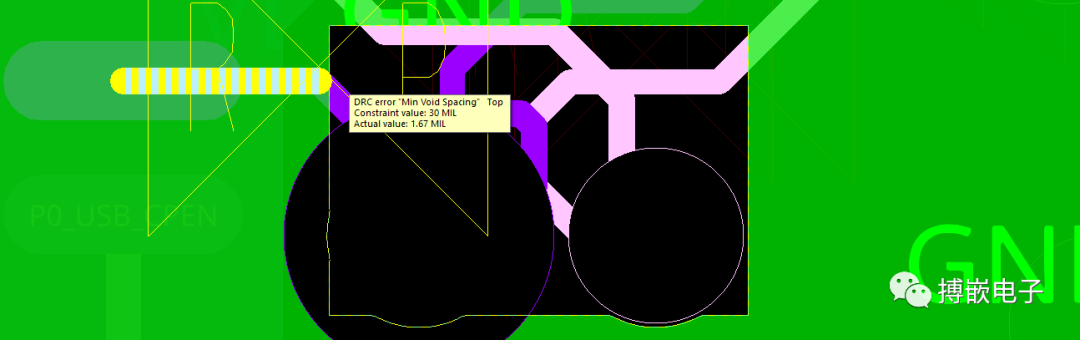

请注意,DRC 从通孔周围创建的空隙开始。使用 Display > Measure 中的测量选项显示空隙的半径为 13.0mils,这与 Pad Gap/Actual 列中显示的值相同。

14.在 Constraint manager 中,右击Pad Gap 下的任何 12.00 mil约束值,然后选择 Go to source。这将带您到设置该约束的位置,即返回 ECSet。

15.将 Pad Gap 的值从 12.0mil 更改为 13.0mil。

16.返回到 Net/Routing/Return Path 工作表,注意所有的 Pad Gap 违规都已清除。

使用相邻空隙间距约束

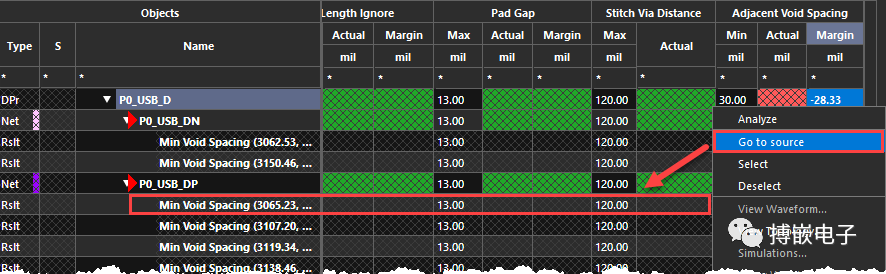

17.返回到 Adjacent Void Spacing 列,对 P0_USB_D 行的 Margin 子列上的值进行 右击并选择 Go to Source。这将选择边距较差的行,这与所选单元格中显示的数字相同。

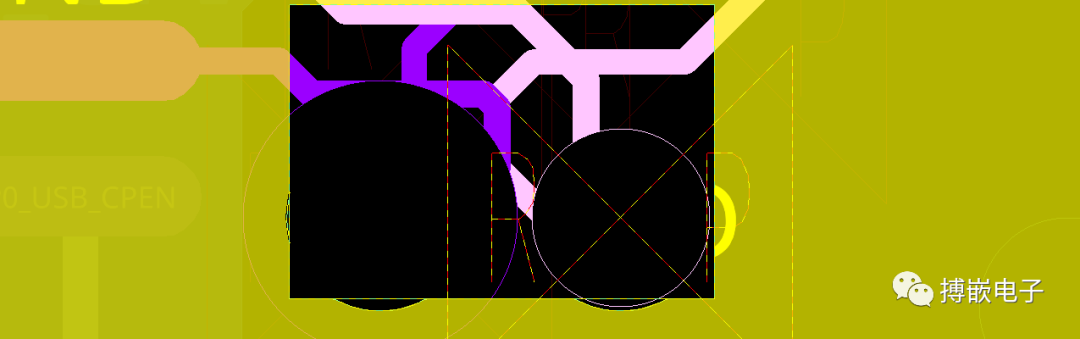

18.双击 Layer TOP 上的“Min Void Spacing (3065.23, 1564.79)”行。这将聚焦并缩放到 PCB 编辑器中的网络。

19.在 Visibility 面板中,取消选中 L4_Gnd 层的 All 列,并选中 L2_Gnd 层的 All 列。

为此结果创建的 DRC 以及与相邻空隙间距相关的其他 DRC 都位于接地层中的空隙附近。另外,请注意,尽管有一些网段通过空隙(例如丢失参考),但没有为 Length Ignore 约束创建 DRC。

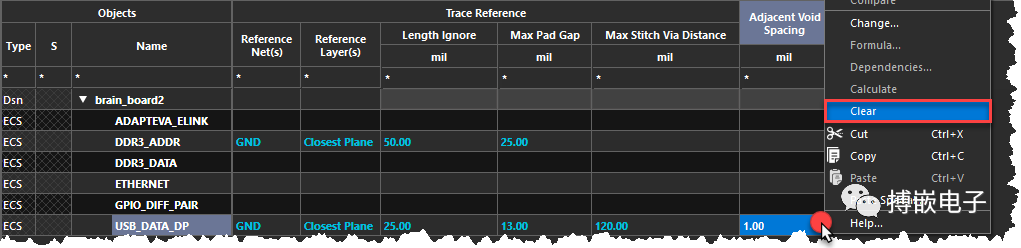

发生这种情况是因为当斜线的中心线与空隙相交并且交点大于约束时,将触发空隙返回路径的忽略长度版本。当 cline 比指定约束更接近 void 时,将触发返回路径的 void 间距版本。由于空隙间距约束必须是非负的,所以只要斜线与空隙相交,就会产生空隙间距违规。因此,空隙间距违规将涵盖空隙的所有忽略长度违规,甚至更多。为避免报告同一场景的多个违规,仅报告空间距违规。20.在约束管理器中,转到the Electrical Constraint Set > Routing > Return Path并将相邻空隙间距的值更改为 1。

21.转到Net > Routing > Return Path。请注意,没有更多的违规行为被报告。在 PCB Editor 中,也没有更多与 Adjacent Void Spacing 相关的 DRC。长度忽略也没有违规。

22.返回到 Return Path ECSet 并通过 右击在单元格上清除 Adjacent Void Spacing 约束的值并选择 Clear。这将清除约束的值。

请注意,为长度忽略创建了新的违规行为,并且针对这些违规行为向项目添加了新的 DRC。要仅获得忽略长度违规,必须通过从 CM 中的空隙间距中删除约束来禁用空隙间距。

返回路径 DRC Vision

23.从 Allegro 菜单中选择 View > Vision Manager,然后在 Visions 窗格的下拉菜单中选择 Return Path DRC Vision。

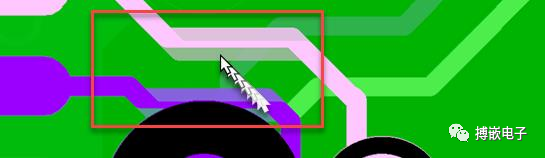

24.单击Modify Selection 并围绕 P0_USB_DN 和 P0_USB_DP 绘制一个矩形,它们是 USB 数据差异对中的网络。

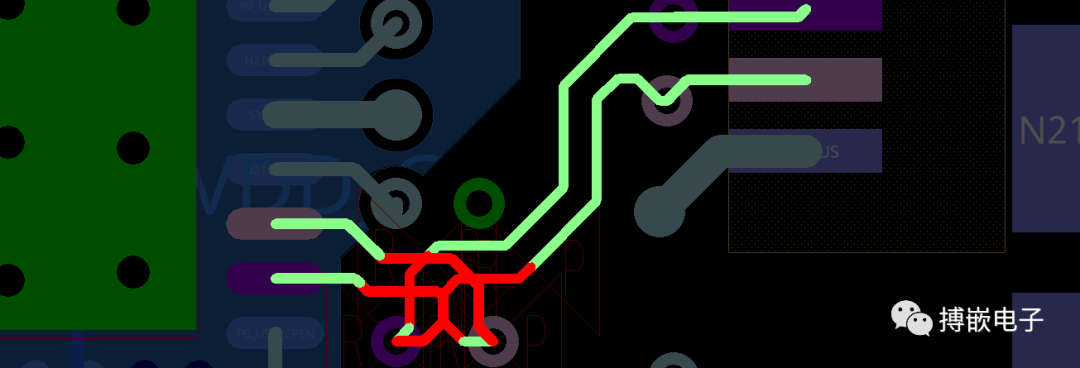

根据通过或失败,斜线或斜线段是彩色的。大多数 cline 或 cline 段是绿色的,这意味着它们满足返回路径约束。该愿景显示了违反为 Length Ignore 和 Max Pad Gap 设置的约束的段。换句话说,它不会显示 Max Stich Via Distance 和 Adjacent Void Spacing 的违规行为。

25.在下拉菜单中将视野改回No Vision,然后单击右上角的 X 关闭视野面板。

使用长度忽略约束

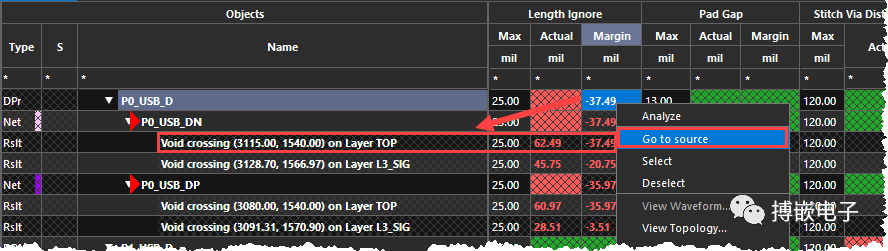

26.返回到 Length Ignore 列,右击P0_USB_D 行的 Margin 子列上的值,然后选择 Go to source。这将选择边距较差的行。

27.双击“层 TOP 上的 Voidcrossing (3115.00, 1540,00)”行以交叉探测 Allegro 画布。该错误表明它是针对 TOP 上的跟踪。这将突出显示画布上的片段和 DRC。

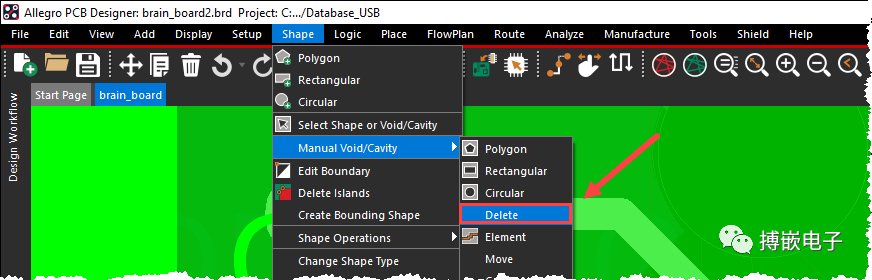

违规再次与参考平面中的空隙有关。这是一个关于忽略长度约束如何帮助设计人员识别参考平面中的问题的示例。在这种情况下,空隙没有任何实际用途,可以被移除而不是被解决。28.在 PCB Editor 中,进入 Shape 菜单并选择 Manual Void/Cavity > Delete。

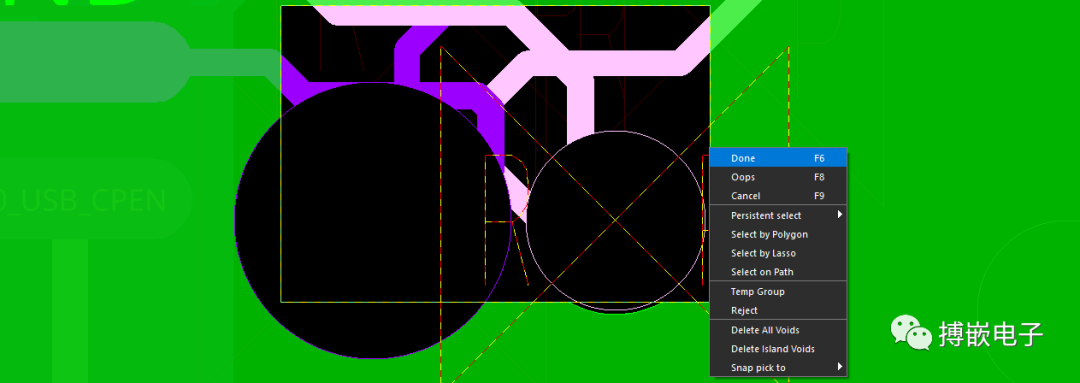

29.在画布中,第一次在地平面中单击以选择空隙所在的层。这会将飞机的颜色更改为浅黄色。

30.在空白轮廓中再次单击以选择要删除的空白,在画布上人民币并单击完成。这将删除 void 并结束命令。

请注意,所有与忽略长度约束相关的违规现在都已删除。

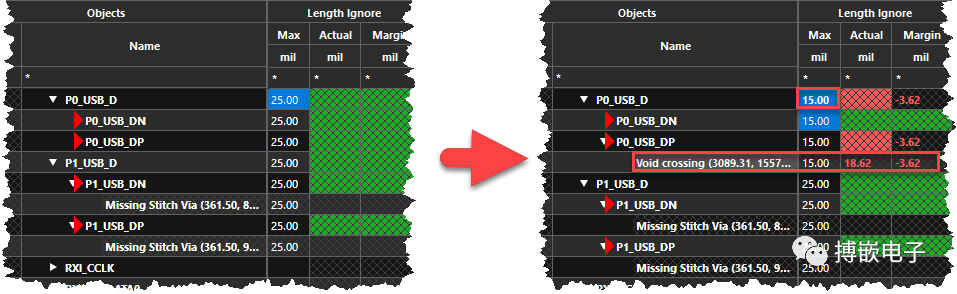

31.在约束管理器中,通过将值从 25mil 更改为 15mil,手动覆盖 P0_USB_D 差异对的忽略长度的 ECSet 值。

请注意,现在创建了一个新的违规。

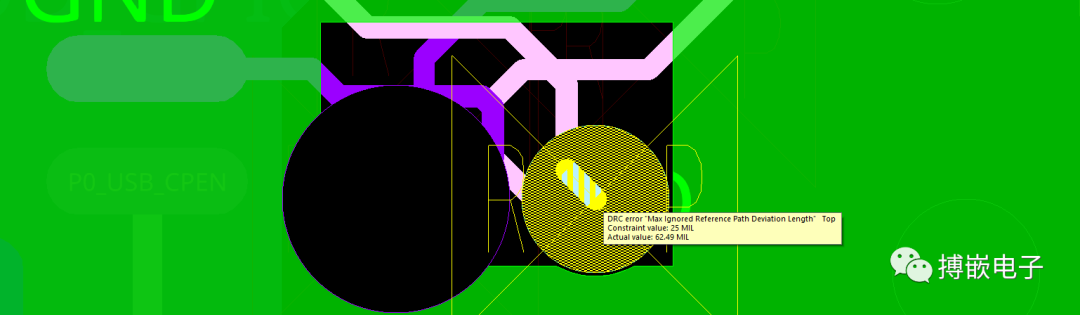

32.双击DRC。这将聚焦并缩放在板上创建的 DRC。

特定焊盘堆栈中的大反焊盘或大间隙也可能通过在形状中产生大空隙而导致参考信号丢失。在这种情况下,假设如此大的反焊盘是有动机的,这意味着设计人员需要滑动网络以将其移回参考平面上方。

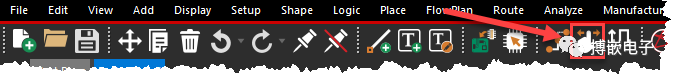

33.在PCB Editor工具栏中,选择slide命令。

34.单击穿过空隙的 P0_USB_DP 段,将其滑动一点,使该段的中心线不再与空隙相交。

请注意,DRC 在滑动段后立即被删除。

使用 Stitching Via 约束

35.在约束管理器中,双击仍然存在的每个违规。

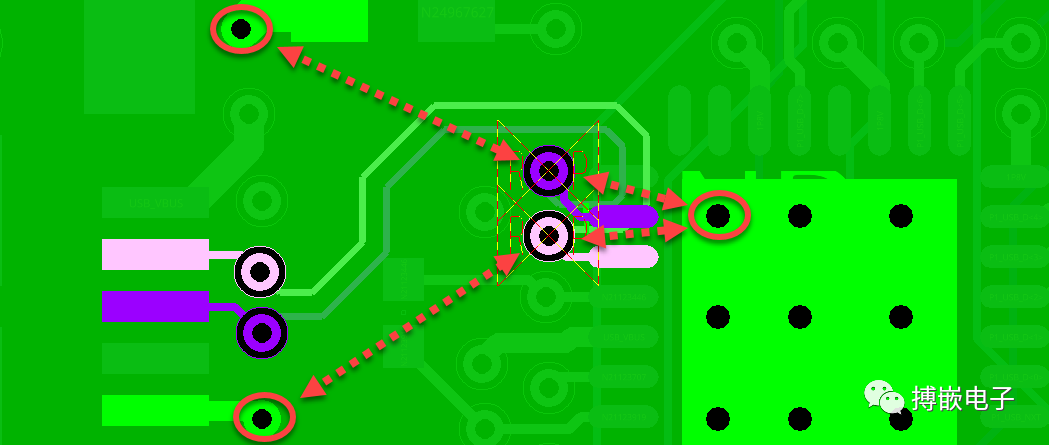

请注意,两者都位于电路板的同一区域。发生这种情况是因为,对于两个信号过孔,它们附近没有距离小于 120 mils的参考过孔。

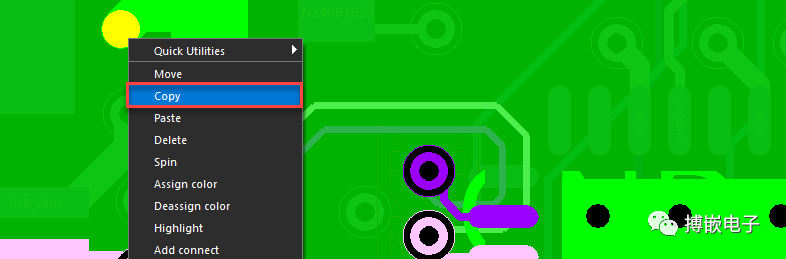

36.右击在其中一个过孔上并选择复制。确保在 Find 面板中启用了 Vias 选项以启用选择过孔。

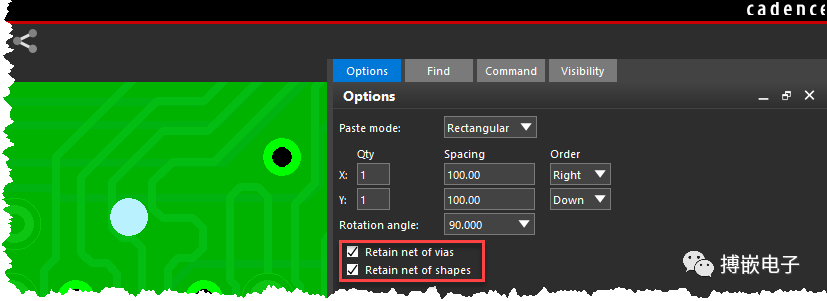

37.验证是否在选项面板中启用了 Retain net of vias 和 Retain net of shapes 。

38.在命令面板内的命令字段中键入“x 330 930”,然后按 Enter。这会将过孔放置在给定的 X、Y 位置。

39.右击并选择完成以完成命令。请注意,板中的所有 DRC 和约束管理器中的违规都已删除。

参考平面选项

40.返回约束管理器,滚动回顶部并单击与设计行和参考层列对应的单元格以显示选项。

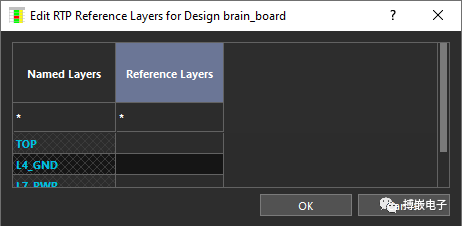

41.选择表以启动以下对话框。此选项允许通过为整个设计定义表格来设置参考层。蚀刻层与平面层之间存在 1:1 映射。

42.取消“Edit RTP Reference Layers for Design brain_board”对话框。43.将电路板另存为brain_board2.brd 并关闭PCB Editor。

建组设置

1.启动 Allegro PCB Editor 使用提供 IDA 分析工作流程并加载 Brain_board.brd 设计的许可证之一。

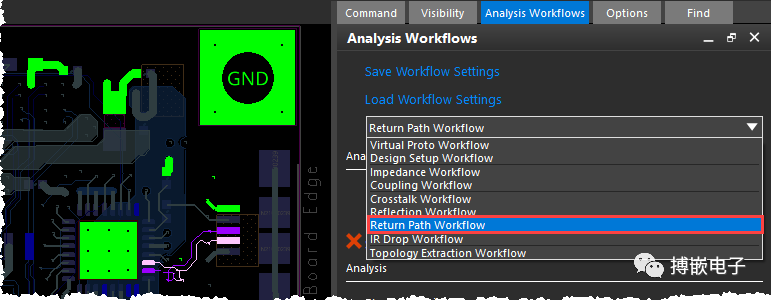

2.在顶部菜单中,选择Analyze > Workflow Manager。

3.在下拉菜单中选择Return Path Workflow工作流。

4.在参考网络下,选择 GND 网络。

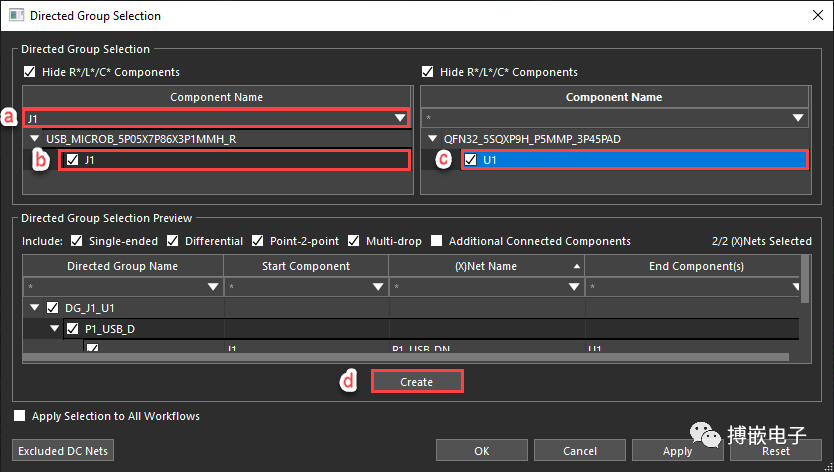

5.左击工作流中的“Select Directed Groups”链接,位于“参考网络”下拉列表的正下方。6.要创建从 U2 到 J1 的单个Directed Group,请执行以下操作:

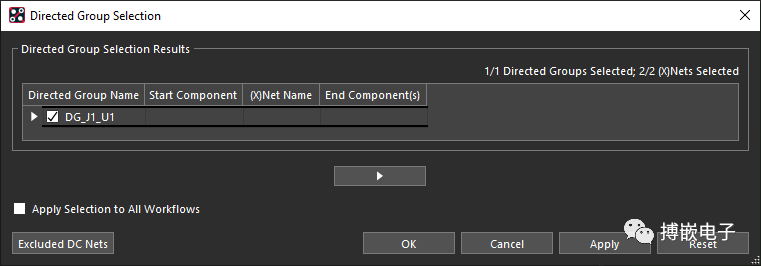

现在,对话框顶部应该有一个定向组(显示为折叠状态):

也可以通过单击板上的组件并在直接组选择预览中选择/取消选择网络/Xnet 来创建定向组

7.清除先前设置的左侧组件名称搜索字段中使用的搜索字符串。这将允许用户选择浏览器上的任何组件。

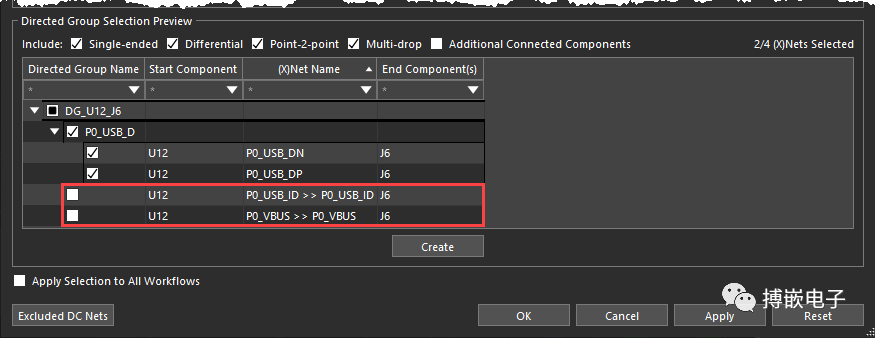

8.将右上角的 USB 电路放在板上,并使用鼠标光标左击放在 U12 和 J6 上。

9.在 Directed Group Selection 对话框中,取消选择 P0_USB_ID >> P0_USB_ID 和 P0_VBUS >> P0_VBUS (X)Net 名称。

10.选择Create按钮。这将创建第二个定向组/。11.在“Directed Group Selection”对话框中单击“OK”。

分析和结果

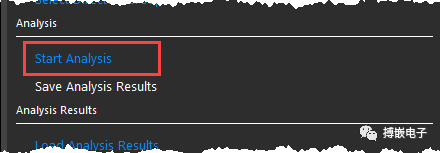

12.在工作流中选择Start Analysis链接。模拟将开始,可能需要几分钟才能完成。

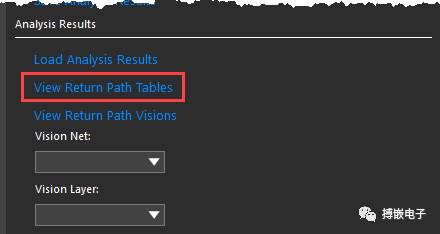

13.在工作流中选择 View Return Path Table链接。

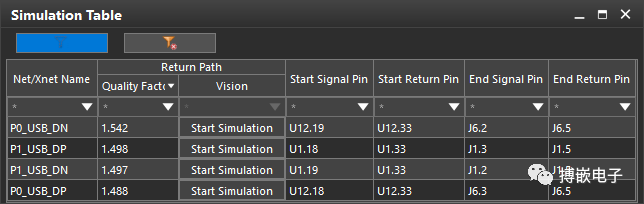

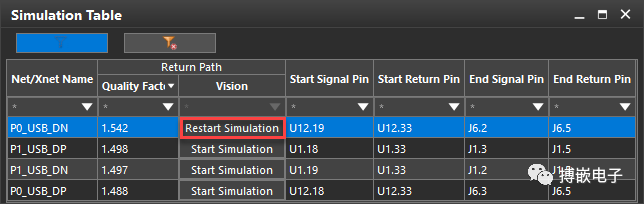

模拟将打开,向用户显示每个网络/Xnet 的质量因子,并允许模拟为每个网络生成一个视图。

这些模拟应该单独执行,使设计人员能够可视化并轻松理解导致高质量因素的原因。

14.如果未完成,请对Return Path Quality Factor返回路径质量因子 (RPQF) 列进行排序。RPQF 的范围是从 1.542 到 1.488。RPQF 没有指示问题的最佳值或阈值。值为 1 的 RPQF 代表理想情况。当 RPQF 值越趋近于 1,则表示信号布线与与回流路径是越贴近的,越高则代表回流路径越曲折绕越远的路径。

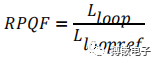

RPQF 是根据环路电感基本原理计算的。Allegro Sigrity SI 基础利用 Sigrity 混合求解器计算环路电感。RPQF 基于环路电感,定义如下:

备注:环路电感计算公式:

环路电感 = 信号路径自感 + 返回路径自感 - 信号、返回路径互感15.点击 Start Simulation 在 Simulation Table 对话框中 P0_USB_DN 网络的 Vision 列中。一段时间后,模拟将完成,文本将变为 Restart Simulation。

请注意,P1_USB_DN 和 P1_USB_DP 具有相似的品质因数值,这表明网络耦合良好,因为可能的解释是它们具有相似的环路。这个假设不能外推到任何网络,因为具有完全不同返回路径的网络可以具有相似的品质因数值。

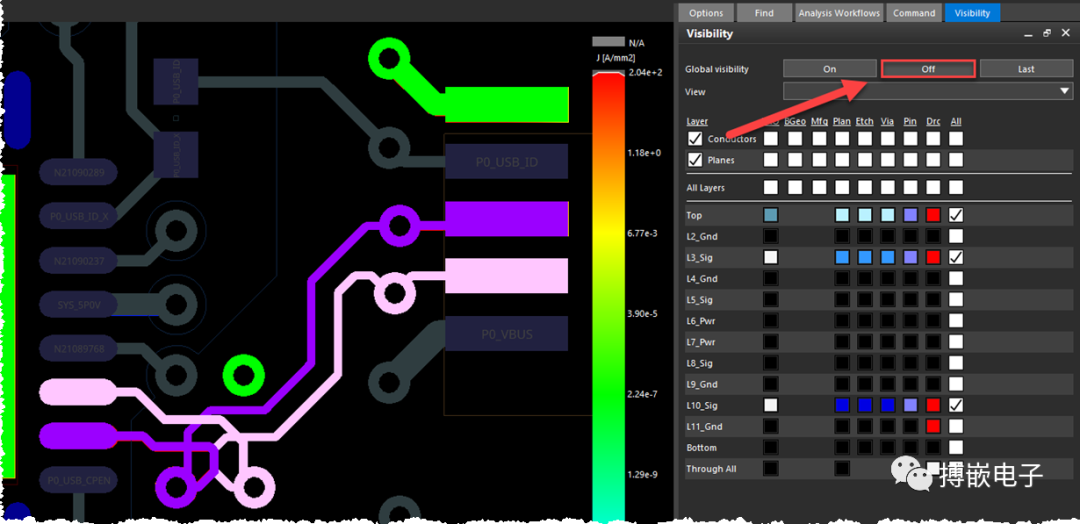

16.在 Vision Layer 下拉列表中选择 L2_GND。这是 P0_USB_DP 网络的大部分路由所在的层。该网络是右上角 USB 电路的一部分。17.在右上角的可见性面板中,通过单击关闭按钮将全局可见性设置为关闭。这将使模拟结果的可视化变得更简单。

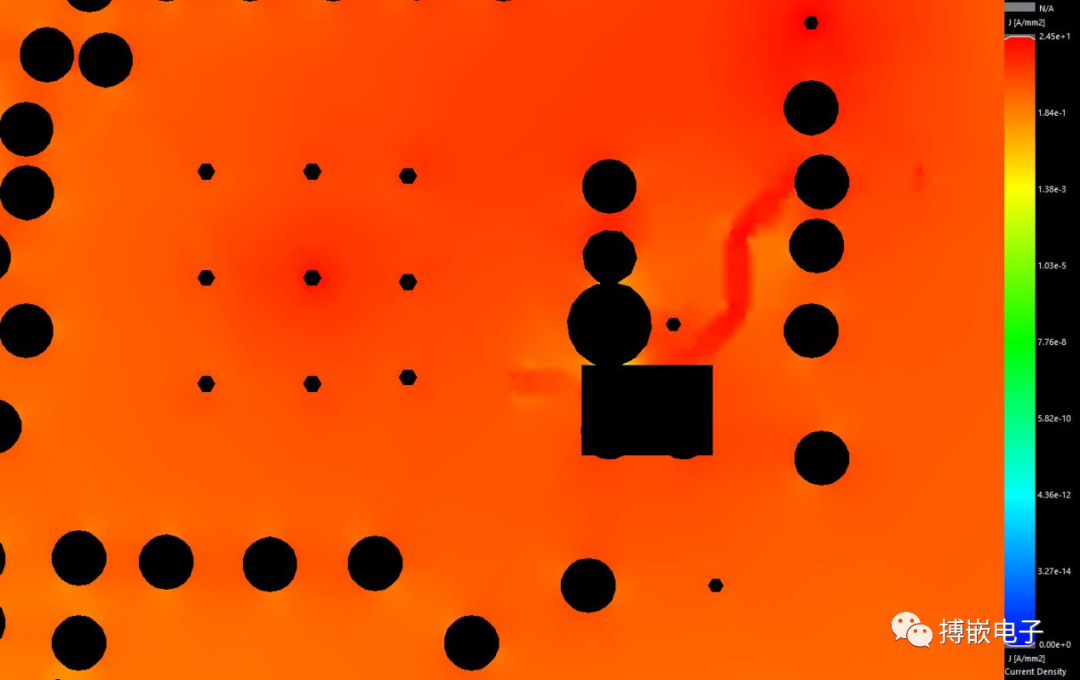

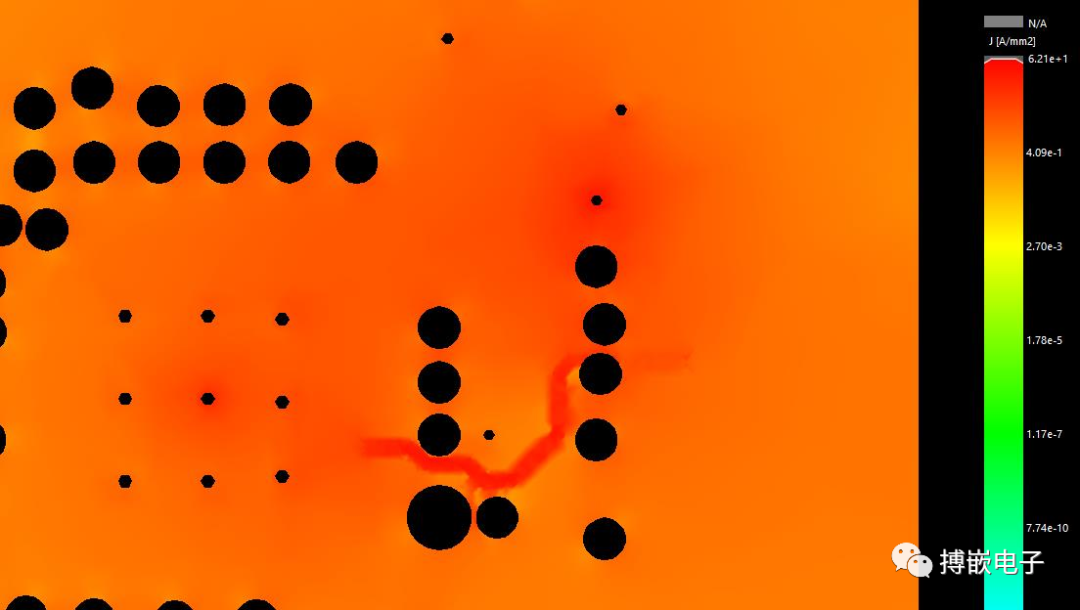

18.在 Vision Layer 下拉列表中选择 L2_GND 层。可以将电流的返回路径可视化为参考平面。

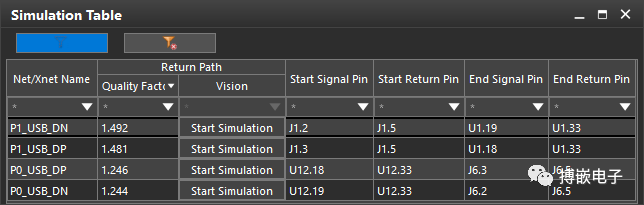

19.在新的 PCB Editor 实例中打开 Brain_board2.brd(在模块 1 中创建的电路板)并重复从 2 到 12 的步骤。20.在工作流程中选择View Return Path Table链接。

请注意,所有 RPQF 值都变小了。还可以看到 P0_USB_DP 和 P0_USB_DN 的值变得更加相似,尽管 P1_USB_DP 和 P1_USB_DN 稍微增加了差异。

21.重复从 15 到 18 的步骤,将 L2_GND 层可视化为P0_USB_DN 网络。请注意,电流密度的最大值更大,并且集中在信号网络的上方/下方。

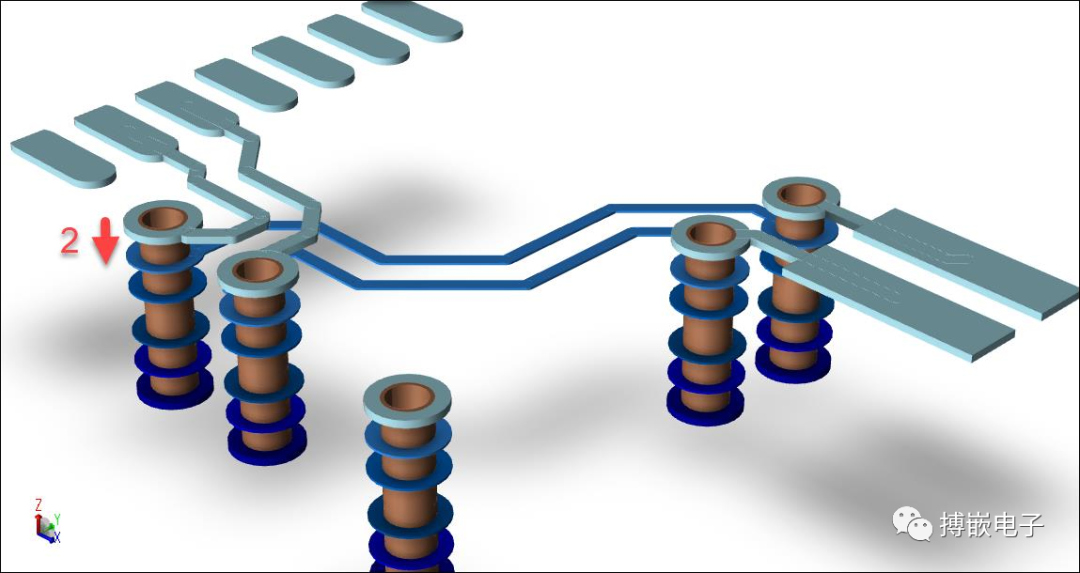

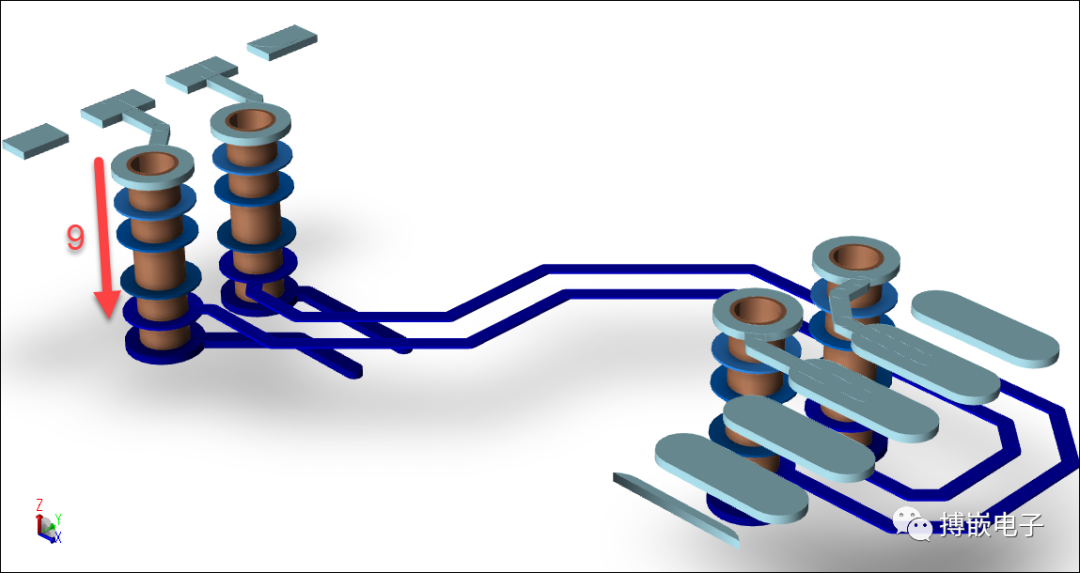

请注意,即使在 Brain_board2.brd 中解决了所有 DRC,P0_USB 和 P1_USB 差分对的品质因数之间仍然存在相当大的差异。之所以会出现这种差异,是因为每个电路都使用了过孔。在右上角的 USB 电路中,差分信号改变了 2 层。

另一方面,左下方的 USB 电路的 diffpairs 改变了 9 层,对应于 4 个参考平面,然后返回到 TOP。这表明路由可以改善网络的返回路径,并且返回路径工作流程可用于查找仅使用可用 DRC 无法检测到的问题。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...