由于在自动驾驶领域需要对传感器的数据作大量的基于深度内神经网络的复杂运算,GPU和FPGA被不约而同地用来作为对CPU的一种加速器被使用。这样做不仅可以提高计算性能,并且可以大幅度地降低能耗。FPGA+CPU架构的自动驾驶平台凭借其灵活性,高效率,低能耗等特点,正越来越多地被一大批拥有技术实力的公司使用,比如Waymo,百度,福特,通用等。在这里本文试图探讨如何对FPGA+CPU自动驾驶平台的性能进行估计,目的是希望帮助开发者在选择FPGA+CPU自动驾驶系统平台时初步掌握一种对系统性能的评估方法。本文将以Xilinx 推出的Zynq UltraScale+ MPSoC ( Part#=ZU19EG )为例,来阐述其方法。

由于作者知识水平和写作方法的局限,如读者能指出错误纰漏之处,将万分感谢。

图一 是比较典型的基于FPGA+CPU的自动驾驶系统原理图。一般来说配置一个多核的应用处理器单元-Application Processor Unit(简称AP)用来跑一个或者多个操作系统,主要用来任务调度,管理等工作,而大数据的处理:比如图像的特征值提取,目标类别识别,多目标跟踪,运动预测等复杂运算多放在FPGA 的可编程逻辑模组Programmable Logic(简称PL)来处理。衡量自动驾驶平台的性能,关键点在几方面:1、系统对大数据的处理能力,在这里就是要了解FPGA的PL模组的运算能力。2、复杂多任务的处理能力,即应用处理器CPU的运算能力。3、高速海量数据的传递,即传感器的数据接收,以及PL和AP之间的数据通讯能力。

由于篇幅原因,本文将只对第1点进行详细叙述,而第2,3点只做简单叙述。

图一:基于FPGA+CPU的自动驾驶平台原理图

在介绍如何计算FPGA的性能之前,我们来了解一下目前主流的FPGA的硬件。以Xilinx的Zynq UltraScale+ MPSoC为例,其PL包含可编程资源 Logic blocks, RAM, DSP slices等。而要得到最终的FPGA 性能值,由于以下几点原因而变得困难。

目前通常使用的方法是参考系统的每秒浮点运算操作(floating-point operations per second ),简称FLOPS。因为浮点运算用到的所有的高阶函数,比如除法,平方,三角函数等,都能归结为加法,乘法运算,且常用的傅里叶变换,矩阵操作也都可以用加法器(adder)和乘法器(multipliers)的组合来实现,所以FLOPS和加法器/乘法器的数量在衡量其运算性能上是直接关联的。

为了计算FPGA的最大运算能力,我们可以通过利用单精度(Single-Precision)数据加法器数量的方法来求出一个系统的FLOPS。较乘法器而言,加法器利用到的系统资源少,求出的系统FLOPS的值就会接近最大值。

假设所有的运算都是并行的,那么可以得到下面的FLOPS计算公式:FPGA PL FLOPS = ( Clock1 x LC based Adder#) + ( Clock2 x DSP48 based Adder#)根据以上公式,下面我们以Xilinx的Zynq UltraScale+ MPSoC的ZU19EG为例,来求其FLOPS。

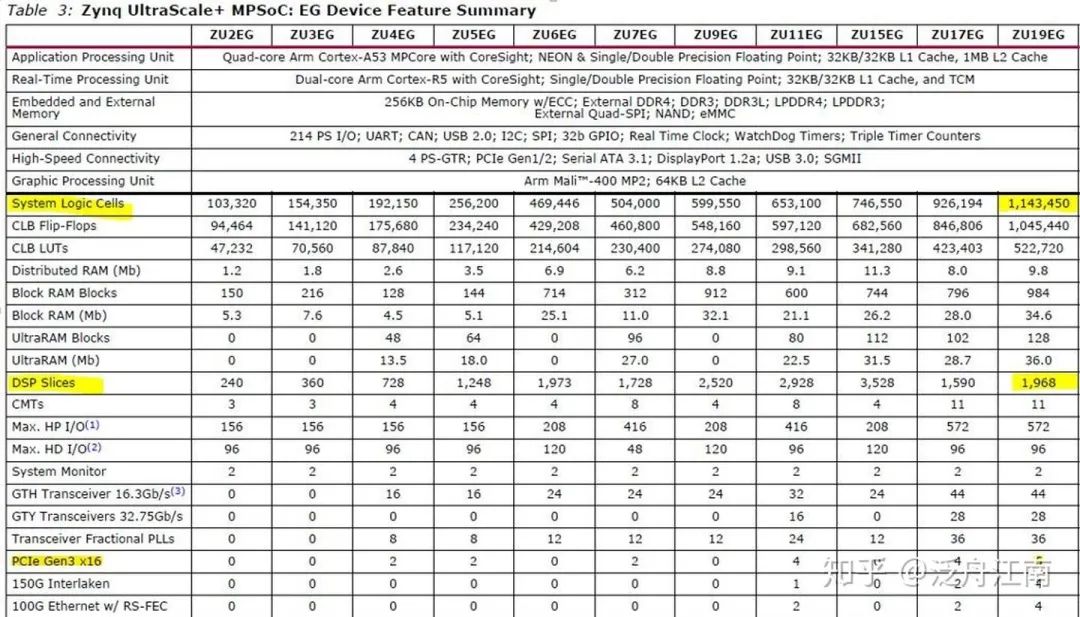

由图二,Zynq UltraScale+ (Part=ZU19EG) 拥有的资源列表,我们可以看到它有1,143,450个Logic cell, 1,968个DSP slices。

图二:Xilinx Zynq UltraScale+资源列表

图二:Xilinx Zynq UltraScale+资源列表

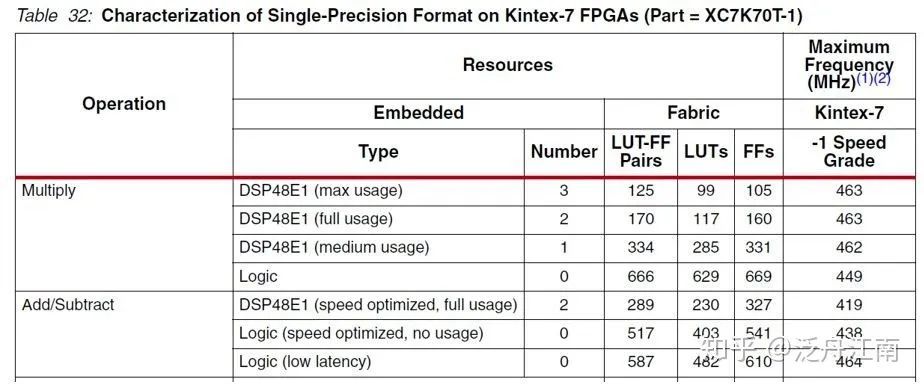

IP Core的实现方式由算法供应商决定,在这里仅以Xilinx提供的基于Kintex-7上的加法器IP Core用到的资源作为参考,误差应该在可接受范围。如图三,可以得知:

图三 支持单精度的FPGA特征由于实现相关的I/O设备,必须占用掉一定数量的Logic Cell,这里我们假设用掉14000个Logic Cell. 也即:Logic Cell 剩下总数 = 1143450 - 14000 = 1129450由于要计算出最大值,我们需要假设尽可能多的使用所有资源,这样可以得出:

我们可以得知:

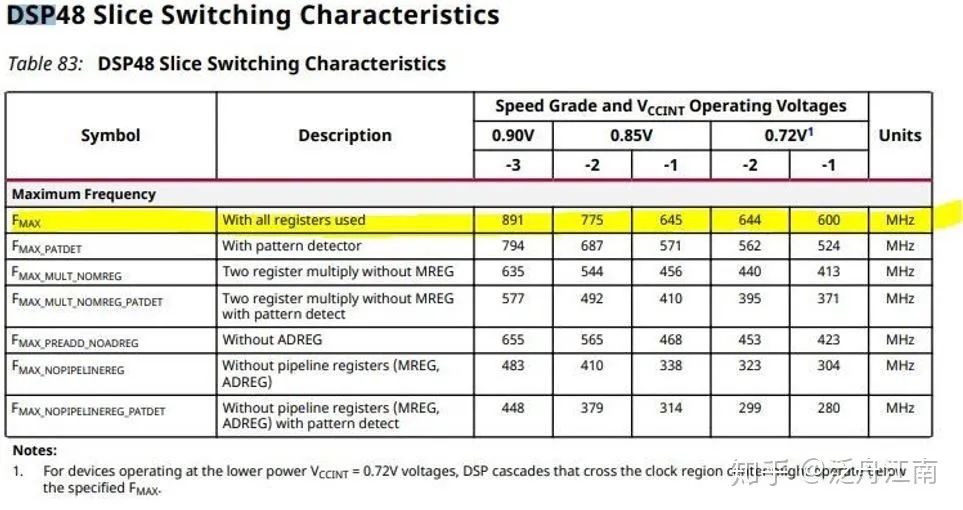

图四 DSP slice 频率参数特征

图四 DSP slice 频率参数特征

图五 Global 时钟参数特征根据不同的温度条件,Fmax的值需要相应调整。比如:

为了计算最大运算能力,我们采用在0-100度的条件下的clock值,也就是891MHz。

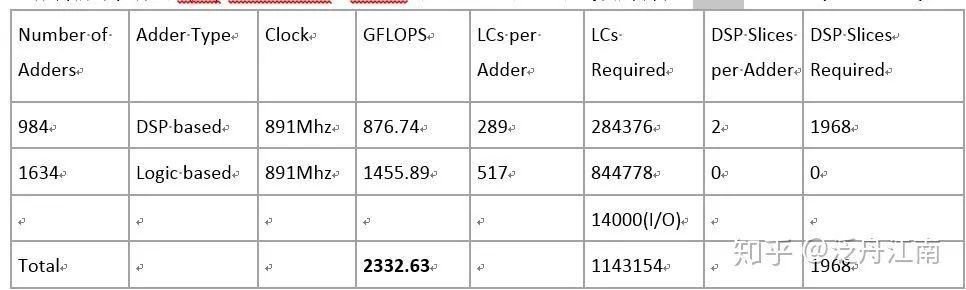

图六 各个模组算力一览这样我们可以得出Zynq UltraScale+ MPSoC的ZU19EG的PL的运算能力为:2332 GFLPOS (~2 TFLOPS)总结: ~2T FLOPS某种程度上反映了FPGA Zynq UltraScale+ ZU19EG PL的处理能力。如果针对汽车级别产品而言,-40度至100度温度的限制,整体PL的 FLOPS值应该在1 FLPOS - 1.5T FLPOS之间比较恰当。

如图七,Xilinx的MPSoc+FPGA系列产品则完全可以叫SoC了,其不仅包含多个ARM CPU内核,还有针对安全领域的R5内核,还有Mali 400这样的GPU。从下面的图,可以得知FPGA Zynq UltraScale+ ZU19EG拥有

图七 Xilinx FPGA Zynq UltraScale+ ZU19EG框图估算下来:

Note: Cortex-R5 : 1.67 / 2.02 / 2.45 DMIPS/MHzCorte-A53: 2.24 DMIPS/MHz

目前通用的认知是Level3的自动驾驶需要系统拥有~350,000DMIPS的运算能力,才可能实现比如雷达/视频的处理,主动避让,自动泊车等。以上章节所说的MPSoc+FPGA已经有足够的计算能力足以支持Level3左右的自动驾驶在一般场景下的运用。

然而为了支持更多的自动驾驶Level4/Level5的场景,由于FPGA的接口灵活性,很容易在和FPGA的基础上额外增加子计算模块,整个系统运算能力将突飞猛进,这样极大地方便了平衡运算力到不同的运算单元。比如:可以把激光雷达的数据处理单独放到某一个Intel Xeon 子计算模块执行,FPGA母板只需要控制逻辑,把激光雷达数据通过高速接口(PCIe或者10G以太网)传递给子计算模块让其进行大量的数据处理。

FPGA的灵活性可以让开发者拓展出越来越多的可能。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...