软件无线电的中心思想

构造一个具有开放性、标准化、模块化的通用硬件平台,将通信的各种功能通过软件来完成,并使宽带A/D和D/A转换器尽可能靠近天线,以研制出具有高度灵活性、开放性的新一代无线通信系统。由于软件无线电可以通过增加软件模块来增加新的功能,而且硬件也可以随着器件的发展而不断地升级,所以这一概念一经提出就受到了广泛的关注。

系统结构设计

目前受器件的限制,软件无线电一般都采用中频采样的结构,这样做既兼顾了软件无线电的思想,又能在目前的器件水平下搭建实际可应用的系统。本文的软件无线电平台也采用了这一结构。随着无线通信系统的发展都在朝着高速率、可移动性方向发展,因此本平台的设计也必然要适应宽带无线通信系统的要求。

平台结构

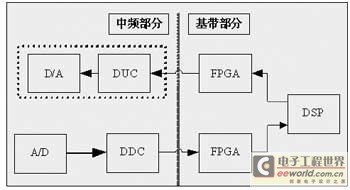

平台主要针对系统物理层中的中频和基带处理单元而设计。系统的结构如图1所示。平台由一个DSP(TMS320C6414T)、两片FPGA(Cyclone EP1C6Q240C8)、上变频芯片DUC(AD9857)、下变频芯片DDC(HSP50214B)等构成。

图1 平台结构图

根据信号处理模块和各芯片数据处理的特点,我们将各通信模块分配到不同的器件中来完成。DSP的主频很高,而且内部资源丰富,支持高级语言的编程,适合于串行的算法,用来完成协议和基带处理;

FPGA配置灵活多变,虽然主频不太高,但是鉴于其并行处理能力突出,用于完成时钟分配、芯片设置、接口转换等;AD9857和HSP50214B是用于上下变频的ASIC,集成程度高,参数设置灵活,可以满足多模式的数字上下变频,数据速率变换和滤波。下面简要介绍一下平台上器件的性能。

器件介绍

DSP

平台选用的DSP芯片是TI公司的TMS320C6416T芯片。该处理器属于32位定点处理器,主频1GHz,内部集成丰富的外设和接口。在指令结构上,扩展了寻址指令、位域指令、打包解包、控制转移等指令,增强了芯片的处理能力。在计算2048点的复数FFT运算时,可以在大约26 000个时钟周期内完成。

6416T主要包含的模块有:1)两个通用寄存器组,64个32位通用寄存器;2)8个功能单元,6个ALU(32/40b),两个乘法器(16×16);3)一共8.256Mb的两级缓存内部存储;此外,还有图1中没有列出的Viterbi编解码协处理器(VCP)和Turbo码编解码协处理器(TCP)。VCP支持500路7.95Kb/s AMR,TCP可以处理6路2Mb/s 3GPP。

接口方面包括:

1)多通道EDMA控制器;

2)多通道缓冲串口(MCBSP);

3)高性能外部存储器接口(EMIF);

4)可访问DSP的整个存储空间的主机口(HPI);

这里不在一一列举。

上变频芯片AD9857

AD9857是一款高性能的数字上变频器,***时钟为200MHz,根据外时钟的范围,可以选择0~80MHz的任意中频输出;芯片还具有两级内插功能,可以实现4倍固定内插和2~64倍可选内插倍数,便于多数据速率变换;14b的DAC。

A/D变换器AD9051

ADC选用ADI公司的AD9051,***采样速率达到60MSPS,10b输出,对于中心频率较低的中频信号可以进行直接采样,中频值较高的则运用带通采样方式。

下变频芯片HSP50214B

HSP50214B是专用数字下变频芯片中综合性能***的,除数字下变频外还具有***255阶可编程FIR滤波器,0~96dB动态范围的 AGC自动增益控制,数据速率变换包括4~32倍CIC抽取和5级HB抽取,以及FIR1-16倍抽取,坐标转换,鉴频等功能,而且具有四种输出形式,接口灵活。

FPGA

由于平台上的中频处理由ASIC完成,所以FPGA选用了CycloneⅡ EP1C6Q240C8,这是一款低端的FPGA芯片,逻辑单元只有6000门,主要用来完成时钟分配,接口转换,ASIC控制字配置,以及作为DSP的协处理器的补充。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...