1.关于等长

第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。

不知道从什么时候起,绕等长成了一种时尚,也成了 PCB设计工程师心中挥不去的痛。需要等长设计的总线越来越多,等长的规则越来越严格。5mil已经不能满足大家的目标了,精益求精的工程师们开始挑战1mil,0.5mil……还听过100%等长,没有误差的要求。

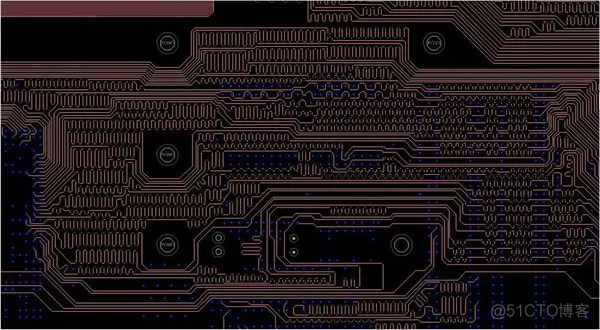

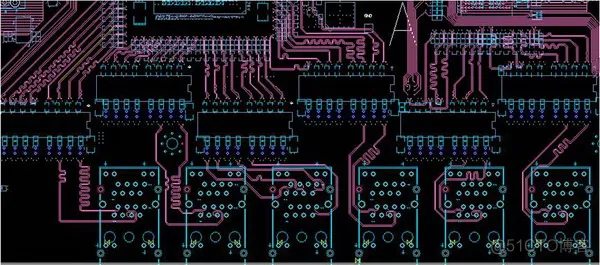

为什么我们这么喜欢等长?打开PCB设计文件,如果没有看到精心设计的等长线,大家心中第一反应应该是鄙视,居然连等长都没做。也有过在赛格买主板或者显卡的经验,拿起板子先看看电容的设计,然后再看看绕线,如果没有绕线或者绕线设计不美观,直接就Pass换另一个牌子。或许在我们的心中,等长做的好,是优秀PCB设计的一个体现。

做过一个非正规的统计(不过一博每年上万款PCB设计,我们的采样基本上也可以算做大数据了),稍微复杂一点的高速板子,绕等长要占据总设计时间的20%~30%。如果等长规则更严格,或者流程控制不好,做了等长之后再反复修改,这个时间还会更多。

2.那些年,我们一起绕过的等长

培训的时候,我们经常会玩一个游戏,游戏的名字叫做:那些年,我们一起绕过的等长……

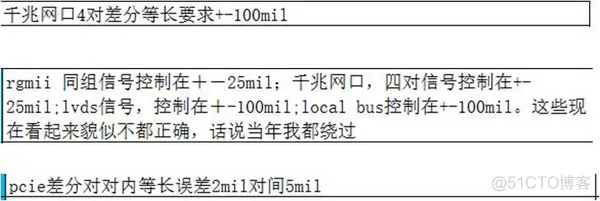

说到等长要求,先说说什么是“裕量”哈。“裕量”是设计时保留的安全间距,百度百科的解释更简单:多出来一部分,就称之为裕量。到底要多多少,什么才是安全,那就见仁见智了。每个人的安全感不同,对“裕量”的定义就不一样。但是在 时序设计的时候,有一个现象比较普遍,那就是裕量层层放大,比如产品经理可能要求等长范围是±100mil,项目经理可能就会更严格到±50mil,然后到具体的实施工程师,可能就变成±5mil了。碰到一些“安全感”不足的工程师,那就恨不得是完全等长,没有偏差。

所以,后面的讨论里面,我们不会太多纠结在等长到底是10mil还是±5mil,我们集中精力来看看哪些等长是没有必要的,哪些等长反而破坏了系统的时序设计要求。

1、关于等长与等时

绕线系列的第一篇文章发完之后,就开始准备美国研讨会,然后就是长达一个月的出差。终于有时间继续这个话题了,先来看看之前大家的回复,我隐去了回复者的名字,只保留了答案:

游戏开始,大家直接回复“高速先生”,列举下自己做过的,或者认可的等长设计要求,之前的部分答复如下:

…… ……

之前也提过,现在流行重要的事情说三遍:

1、 等长从来都不是目的,系统要求的是等时……

2、 除了差分对内的等时是为了相位之外,绝大多数的等时都是为了时序!

3、 为了 时序而绕线,就一定要搞通时序关系,看懂时序图

每次看到时序图的时候,都会眼前一黑有没有?

时序是大家非常头痛,也觉得非常复杂的话题,所以高速先生小陈在之前的时序话题中试图用两对恋人的恋爱关系来解释时序问题,绕口令式的比喻不知道有多少人真正看懂了?给我的感觉是80、90后们好像很快领悟了小陈的意思,而70后们普遍表示更晕了有没有。

想把时序问题简单讲清楚,是一个巨大的挑战,高速先生的精神就是迎难而上,前仆后继。我的目标是不给大家看复杂的时序图,也不引用什么比喻联想,让大家简单理解时序。

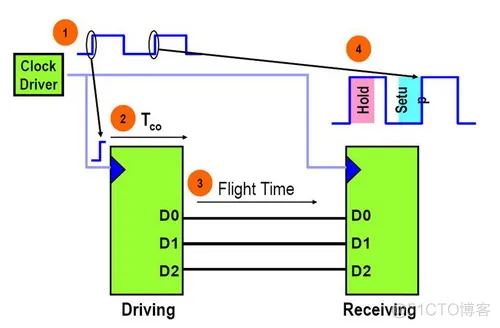

共同时钟总线的时序特点是,时钟的上一个边沿,发送芯片打出数据,然后在下个时钟边沿,接收芯片接收数据。为了简化后面的理解,假定时钟达到驱动端和接收端的时间一致,也就是时钟线等长(这也是最常规的设计思路)。

影响时序的因素有Tco,Tskew,Tjitter,Tcrosstalk……,看起来很复杂,简单来说,只要满足两个条件,即可达成时序要求:

1、 一个时钟周期之内,数据要完成从驱动端发出,到达接收端,并有足够的建立时间

2、 第二个数据来到之前,前一个数据要有足够的保持时间

满足条件1,就要求Tclk能包容数据到达所需的是所有时间,这些时间包括了数据输出延时(Tco),数据飞行时间(Tflighttime),数据保持时间要求(Tsu),以及所有七七八八影响时序的因素(Tcrosstalk,Tjitter……),并且所有这些因素都要取最恶劣情况。

TPCB skew+Tclock skew +Tjitter +Tco data +Tflt data +Tsetup<Tcycle

满足条件2,就是下个数据最快会在最小数据输出延时(Tco min)加上最小数据飞行时间(Tflighttime min)之后达到,数据必须在下个数据达到之前有足够的保持时间。

Tco data +Tflt data +Tclock skew+Tpcb skew>Thold

真正设计的时候,我们需要从器件手册查找相应的数据来进行时序计算。从理解角度来说,却不用那么复杂。

<p style="text-align: center;>

0.3ns<Tfly time<0.7ns

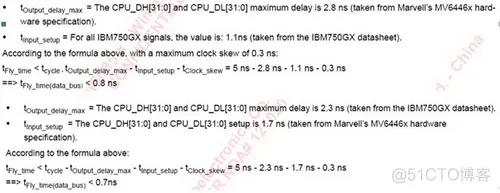

上图是一个实际案例计算后的结果,我们从中只要看懂两个事情:

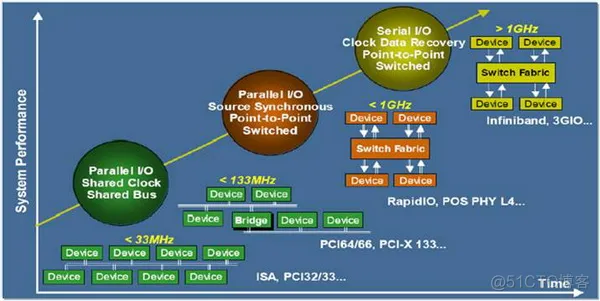

一、共同时钟总线时序关系随着TClk的减小,难度急剧加大。33M、66M的共同时钟总线,适度关注拓扑结构和端接来保证信号质量就够了,不需要任何绕线。100M以上的共同时钟总线时序开始变得紧张,133M以上的系统,建议一定要做时序分析,否则风险很大。

二、共同时钟总线时序是对总长的要求,不是等长,借用Cadence Allegro的规则管理器来解释,共同时钟总线最合适的电子规则是Total Etch Length,而不是我们常用的各种Propagation Delay。

注:100M或者133M以上的时候,由于时序非常紧张,有可能通过控制外部时钟Skew(布线或者调整寄存器)的方式来调节时序,这时对以上不等式两边进行调整的过程中会涉及到总长的差异问题。但是也还是用Total Etch Length的规则来约束设计,而不是Propagation Delay

讲了这么多,大家继续晕菜有没有?想把时序讲简单,是不是Mission Impossible?

还是简单总结一下:

1、共同时钟总线时序关系随着速率增加,时钟周期减小,设计难度增加

2、共同时钟总线时序是对总长的要求,一般情况下可以理解为尽量走短;没有等长要求。

3、如果因为时序调整的原因,需要绕线的时候,尽量保证长线不要绕的更长

4、100M以上的共同时钟总线,建议进行时序计算,避免风险

上一篇《 PCB设计十大误区-绕不完的等长(二)》文章不知道大家有没有看晕了,讲时序确实是吃力不讨好哈。看看上一篇文章大家的回复:

@南昌米粉-萝卜妈:最大还是受限于Tco,一般2点几个ns,速率越高时序越难满足,所以共同时钟就升级为源同步,信号时钟从同一个芯片发出。

@绝对零度:主要因素是时钟的串扰,数据的Tco难以减小。解决方法就是使用源同步时钟系统,和差分时钟。典型应用就是DDR。

@山水江南:共同时钟总线的数据时长与时钟时长不匹配,还受时序偏差最大的通道影响,如:时钟偏差、数据偏差、Jitter、串扰等。使用源同步时钟,让时钟和每Bit数据一起发送,消除时钟和数据的偏差。

@Erick:随着频率的提高,共同时钟的限制因数有如下:时钟到达两个芯片的clock skew,数据中各个data的skew,以及clock和data之间的skew越来越难控制. 采用源同步时钟,可以有效解决clock skew,而且clock 和data采用组内差分走相同路径也可以解决clock和data之间skew. 但是源同步受限与clock频率的提高来提升带宽,这样就要讲讲内嵌时钟的大serdes了。

上期问题:影响共同时钟总线速率提升最关键的因素有哪些?行业是怎么解决这个问题的?(提示:内同步时钟和源同步时钟)

看来大家还是有不少人说到了重点的:

既然Tco是影响共同时钟总线速率的重要因素,那么有什么办法可以解决这个问题呢?

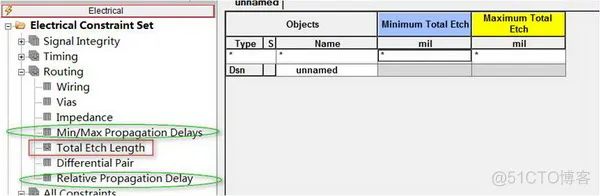

工程师的创新力是无穷的,解决办法也非常简单,不再用外部时钟来同步数据了,而是时钟和数据一起往前走。你数据发出有Tco延时,我时钟发出照样有Tco延时,于是两个Tco就抵消了。晕了?我们看图说话,如下图所示:

这样的方式就是源同步时序总线,由于Strobe和Data一起出发,一起行动,解决了时钟触发的延时(Tco)问题,也一起克服路上遇到的艰难险阻(T Flight Time)。这个方式是不是很像生活中理想的夫妻模式呢?

这种情况下,走线的长短已经不是问题了,反正我们步调一致。对了,关键就是步调一致,反映到走线,就是尽量等长。再次借用 Cadence Allegro的规则管理器来解释,源同步时钟总线最合适的电子规则就是我们常用的Propagation Delay啦。

如果我们把源同步时钟总线比喻成夫妻生活,步调一致,一起克服困难;那么返回头看看共同时钟总线,是不是可以理解为恋爱时候的关系呢,虽然男女之间的目的是一致的,都是到达接收端(结婚),然后有一定的裕量(生活)。但是由于没有达成信任与默契,需要更多的外部条件来协调。然后女生对男生说,不管你有多好,基本条件(房子车子)是要满足的,这就是Total Etch Length的要求,你必须满足一个最大最小的范围条件。

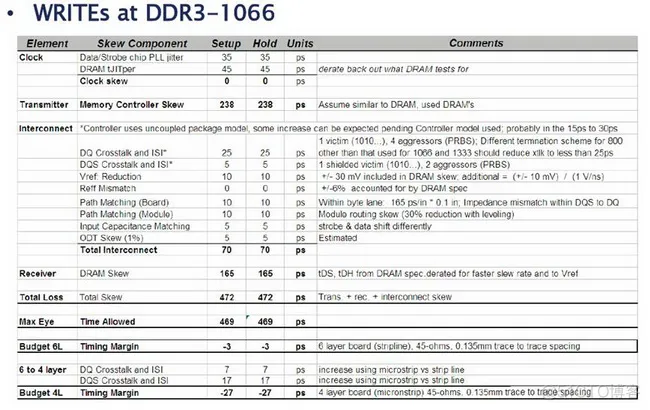

DDR是典型的源同步时序,我们就以DDR3为例,详细说明下DDR设计需要满足的时序关系。

上文说到,源同步时钟的目标就是Strobe和Data一起到达,然后满足到达之后的建立保持时间关系。按照这个目标,只要Strobe和Data等长设计,好像DDR的速率提升就不是什么问题了。不去说什么能不能跑到10Gbps或者更高速率,至少在DDR3的1600Mbps不会有什么困难。总共一两百皮秒的建立保持时间需求,就算加上derating的数据,对于1.25ns的Tck来说,好像都不会有任何问题。

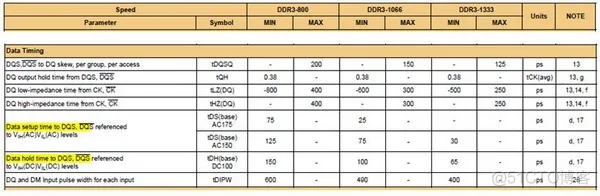

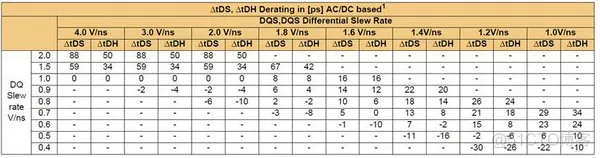

但是下面这张表格告诉我们,源同步时序系统速率提升之后,除了Tck变小会让时序裕量变小之外,还有更多其他因素会影响时序。

码间干扰(ISI),数据线之间的串扰(Crosstalk),还有同步开关噪声(SSN)等,都会吃掉大量的时序裕量。

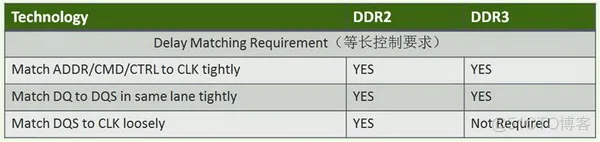

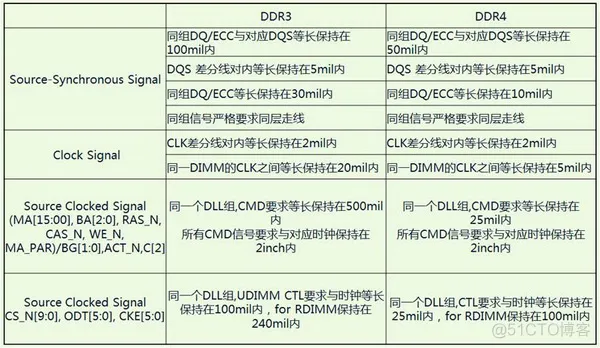

所以在设计中,我们要遵循下面的分组等长原则(DDR3的DQS和CLK不需要用绕线等长的方式来控制时序,而是通过芯片内部的读写平衡功能,我们在DDR3系列文章中已经多次提出来了)

说了“围殴”话题的时候,大家各诉己见。

观点可以百花齐放,话题可以争议性质!

诚征各路英雄参与,微信群同步展开讨论!

所以第一个争议性话题来了:等长越严格, 时序裕量越大,系统越稳定!

这句话应该有很多硬件工程师是同意的,所以我们也经常能看到类似的规则:

……

类似的规则还可以衍生为:

……

类似的规则,用现在最流行的话来说,应该就是“理都懂”,但是臣妾做不到呀!

这里忍不住要吐槽一下:随着 PCB设计这个工种慢慢从硬件设计中独立出来,大部分公司里面PCB设计工程师和硬件原理工程师不是同一个人。所以有些EE会想当然或者很理直气壮把很严格的规则提交给上下游,反正需要 绕线的不是我……更不用说外包的PCB设计了,更是占住了甲方的位置,你们给我往死里绕线。

当然,更多的硬件原理工程师并不是这么想的,只是当这个项目落在自己头上的时候,战战兢兢,如履薄冰,想把一切事情做到完美。

这篇文章,就是为后面这种工程师写的。继续往下看之前,先分享一篇摘自SI-List的讨论。我最喜欢里面的一句话:

http://www.edadoc.com/cn/TechnicalArticle/Show.aspx?id=780

"We are engineers. We are supposed to think."

也喜欢文章里面说的,搞清楚什么是“Design Guide”,什么是“Spec”

之前的文章有提过,所有的等长都不是目的,设计的目的是等时。所以我们首先要知道,+/-10mil对应的时间是多少?貌似+/-1mil等长比+/-10mil严格了10倍,我的时序裕量会不会好很多?

大家应该还记得高速先生王锐写的那篇文章:《 信号是怎样传输的》,没看过的可以翻出来再看看。文章的最后,给出了一个案例:同一种阻值的走线,微带线时延是145.9ps/in,带状线时延为173.6ps/in。

我们需要记住的值是每英寸145~170ps,对于带状线来说,每ps延时对应的走线长度是6mil左右。所以,+/-10mil等长和+/-1mil等长,在时间上的差异不超过3ps。再回头看看我们的系统,有多少是真正需要3ps裕量的?

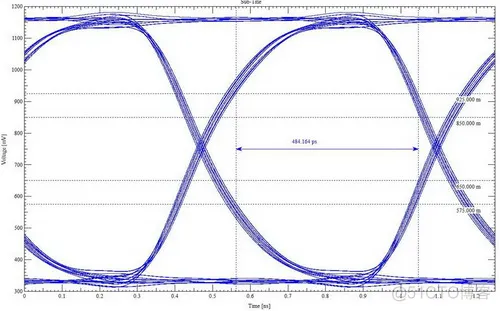

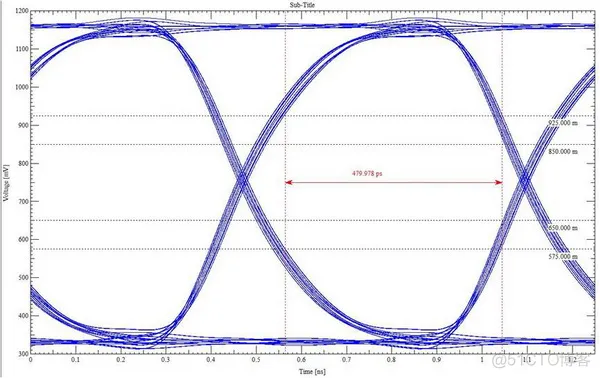

上图是同一个波形,不同的两个人测量的时序窗口大小,有4个多ps的误差。测量的波形也是一样,大家都有这样的经验。

高速先生有时候为了说服一些客户不要纠结在等长是1mil还是5mil,或者劝告说完全等长是没有意义的,我们也是拼了,下面是我们用过的一些比喻:

如果你能理解以上比喻,那么应该可以理解:

大部分的系统,不管是DDR3的数据分组还是PCIE3或者10G Base KR的差分对内,等长做到5mil已经足够了。速率更低的系统,还可以放宽更多。

这篇文章的篇幅已经比较长,所以主要讨论等长不需要过度考虑这一个问题点。另外一个相关的话题是:严格等长会不会带来负面影响,会不会成为系统失效的根源。这个话题我们稍后单独讨论,大家也可以就此提出自己的意见和建议。

1、 串行总线来了

绕线话题从开篇到结尾,花了好几个月哈,老是出差,没有时间静下来写东西。不过或许出差也只是借口,而是因为时序绕线这个话题实在是有点难写好吧。不管怎么说,挖下的坑是一定要埋上的,今天就是绕不完的等长的最后一篇,串行总线来了。

上一篇文章发出来之后,不少网友回复说,DDR3的同组数据并不需要做到5mil等长这么严格呀。看到这样的回复,高速先生们都是热泪盈眶:“同志,见到你真好……”。说实话,写这个系列文章还是有点私心的,希望以后不会再收到客户提出的+/-1mil,+/-0.5mil等长这样的要求,我们已经是很满足了。+/-5mil或者+/-10mil,这已经不是个事了,咬咬牙,加点班,这个等长我们就忍了。

到了串行总线,貌似速率更高了,大家对等长的要求也更严格了。那么串行总线到底是什么鬼?

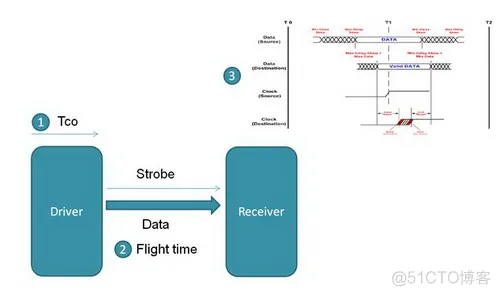

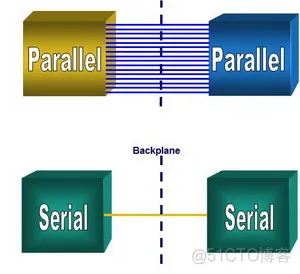

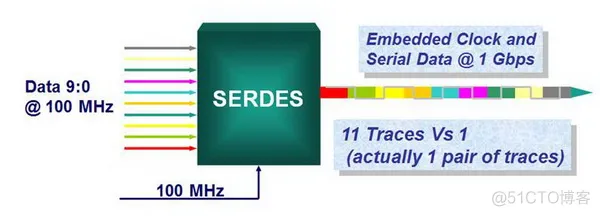

高速串行总线的技术核心是SerDes技术,也叫SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),(Deserializer)也称为接收端Rx。下面一张图,轻松看懂SerDes的工作原理。

篇幅关系,也是高速先生的风格,我们不去解释SerDes的工作原理细节,从上图,我们只需要看懂:

· 时钟是内嵌在差分对里面的

· 到了接收端,时钟信号被重新恢复

2、 高速串行总线(SerDes)的等长要求

从上文可以很容易得到结论:高速串行总线技术采用 时钟和数据恢复技术,从而解决了限制数据传输速率的信号时钟偏移问题,减少布线冲突、降低开关噪声、更低的功耗和封装成本等。所以差分对与差分对之间基本没有等长要求;时钟是依赖串行解串的技术进行传输与恢复。

高速串行总线设计的难点从传统的时序问题,变成自身的Jitter,误码,损耗衰减等问题,关注的重点是差分对本身的信号质量,以及尽量避免受外界干扰影响。

差分对自身的问题,包括:

1、对内等长带来的相位问题以及差模共模模态转换

2、差分对间的串扰问题评估及优化

3、导体损耗,介质损耗等高频损耗问题

这些话题里面,差分相位及模态转换是绕线和走线拐角关注的问题点,会在这个时序系列里面进行探讨。其他问题则会在以后专门的高速串行总线系列来进行讨论。

注:说到高速串行总线基本没有差分对与差分对之间等长要求,需要注意的是差分线不完全等于高速串行总线;换句话说,高速串行总线基本都是差分形式,但是不是所有的差分线都是高速串行总线。

如果差分线不是高速串行模式,而是并行总线,等长设计按照之前导论的并行总线原则来执行(比如传说中还没有推出的差分版本DDR4)

既然说高速串行总线基本没有差分对与差分对之间等长要求,那么就还是有特例:

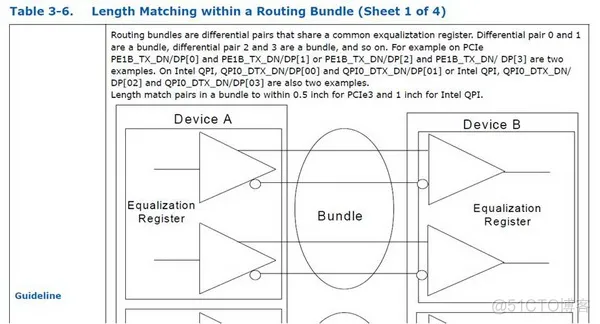

Intel的PDG里面,对同一Bundle内部的PCIE3信号和QPI信号提出了等长要求。不过这是一个很宽松的要求,正常的布局布线设计,基本是不用考虑绕线这个事情的。

回顾一下之前文章的要点,温故而知新嘛,现在不都是流行重要的事情多说几遍吗?

1、共同时钟总线的时序要求,不是等长,而是满足一个范围,更多的时候,需要注意不要走线太长。(这时候男女还没结婚,步调不一致,等长没有意义,大家看的是外部条件,需要满足一个基本要求)

2、源同步时钟总线的时序要求,主要是分组等长。但是等长只是满足了静态偏移,做到几个ps已经是足够好了(+/-10mil左右)。影响更大的是动态偏移,也就是SSN,ISI,Crosstalk等,不要过度强调等长(+/-1mil),而忽略了其他更重要的设计要求(这时候男女已经结婚了,步调一致最重要,只要夫妻齐心,Tco,飞行时间那都不是事。但是外部的风雨还是会影响感情,担心来自于电源噪声、串扰的影响)

3、高速串行总线,时钟内嵌,差分传输,更关注信号自身的品质,外部的干扰已经很难影响到时序了,需要关注差分线自身的设计质量(男女经过磨合,达到了灵魂伴侣的层次,只要两人同心,一切外部的事那都不是事了,所以关注的重点变成两人是否同心 - 差分)

文:王锐

"时序"话题继续殴,说好的围殴一个话题,要殴就殴他个精神抖擞,殴他个四脚朝天,殴到大家爽为止……

相信大家还有印象,在文章《PCB设计的十大误区 - 绕不完的等长4》末尾,提出的问题是:有哪些因素会导致实现了等长设计,却没有等时?高速先生把大家的观点综合之后给出了评论,其中影响较大的因素有同组不同层、过密的蛇形绕线、跨分割、玻纤效应、封装长度等。

对很多有刨根问底精神的网友来说,读到这里大概就会产生这样一个疑问:高速先生,那这些因素对信号传输延时到底有多大的影响呢?求明示…

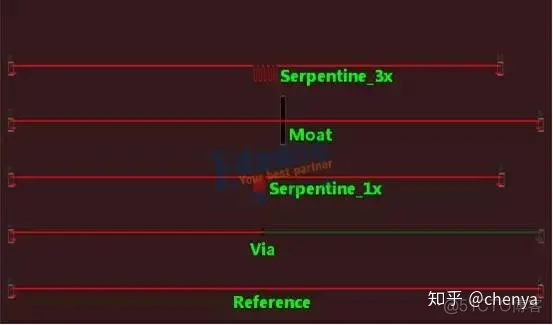

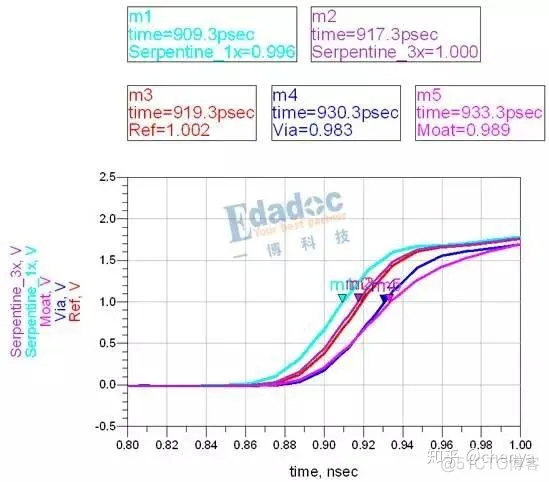

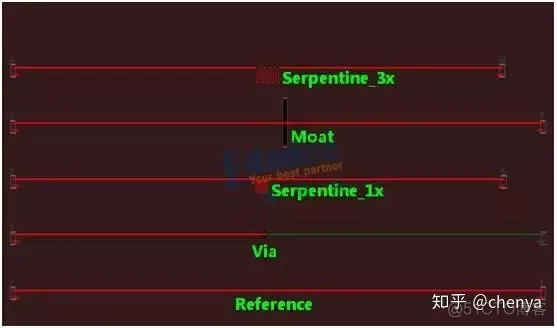

针对此问题,高速先生模拟了下列五种情况来进行对比,五种情况分别是:

1.Reference(6inch 50ohm的微带线)

2.Via(6inch 50ohm的微带线,中间有一个表层到底层的换层孔,过孔长1mm)

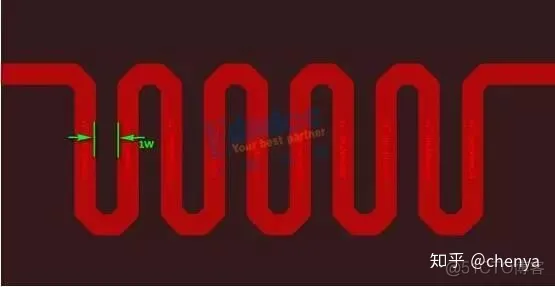

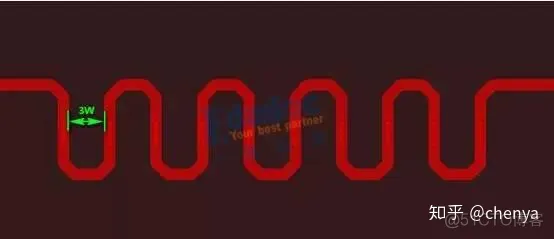

3.Serpentine_1x(6inch 50ohm的微带线,其中有500mil蛇形线,蛇形线间距为1倍线宽)

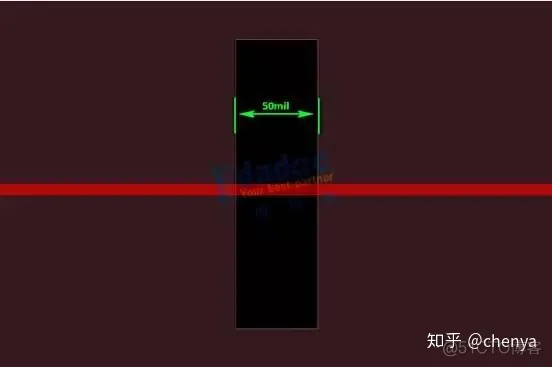

4.Moat(6inch 50ohm的微带线,微带线横跨一个50mil的分割线)

5. Serpentine_3x(6inch 50ohm的微带线,其中有500mil蛇形线,蛇形线间距为3倍线宽)

直接看仿真结果:

Via与Reference的时延差:m4-m3=11ps

Serpentine_1x与Reference的时延差:m1-m3=-10ps

Moat与Reference的时延差:m5-m3=14ps

Serpentine_3x与Reference的时延差:m2-m3=-2ps

当我们还在为5mil,10mil的长度差异而苦苦绕等长时,10ps、20ps的时延差异难道还不能引起我们的足够重视吗?!

预知后事如何 且听下回分解。下期将分享:为什么会出现此类时延差异?

问题来了:信号跨分割会给信号带来什么影响?为什么?

文|王锐

上期文章,高速先生模拟了五种情况做对比,同时也给出了时延差值。下面我们来看看,为什么会出现此类时延差异?

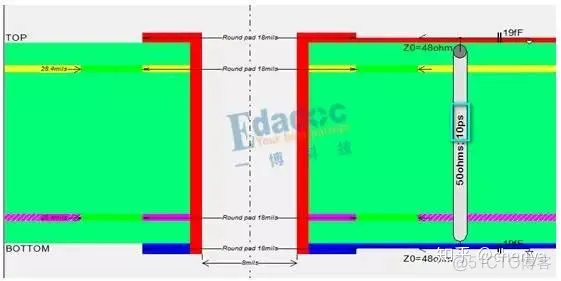

Case1:过孔带来的时延差值为11ps,这个就很好理解了,过孔有一定的物理长度,该过孔长1mm,过孔本身还具有寄生电容和寄生电感,所以实际带给信号的传输线延会比普通传输线要大,本例中是11ps,而且这个延时跟频率有一定关系。使用软件单独提取该过孔的模型,如下图,过孔的延时为10ps,与仿真得到的11ps差不多。

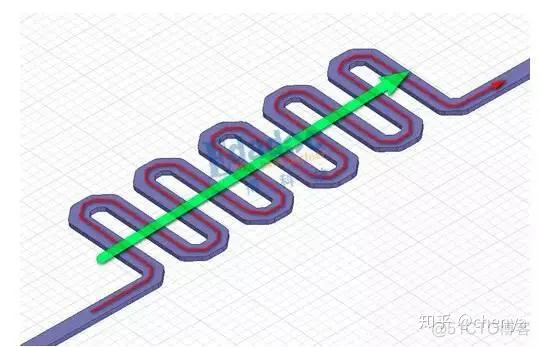

Case2:1倍线宽的蛇形绕线带来的延时差异是-10ps,比参考线快了10ps,造成延时差异的主要原因是信号的自耦合现象。在绕蛇形线的时候,期望的信号传输路径是沿着下图红色箭头传输,可是由于蛇形线之间的距离太近,导致信号实际传输路径是下图绿色箭头所指示的那样(当然,实际上信号也不会以绿色箭头那样传输,在这里这么标注只为了大家更形象的理解记忆,后期会有详细解释)。所以就导致了信号提前到达接收端。

如果把蛇形线之间的间距拉开,比如从1倍线宽拉到3倍线宽,信号的延时差异立刻缩小到-2ps,差异就没有那么大了。所以在使用蛇形线匹配长度时,要注意蛇形线之间的间距一定要拉开,拉开多远可参考下图

Case3:当参考线跨过50mil的分割线时,带来的延时为14ps。在PCB设计中,同一层的平面常常会因为不同的用途而分割开来,由此就会导致很多分割线。众所周知,传输线由信号路径和返回路径组成,信号的返回路径通常在距离信号路径最近的参考层上,且在信号路径正下方(如下图红色圆圈)。如果跨过分割线,信号的返回路径被切断,信号就要寻找其他的返回路径回流,因此信号的回路面积就增大(如下图蓝色圆圈),传输线延时就会增大。

问题来了:有哪些办法可以增大过孔的电感效应或者减小电容效应,从而达到增大过孔阻抗的作用?

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。