研发更多地关注产品本身的性能,还要通过thermal、reliability、S&V、EMI/EMC等一系列测试,拿到FCC、CE、BSMI、KCC等一系列安规证书。而测试点对于这些几乎没有帮助,当然较重要的是增加了研发工作量和设计复杂性。因此对于研发来说,如果没有调试、检测的需求,根本没必要加这些TP。

而工艺/品质更多地关注生产或量产时的良率,确保ship到客户手里的产品没有质量问题(这对企业来说非常重要),所以一定需要完整的流程和机制去检测产品潜在的不良,ICT、FCT、OQA都是其中的一部分。对于工艺/质量管控部门来说,产品设计就应该是DFM(Design for Manufacture),DFT(Design for Testing)的。

说了那么多,到底是否所有的板子都需要加测试点,怎么加呢?

要回答这个问题,首先要明确加测试点目的,不能为了加测试点而加测试点。

测试点的用途主要有以下三类:

不同目的加测试点的策略是不同的。

研发阶段,需要加哪些测试点?

可能会有工程师说:我干了研发那么多年,还从来没有添加过测试点,调试的时候,直接从器件管脚或者过孔处测信号。

先不论这些“点”严格意义上来说本来也属于测试点,每次调试的时候,都要去数芯片上的管脚号,然后到处去找万用表可以“下针”的位置,是不是很麻烦?碰到QFP、BGA的器件是不是更麻烦?

因此合理的添加测试点还是有必要的,当然只需要给“感兴趣”的信号添加测试点。以下是推荐的需要添加测试点的网络:

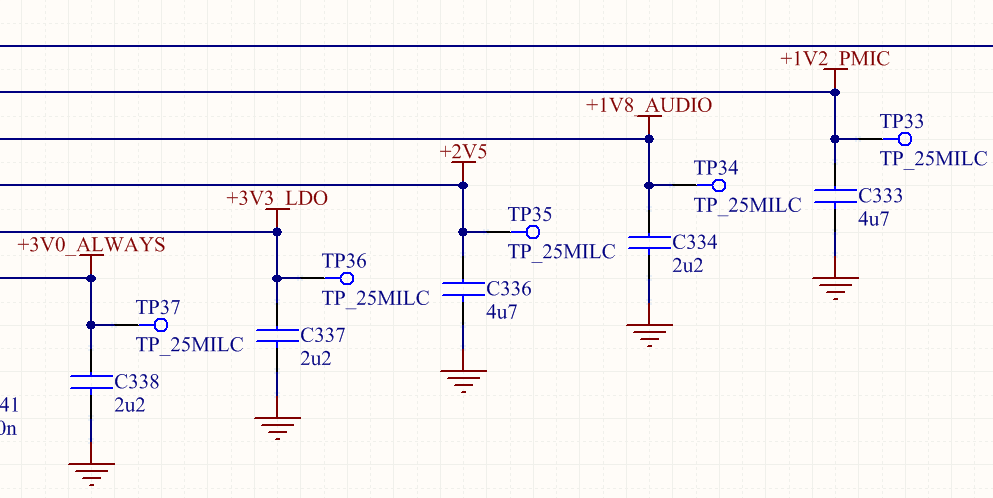

电源

如果你收到第一块prototype的PCB,你会测什么信号?如果板子工作不正常,你会先检查什么?没错,绝对是电源,给所有的电源网络都加上测试点很有必要。

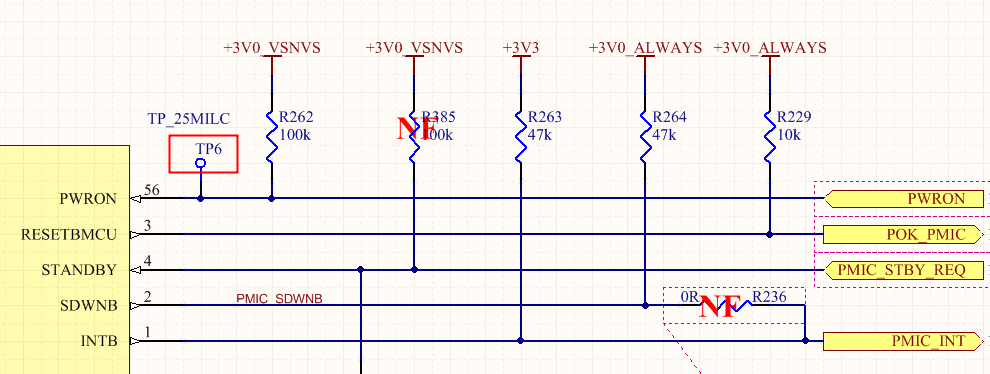

重要的控制信号(Control Signal)

比如说,电源管理芯片的PowerOn(Power Enable/Power OK)的信号。给重要的控制信号加测试点,便于我们观察信号的时序,帮助我们分析板子不正常工作的原因。

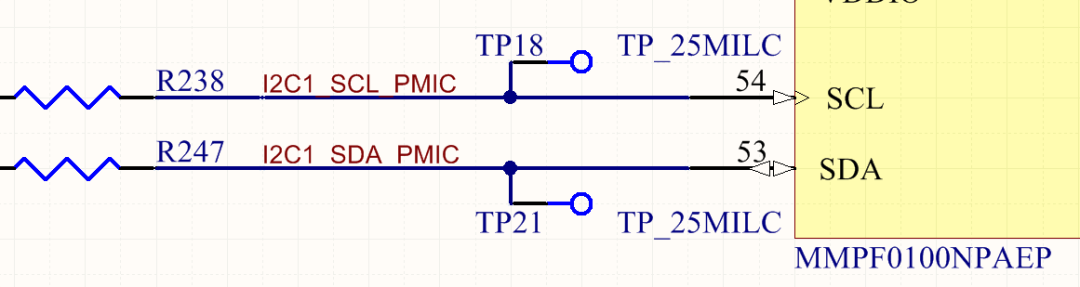

某些需要与外部接线的信号

比方说下图中的I2C信号,添加了两个测试点,可以用于与外部编程器相连,给右侧的芯片进行编程。

除此之外,其他的工程师认为重要的信号也应该添加测试点。

量产阶段的ICT是什么?

回到本文开头的那个问题,是不是所有的产品量产时都需要满足每个网络至少有一个测试点的要求?这主要还是取决于量产的规模,如果年产量达到kk级,那毫无疑问需要通过ICT快速地检查PCBA的品质。如果量产的规模较小,很多公司会通过FCT阶段跑一些Diagnostic tool或测评软件来判断产品的好坏。

如果选择了ICT,理论上每个网络确实至少应该有一个测试点。对于工控板、白电等PCB面积相对富裕的产品,这个要求很合理。但对于手机、电脑主板等走线密度较大的产品,有时100%是不可能实现的,因此才会变通出”Critical Net覆盖率100%”的说法,至于哪些网络是critical的,那还不是研发说了算:P这里花些时间说说ICT,这个对于理解测试点如何设计很有帮助。

ICT理论知识

ICT是In Circuit Test的简称,其功能类似于一块万用表,在产线上可以快速、批量地对PCBA进行测试。ICT测试靠探针接触PCB Layout时的测试点,来检测PCBA线路的短路、开路以及器件的焊接情况,并将短路、开路的点准确告诉用户。

和ICT同样用于PCBA检测的还有AOI(Automatic Optical Inspection)以及FCT(Function Test)。AOI是光学检测,通过摄像头将扫描出的图像,经过处理,与合格的图像进行对比,给出潜在的缺陷。AOI与ICT相比,优势是比较灵活、不需要治具,但对不可见的焊点无能为力,对于焊点虚焊等情况也无法检测。

FCT是功能检测,通过软件来判断PCBA功能是否符合要求,这也是大部分企业采用的方式,相比ICT,它的更大缺点在于无法给出缺陷的具体位置。对于一些产量比较大的产品,测试成本相对可以忽略,通常会将AOI、ICT、FCT作为多个工位依次进行。

下图是ICT治具的一个参考图:

其中最贵的就是下图中的探针,表面镀金,一整套治具的价格十来万不在话下。

ICT也有个致命的缺点,即市场反应速度慢,因为为一块PCBA制作和调试ICT针床夹具,往往需要花费1周甚至几周时间,并且只能用于这块PCBA。因此现在市面上也有飞针测试仪,相对ICT更灵活,可以编程实现飞针的快速切换,但缺点是测试速度慢。所以ICT现在仍是产线上的主流检测方式。

测试点设计规范

由于ICT的探针的机械限制,测试点的设计也要遵循一定的规范。

测试点间距

探针的行业规范为0.100”/2.54mm(价格最低,可靠性高),因此对于这类探针,测试点之间的间距至少为0.100‘’/2.54mm或者更大。如果满足不了这个要求,就需要使用更小的标准探针,如0.075‘’/1.91mm(这种探针也很常用)或0.050’/1.27mm,当然更小的尺寸意味着更高的价格。

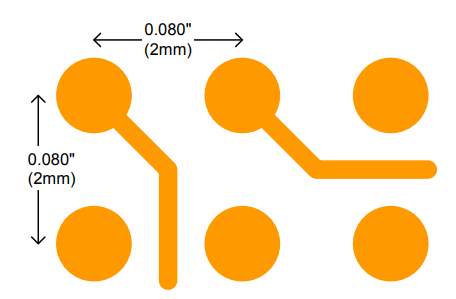

下图是一种测试点间距的设计方法,直接将格点设为0.080‘’/2mm,方便测试点的统一摆放:

测试点尺寸

测试点的尺寸对于治具额可靠性来讲非常重要。有可能的话,TP尺寸越大越好,最常见的TP尺寸是⌀1.2mm,最小的TP建议为⌀0.8mm,再小的话会使探针的成本极具上升。

一般建议企业定义几种规范的测试点,如⌀1mm,⌀1.2mm,⌀1.6mm等。

测试点位置

除了测试点间的间距要求外,测试点的位置还需遵循以下规则:

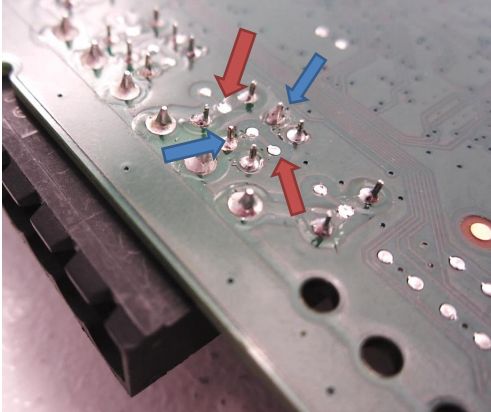

下图是一个设计比较好的样例,工程师并没有把蓝色箭头所指的焊盘锡点做为测试点,而是将测试点引出,提高了测试的灵活性和可靠性。

测试点类型

测试点应该被设计成通孔(through-hole)的还是贴片(SMT)的?

原则上来说,通孔的TP比贴片的TP更有优势。通孔测试点更大的好处在于通孔本身使得探针的中心定位更准确,其次两面都可以下针。但通孔测试点更大的问题在于占用;额PCB所有层的走线空间,这也是SMT测试点更大的优势所在。因此在当今PCB尺寸越来越小的趋势中,SMT测试点被更广泛的应用。

测试点的材质

测试点最常见的材料有以下两种:

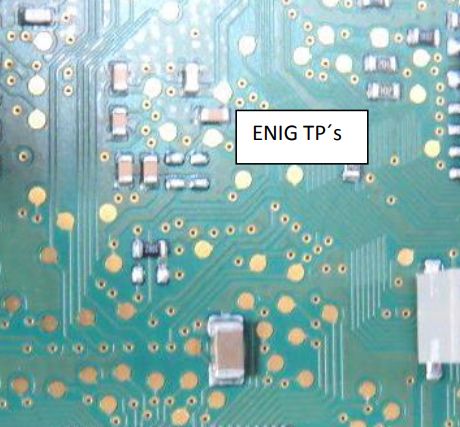

建议使用化学镀金的方式,因为电导率更高,虽然价格略贵。

下图是镀金测试点的一个实例:

Altium中测试点的使用

AD对测试点的支持并不怎么好,只需要记住以下几点即可:

标识测试点

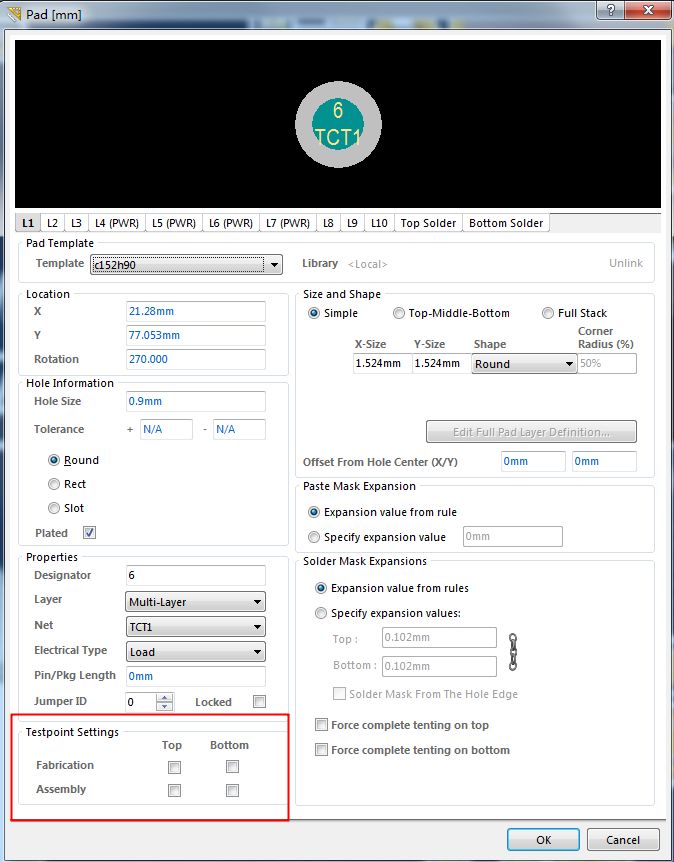

在AD中,双击需要做为测试点的焊盘或过孔,在左下的属性中勾选,以此来定义测试点:

后续标记过的测试点可以生成报告。

测试点相关规则

比较重要的有以下两种规则:

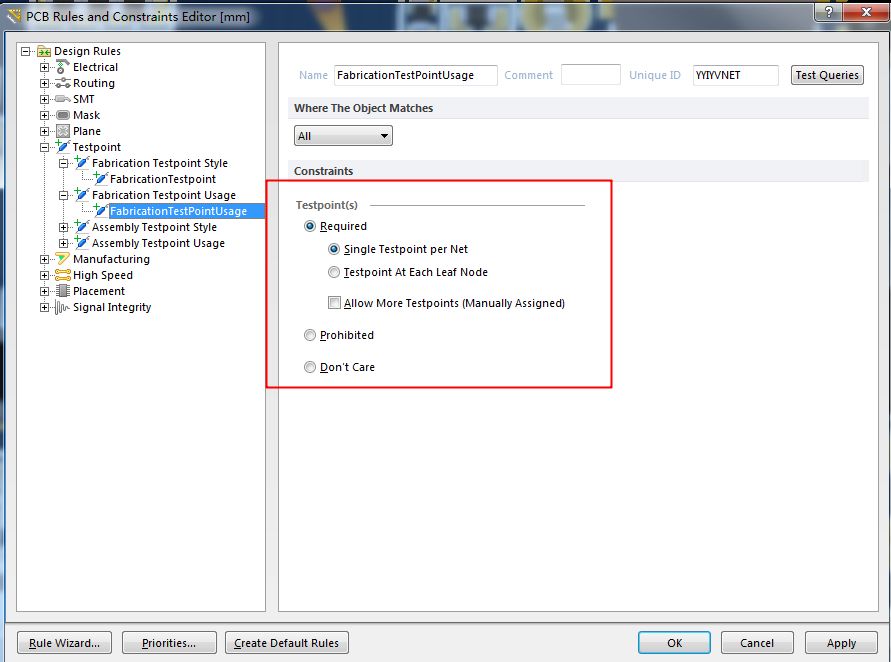

第一个是样式规则,可以在规则中定义测试点的尺寸、间距、位置等。其中间距规则允许定义TP到器件、TP到板边、TP到焊盘或过孔的距离,非常实用(老的AD版本好像没有)。

第二个是使用规则,可以定义是否每个网络都需要一个测试点。运行DRC后,没有添加测试点的网络都会警告提示。

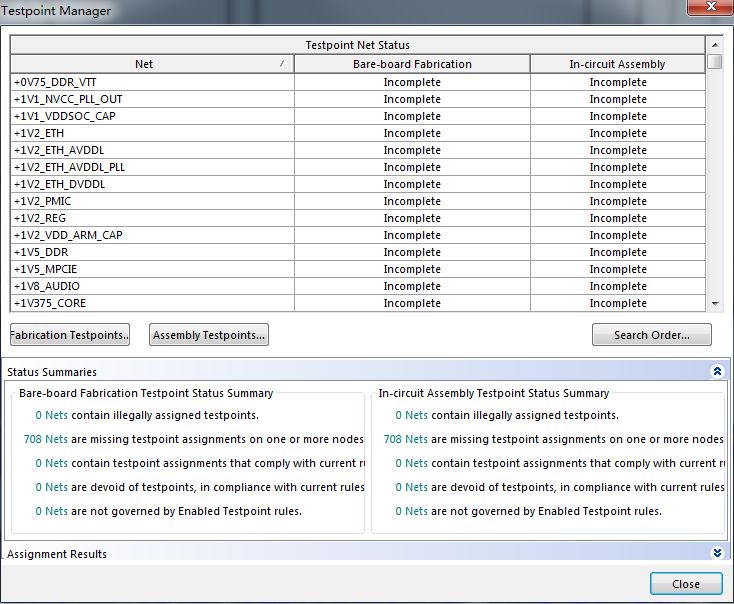

测试点管理器(Testpoint Manager)

说实话这个功能非常鸡肋,除了能给已经存在的Pad/Via添加一个测试点的属性外,啥都做不了。而且添加属性还需要设置格点规则,不容易成功。这里就一笔带过了。

当然电子行业发展太快,很多数据也有可能过时,希望大家包涵。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。