软件

产品

本实验以实现半加器为例。

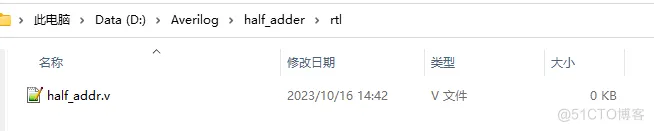

1.建立half_adder文件夹和四个小文件夹

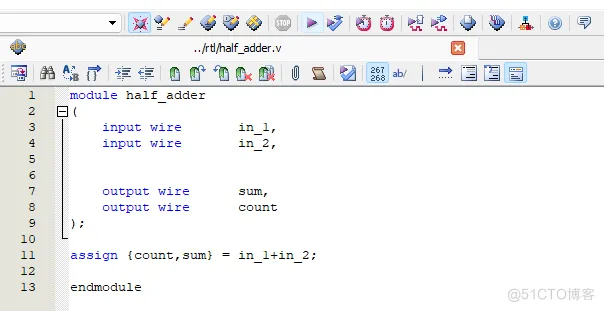

2.rtl文件夹写.v文件,即程序代码

代码实现如下:

module half_addr

(

input wire in_1,

input wire in_2,

output wire sum,

output wire count

);

assign {count,sum} = in_1+in_2;

endmodule

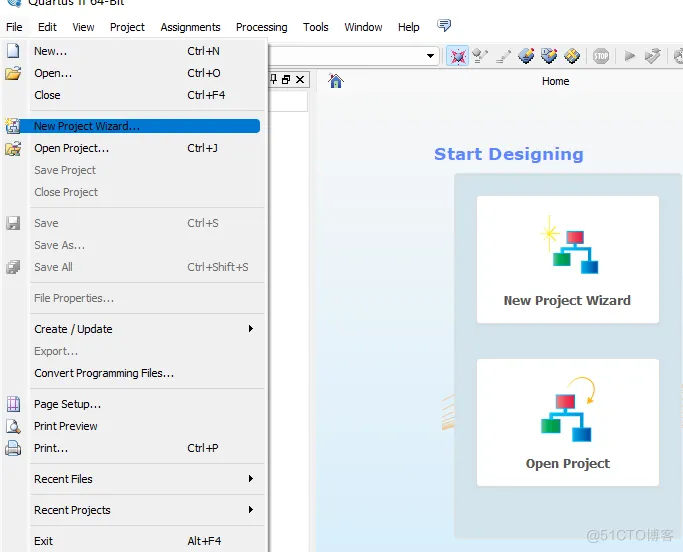

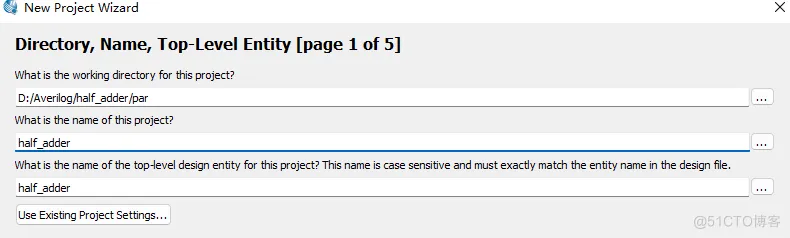

3.打开quartus软件新建工程

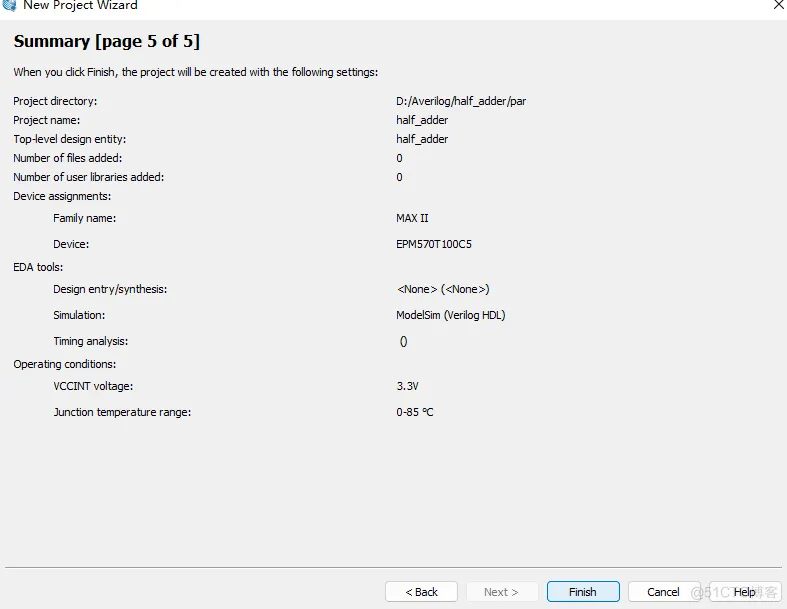

将工程文件保存在之前建立好的par文件夹中,工程名设为half_addr

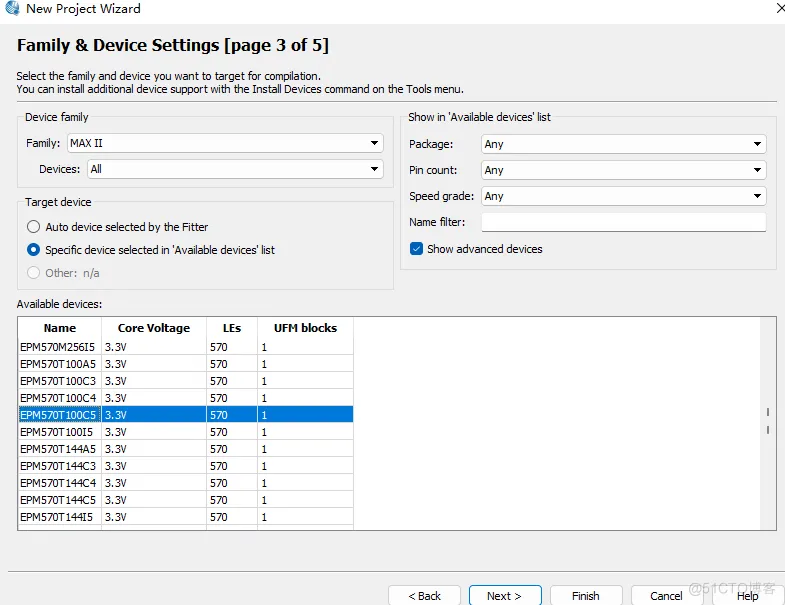

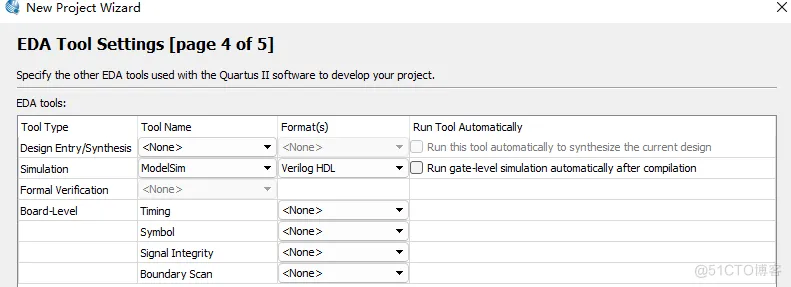

选好自己的芯片型号,再配置相关信息

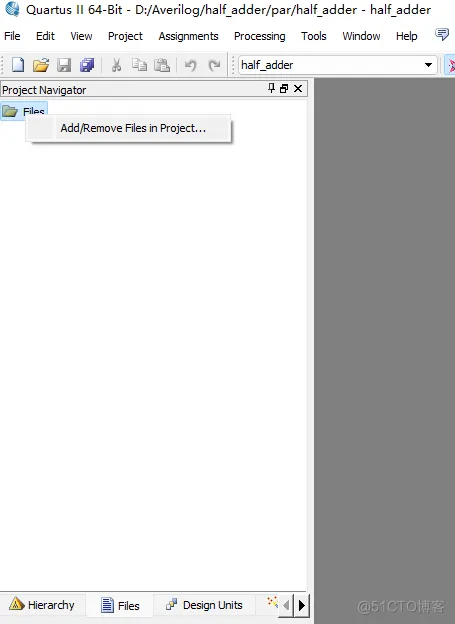

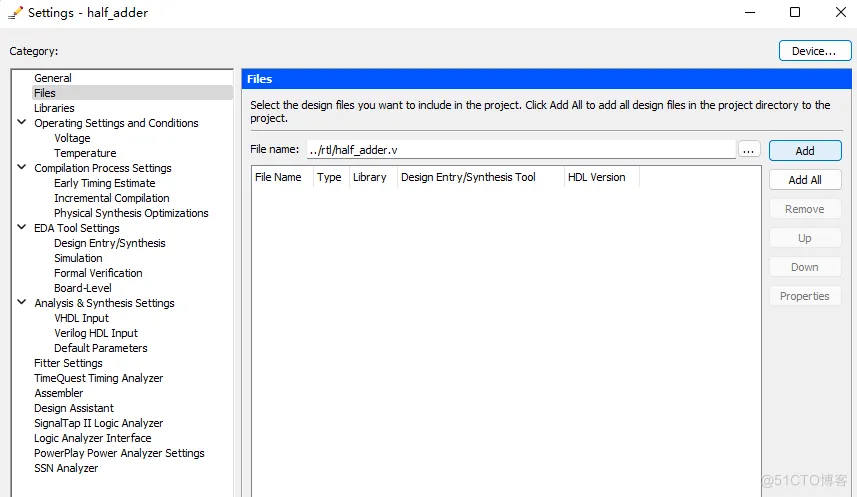

4.添加写好的代码文件

点击add,再点击apply应用,再OK

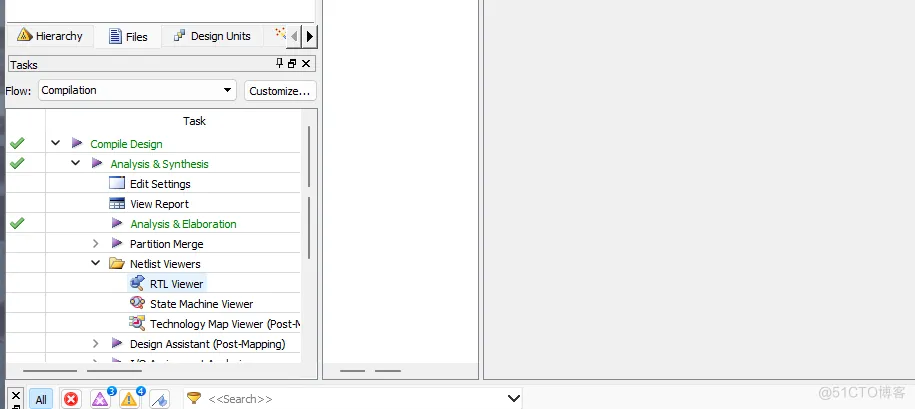

最后编译查找语法错误

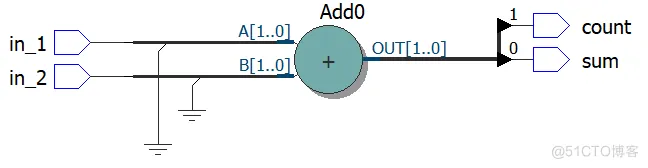

可以查看RTL视图,代码已经被综合成半加器

5.接下来进行仿真

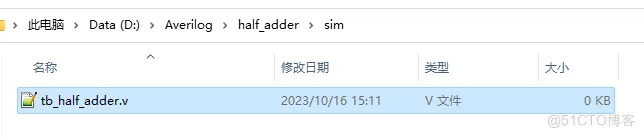

首先在sim文件夹里新建一个仿真文件,进行仿真文件的编写

仿真代码如下:

`timescale 1ns/1ns

module tb_half_adder();

reg in_1;

reg in_2;

wire sum;

wire count;

initial

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

end

always #10 in_1 <= {$random} %2;

always #10 in_2 <= {$random} %2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1=%b in_2=%b sel=%b out=%b",$time,in_1,in_2,sum,count);

end

half_adder half_adder_inst

(

.in_1(in_1),

.in_2(in_2),

.sum(sum),

.count(count)

);

endmodule

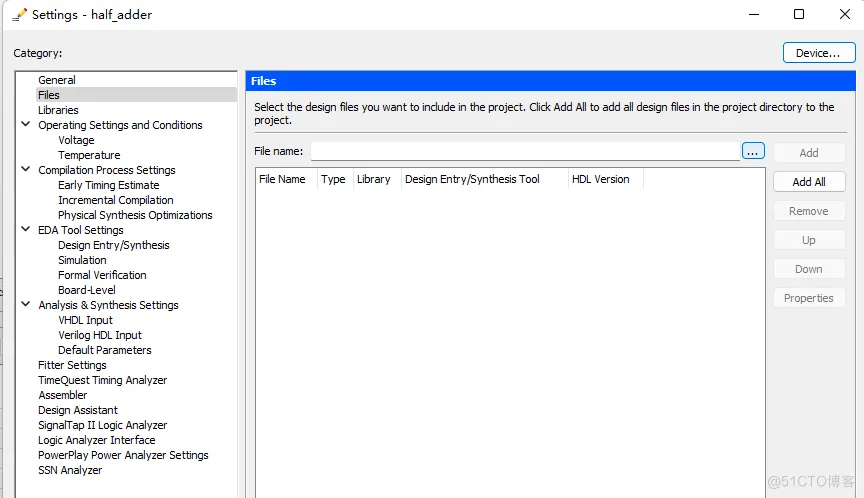

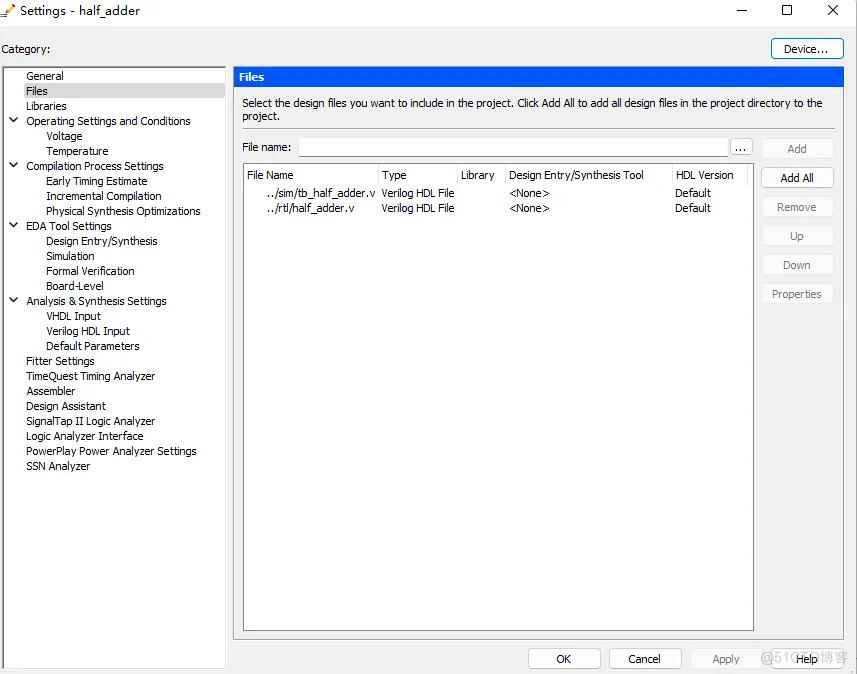

回到quartus添加测试文件,与之前同样的步骤

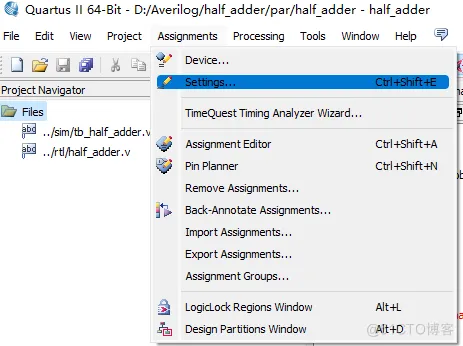

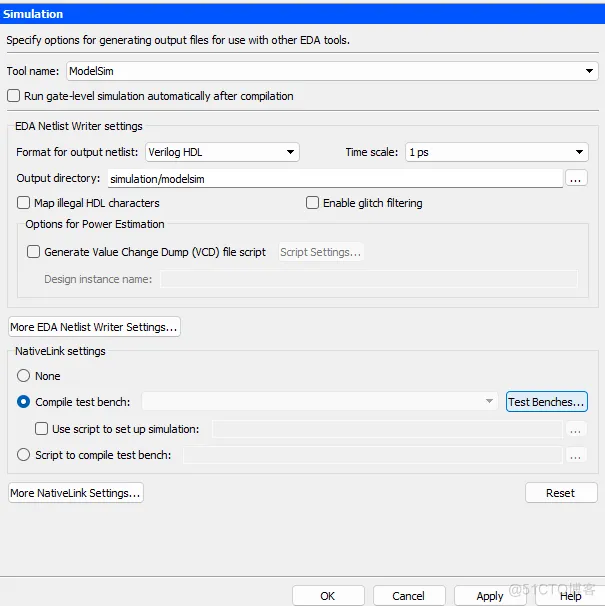

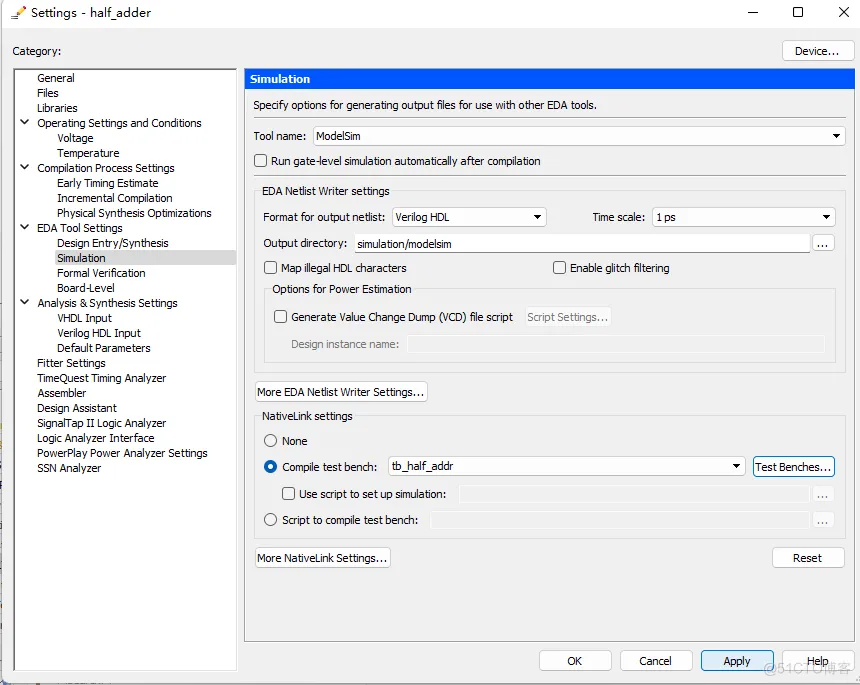

添加完之后进行仿真设置

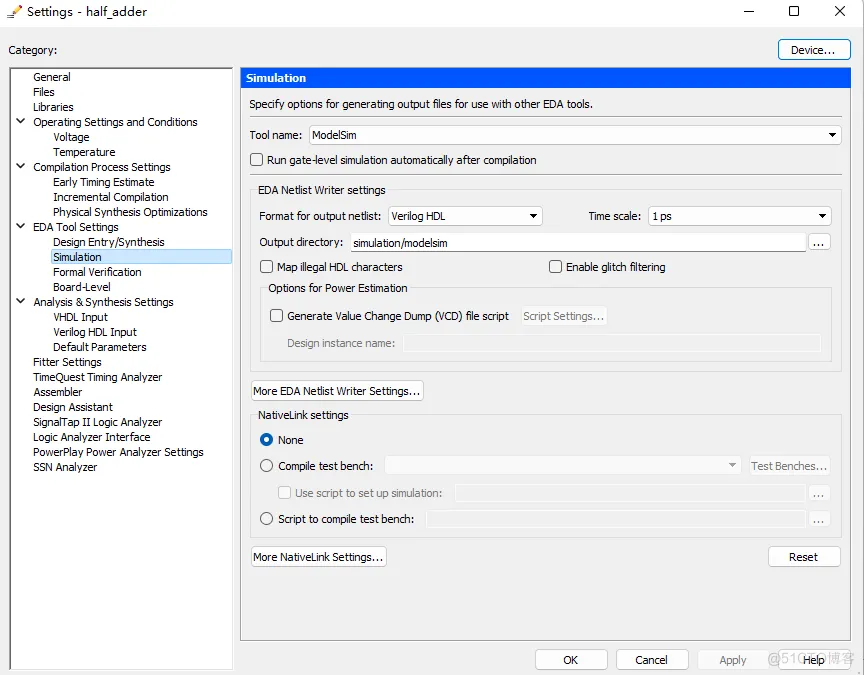

点击左侧simulation那一栏

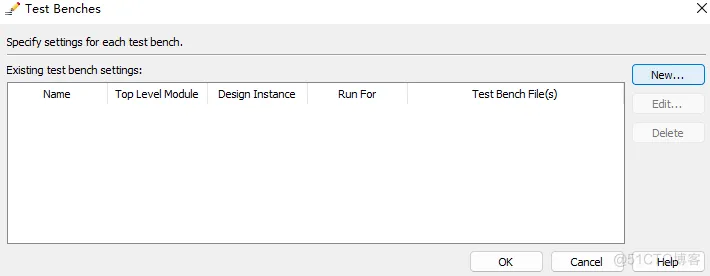

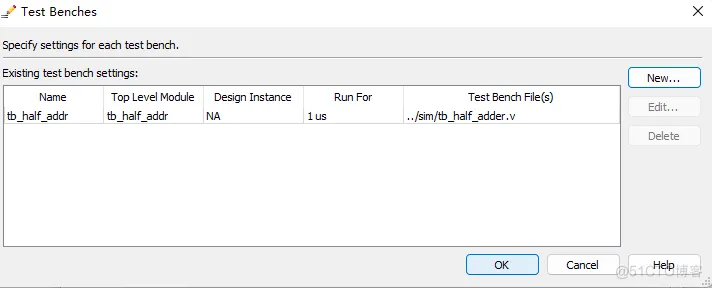

设置正确后添加test benches文件

点击new

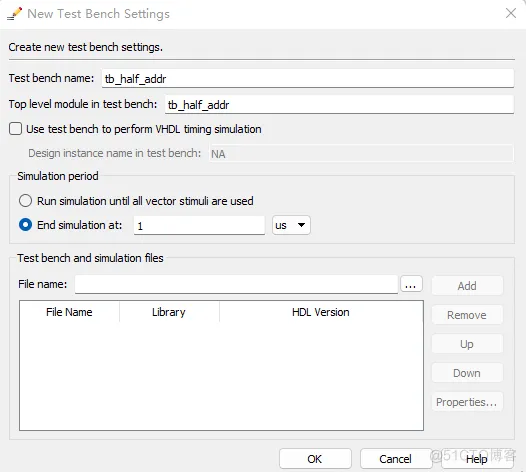

先设置相关信息,注意名称要与测试文件模块名称一致

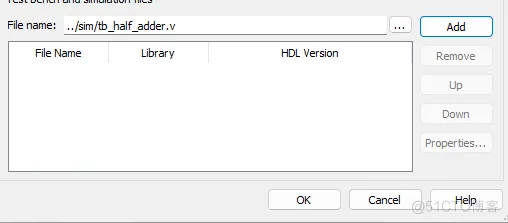

再将其添加,选进,add,OK

再OK

Apply再OK

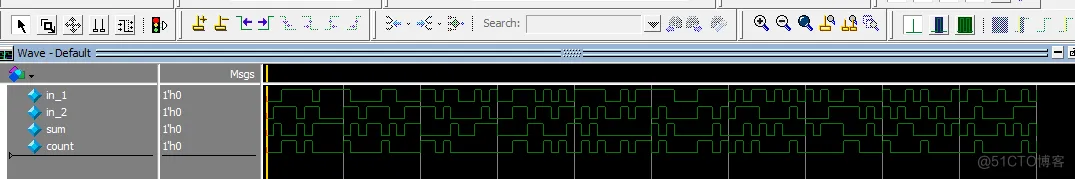

6.直接点击仿真

图像如下:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。