在移动计算和通信技术的推动下,SoC在硅集成技术、先进的低功耗技术以及采用多种封装技术来满足更高的性能要求等方面迅速发展。物联网(IoT)正在为联网设备和系统开辟新的应用领域,其中低功耗、高性能和可靠性成为首要的关注点。由于温度对功率、性能和可靠性会产生巨大影响,因此要求设计师在设计流程中必须要进行精确的热分析。

在FinFET或FDSOI等先进的工艺技术中,导线的宽度和间距减少,电流密度增加,导致导线上的线温度(ΔT)升高。通常,这是导线之间的自发热效应和热耦合造成的,会影响芯片的可靠性和性能。自发热产生的功耗定义为I2R,其中I(电流)可以是电源/地线上的IAVG或信号线上的IRMS。传统方法是使用整个芯片最坏情况下的平均温度来进行电迁移(EM)sign-off。这种方法不仅低效,还没有将热点热量问题考虑在内。因此,在优化导线设计的同时,估算导线的实际温度是保证可靠性的必要条件。由于现代芯片中有着大量的导线,所以在所有导线上应用直接的热场求解方法(如有限元法)是不可行的。本文介绍了一种创新方法,用于高效、精确地计算与自热效应有关的温升对数百万条导线产生的影响。还介绍了兼顾自热效应和芯片封装系统(CPS)热环境的热感知EM方法。

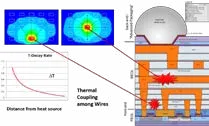

图1:电迁移的热影响

芯片的导线温度是关键数据,用于确定导线上的允许电流,以满足Black方程(图1)中所述的预期平均失效时间(MTTF)。这用于预测金属导线的EM可靠性故障,随着时间的推移会导致不希望出现的开路或短路。导线/器件温度影响功耗(尤其是泄漏功耗,它是温度的指数函数)、电阻、EM限值,进而影响EM、IR/动态压降、信号完整性、ESD和定时。

精确估计导线在数千个时钟周期内的稳态温度需要以下输入:

1、CMOS设备在实际工作状态(即切换模式或空闲模式)下的功耗

2、封装中芯片的热环境,如热导率分布,包括用于三维IC设计的多晶粒加热,以及CPS配置的变化

3、导线的自加热分量,通常由导线之间的热耦合和流经导线的平均或均方根(RMS)电流的功率耗散引起。

通常,设备发热是芯片总功耗的主要部分。芯片级功耗分析工具,如Ansys、RedHawk或Totem生成芯片热模型(CTM),该模型以精细的网格功耗图表示设备加热的影响。Ansys Sentinel-TI是一个有限元工具,用于模拟和求解集成电路封装(如3D-IC)中芯片的热分布。该模型使用CTM功率以及来自板级CPS分析的系统热边界条件,或使用Ansys Icepak的系统级热分析,这是一种使用计算流体动力学(CFD)仿真的系统级热求解方法。CTM包含芯片的总功耗。这包括与温度相关的设备漏电功耗和内部连接层金属分布数据。

尽管芯片内部连接层中导线的自加热只占总功耗的一小部分,但当技术扩展到16/14nm及以下时,导线上的电流密度和电阻都会增加,导致局部自加热和温度显著上升。芯片上的导线段数以百万计,因此很难使用场求解器(如FEM或CFD)求解自加热问题。RedHawk和Totem使用了一种新颖有效的方法来计算导线的温升以及热耦合效应。为了精确进行EM分析,将CTM流的基础温度与导线上的温升结合在一起,利用包含导线自加热和热耦合的新方法来进行计算。

图2:设备和导线上的自热引起的热耦合

设备和导线上的自加热引起的热耦合如图2所示。利用通用有限元分析工具Ansys Mechanical对埋在介质中的每根导线后端(BEOL)自加热(T)的增加进行预演。预演过程考虑了几何和物理因素。这些因素包括电流、导线的电阻和几何形状、电介质层的厚度、电介质的位置和热导率以及附近金属的含量。介质中的温度衰减行为是计算导线间热耦合的关键。有了T和温度衰减特性,利用线性叠加法就可以方便有效地计算导线间的热耦合。

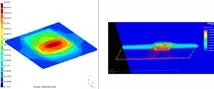

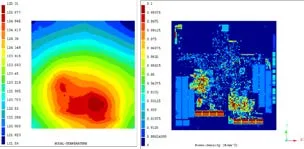

图3:CPS环境中的3D-IC封装(右)和CFD的热边界条件(左)

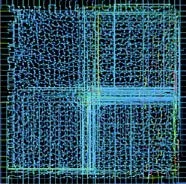

使用Icepak生成的边界条件对3D-IC进行CPS热仿真的结果如图3所示。用有限元和/或CFD场求解器求解CPS导电固体边界外的热对流和辐射。最终的温度感知EM分析是使用高分辨率(图4)和在与实际CPS环境兼容的温度水平进行下的。这种方法允许设计人员在芯片设计sign-off流程中轻松识别和修复超过EM上限的导线。

图4:具有CPS热环境和导线自加热考虑的信号线的EM限制百分数

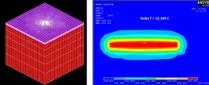

在自加热预表征过程中,采用有限元法对硅衬底介质层中的导线进行了详细的三维建模。图5举例说明了分析模型和导线的典型温度分布,包括进入介质的衰减状态。这种仿真方法为有效预测给定导线的几何和环境配置下每根导线的温升提供了依据。

图5:用于表征电介质层中导线温升的三维有限元模型

使用类似于图6的模型来描述上述仿真的温度衰减行为。通过使用具有导线尺寸、间距、加热导线的高度/位置和衰减方向参数的导线阵列来获得导线之间的热耦合。热耦合分析结果表明,导线内部的自加热会使温度升高。导线的可靠性是芯片最终温度的函数,是使用随温度变化的CTM功率图对芯片-封装-系统的热影响的函数。在CPS环境中迭代之后,温度和功率收敛,显示出连续的温度分布和功率图(图7)。对于多芯片和3D-IC设计,CTM和CPS方法同时提供了芯片上温度分布的收敛性。收敛的热分布与导线热耦合相结合,为温度感知EM分析提供了一个完整的解。

图6:介质层中嵌入的自热导线的温度衰减

由于设备或管线前端(FEOL)加热(图2和图7)而产生的层和导线上的基础温度是基于CTM的热分析(图3)计算的。

图7:来自CTMd FEOL设备功率(右)和作为导线基础温度的芯片层上的热分布

总之,随着包括FinFET在内的先进工艺技术,随着SOC密度的增加,芯片内部的由热引起的电迁移也随之增加,这是一个主要的可靠性问题。

Ansys开发了一种创新技术,该技术利用导线的自加热引起的T和热耦合来精确、有效地计算当今SoC中数以亿计的纳米导线的温度,而不是采用传统的基于最坏情况下的平均温度的方法。Ansys提供一种温度感知EM方法,利用自加热和芯片封装系统热环境,使设计人员能够为移动、通信和汽车等市场制造最可靠的IC。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。