BGA的全称叫做“ball grid array”,或者叫“球柵网格阵列封装”。目前,绝大部分的intel移动CPU都使用了这种封装方式,例如intel所有以H、HQ、U、Y等结尾(包括但不限低压)的处理器。BGA可以是LGA、PGA的极端产物,和他们可以随意置换的特性不同,BGA一旦封装了,除非通过专业仪器,否则普通玩家根本不可能以正常的方式拆卸更换,但是因为是一次性做好的,因此BGA可以做的更矮,体积更小。

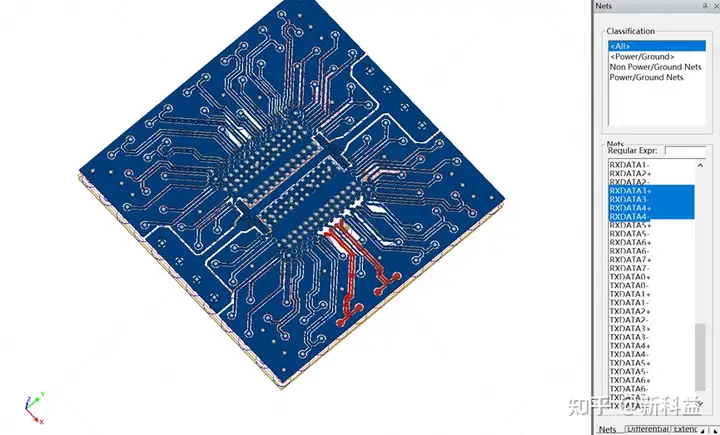

竞争激烈的移动市场迫使设计人员完成极具挑战性的目标:成本更低,但性能更好。芯片-封装-系统(CPS)协同分析作为重要突破手段之一。它旨在使移动AP系统设计人员能够发现并最大限度地减少通过优化每个芯片、封装和电路板级别而永远无法发现的过度设计。在数字接口速度不断提高的背景下,信号完整性(SI)分析成为确保 IC-封装-PCB 实现的必要条件。下边我们介绍ANSYS 针对BGA封装差分信号S参数的提取策略,即借助ANSYS 旗下的HFSS 3D Layout专业3D SI/PI分析工具,来分析BGA的SI问题。本次分析的两对差分信号如下图红色net: (RXDATA3+、RXDATA3和 RXDATA4+,RXDATA4-)

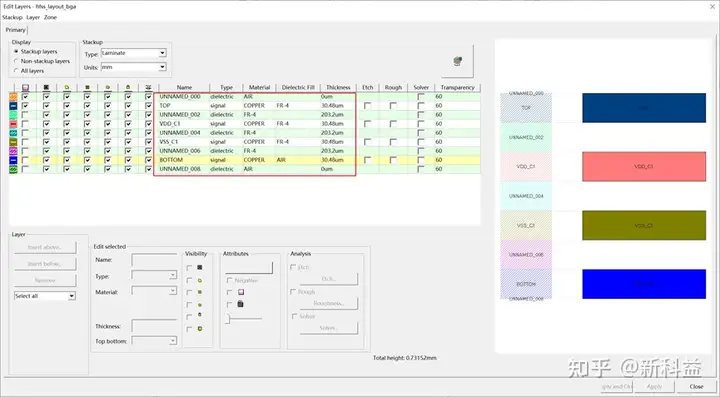

做任何仿真叠层信息的确认是第一步,主要确认叠层的材质、厚度和填充才材料:

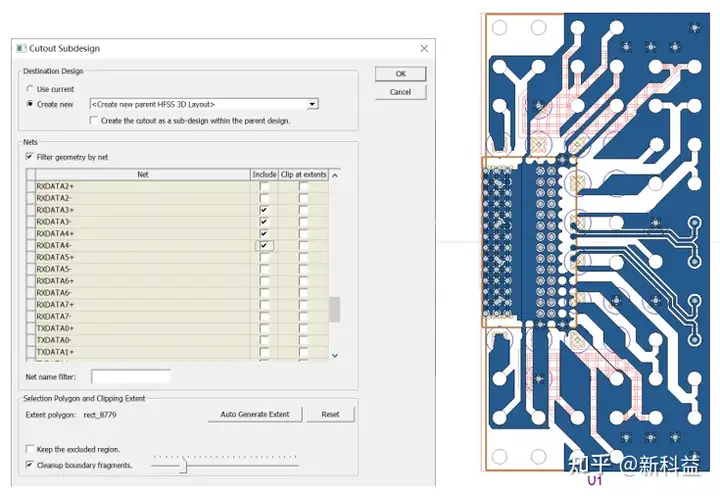

为了节省计算机的计算资源,提升仿真效率,对关键的信号线进行裁剪,从而节省大量的时间和计算成本。在裁剪生成子设计,我们将在“user”层(non-stack)上绘制一个矩形,当然裁剪也支持多边形以及自扩展区域。此设计中的使用矩形裁剪一半后如下:

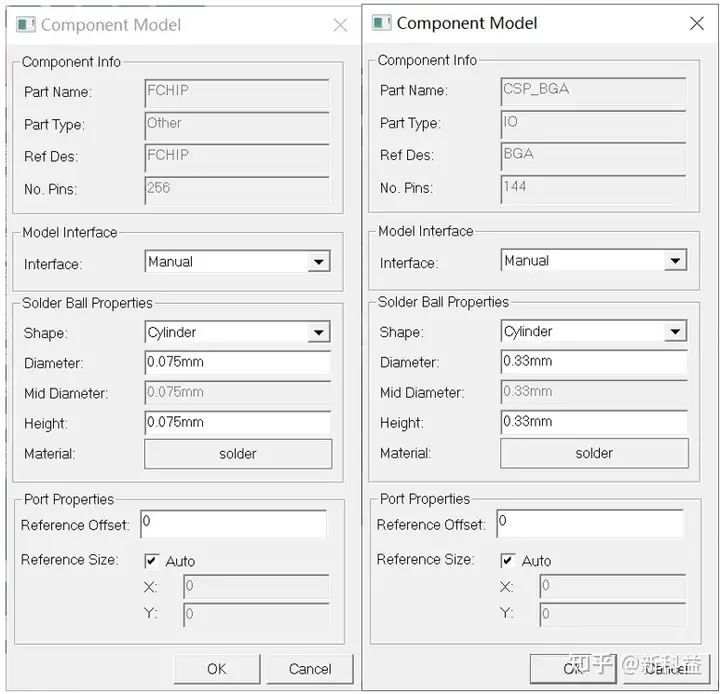

设定FCHIP和BGA的焊球的类型为cylinder,半径分别为0.075mm/0.33mm

生成后如下:

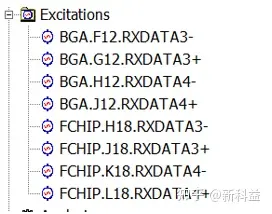

接着为差分对RXDATA3+、RXDATA3-、RXDATA4+、RXDATA4-添加如下八个端口:

添加操作如下:

求解设置,设置求解频率为2.5GHz,扫频范围为0-2.5 GHz。定义空气盒子其中水平和垂直方向扩展0.025,介质层水平不扩展。

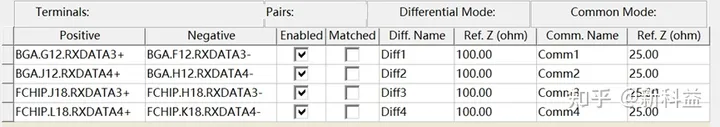

求解后定义差分对如下:

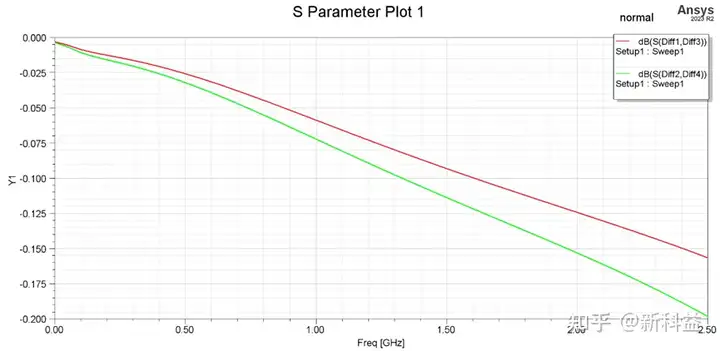

查看其结果,可以发现两对插入损耗非常小,具体如下图:

回波损耗如下:

同样可以观察整个封装的电场强度分布:

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。