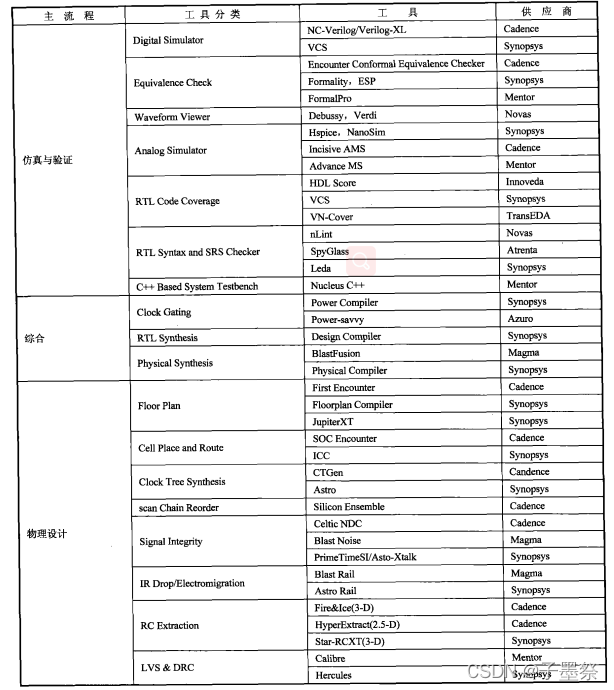

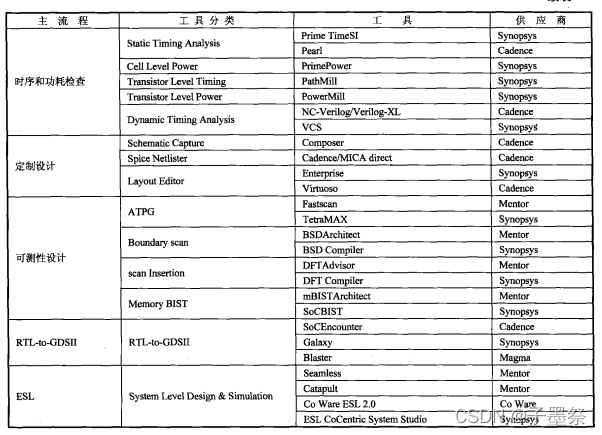

目前主流的EDA软件供应商有Synopsys、Cadence、Mentor Graphics及Magma公司。他们都有各自独立的设计流程和相应的工具,也是提供了独立的ASIC设计的整个解决方案。下表为主要的EDA产品及对应的设计流程:

这些工具各自都有自己的特点和特长,有一些已经成为工业界的标准。例如,Synopsys的静态时序分析工具Prime-time、晶体管级电路模拟仿真软件HSPICE、逻辑综合工具Design Compiler、Cadence的全定制芯片流程软件包ICFB,以及Mentor的DRC&LVS工具Calibre。设计公司应该在设计之前根据自己的需求确定所要使用的工具。

目前,随着EDA软件功能越来越强,各大EDA公司都已推出了RTL到GDSⅡ的完整工具包。这样大大减少了使用不同工具所带来的数据格式不同等问题,如Synopsys的Galaxy平台、Candence公司的SoC Encounter、Magma公司的Blaster等。

对65nm、45nm及以下节点的设计,芯片的功能越来越复杂,工艺尺寸日益减小,设计工程师需要更好的EDA工具,来保证芯片设计尽可能一次性成功。因而,EDA工具的发展趋势是如何解决软件与硬件之间的隔阂,设计与制造之间的隔阂。

1.支持软硬件协同设计的ESL工具

软件挑战是ESL工具发展的关键推动力。对多处理器的SOC和必须并行编程的多线程结构的要求将促使ESL工具进一步发展,来满足单一高级别模型的软硬件协同设计。而用软件来生成芯片的IP将更有效地缩短设计的周期。可以预见,支持ESL到RTL的编译和转化,甚至是直接完成ESL综合的EDA工具也将成为关注的热点。

2.支持良率设计的DFM工具

在90nm及以下工艺,光学效应开始引起设计问题和良率问题。因此除了设计规则,还需要光学仿真来分析工艺变化和分辨率增强光学接近校正的影响,从而可以发现设计规则检查(DRC)所无法发现的问题。另外,在45nm及以下工艺,将引起更多的工艺变异问题,如应力工程的变异,需要将这些工艺变异信息反标回设计阶段,帮助设计人员优化布局并最大限度地提高成品率,由此可见,必将会有更好的EDA工具出现来保证设计可制造和良率。

3.提高EDA工具本身的性能

现有的大规模SoC中包含了上亿个晶体管,使得工具支持尚有难度。通常来说,进行一次验证可能需要几天的时间,严重影响了产品的设计周期并增大了设计风险,因此有必要对于软件本身的性能和算法进行优化和改进。

总体来说,EDA的发展已经成为解决集成电路设计的重要途径。现在集成电路产业发展的主要矛盾是:芯片制造业发达和芯片设计能力的相对不足。而要推动SoC设计,就必须在设计方法和EDA设计工具上有所突破。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。