HDL Designer—设计复用、创建和管理工具

HDL Designer Series 是Mentor Graphics公司独有、完善的硬件设计复用、创建和管理环境,广泛地应用在FPGA, 平台化FPGA, 结构化ASIC,ASIC和SoC等多种设计流程中。HDL Designer可以实现HDL与图形方式混合的层次化设计,结合数据管理、版本管理、文档管理、设计流程管理等全面的设计管理功能,为大规模设计提供了有力的支持。HDL Designer提供和多种仿真器、综合器的接口,用户可以根据实际情况定制自己的设计流程。与仿真工具如QuestaSim和综合工具如Precision结合提供完整的FPGA/CPLD设计流程。

主要的优点:

采用多种高级设计输入工具,快速创建设计;

快速地分析设计代码,评估代码,对RTL代码进行图形化处理;

内置与其他EDA工具和版本管理工具的接口;

与Mentor Graphics的其它工具构成完整的FPGA/ASIC设计流程。

图形化设计

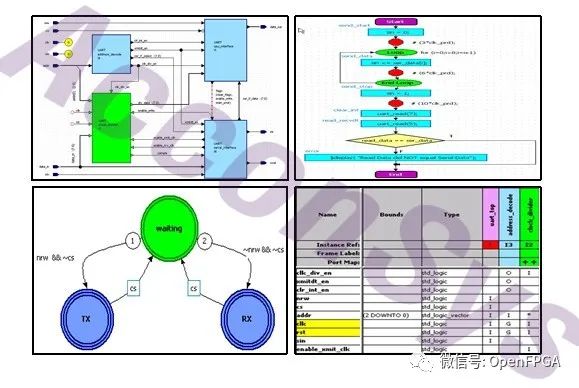

HDL Designer提供丰富强大的输入手段,为用户提供了一个设计高效的设计创建环境。针对不同厂商的器件,可以采用相同的设计方法。输入方式包括框图、流程图、状态机、真值表、基于接口设计(IBD)、表格式输入输出、HDL文本等设计输入描述方式。所有图形化设计输入都可以自动生成高效率可直接综合的HDL代码。

图形化设计输入

代码质量检查

传统的方法评估一个项目的代码质量高低基于主观的评价,而HDL Designer避免了这一缺陷。HDL Designer内置了不同的设计规则集合,同时,用户可以进行灵活的修改,来制订出适合本公司的设计规则。而且,面向航空航天及军工等安全关键行业的设计特点,HDL Designer集成了DO-254、安全关键设计规则集,确保设计具备足够的可靠性及安全性。

设计规则检查

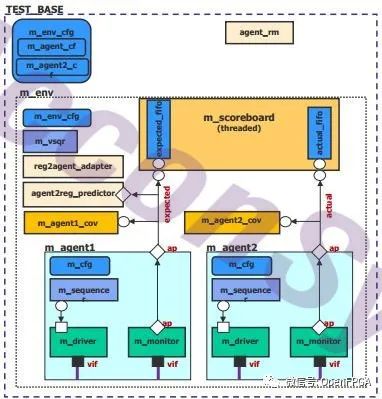

高级验证方法学平台创建

对于诸如AVM/OVM/UVM等高级验证方法学的应用,HDL Designer提供了一个强大且良好的GUI环境,基于集成的AVM/OVM/UVM与验证兼容性的规则检查,帮助工程师快速实现基于AVM/OVM/UVM标准的测试平台的调试,减少了测试平台的创建与调试时间,并满足工程师对复杂硬件设备的高性能测试环境创建的需求。

搭建UVM验证环境

在高可靠性流程中,具备有效管理设计数据的环境是一个重要理念。HDL Designer借助管理配置工具与设计流程中的其它工具,可提供RTL设计创建、编辑、代码质量检查与可重用分析,并且支持网页形式的设计检查方式。它带有内嵌的DO-254设计规则集,可以针对设计可靠性进行有效的检查,进行设计代码风格与质量的评估,对实际项目的开展极具工程实践价值与指导意义。

该工具的主要技术性能及指标要求如下:

内置众多设计规则(含DO-254),可快速地分析设计代码,评估代码;

支持对RTL代码进行图形化处理,便于工程师理解不熟悉的设计结构;

支持采用多种高级设计输入方式,快速创建设计与测试环境;

内置与其他EDA工具和版本管理工具的接口;

可对设计进行完整性分析及设计层次关系分析,便于工程师查找设计缺失与理解设计结构;

支持框图、状态机、真值表、流程图、基于接口设计(IBD)等多种设计图形化显示形式,并可自动将图形转成Verilog或VHDL源代码;

其内嵌的代码编写工具可自动联想VHDL或Verilog的关键词,减少代码编写错误,并可以进行语法检查。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...