1. Linux下的基本操作

模拟IC设计实践_课时2 P2 - 07:59

Linux之Kernel、shell、bash:

- Kernel是核心,直接控制硬件

- shell将用户的指令与Kernel沟通,shell有很多种

- Linux使用的shell是Bourne Again Shell,简称bash

- 详细参考:https://www.cnblogs.com/z-x-p/p/11571569.html

桌面右键,点开Terminal 类似于windows的cmd

快捷操作:

- 输入文件名后按TAB,会自动补充后缀

- 阔选一段文本,按鼠标中键,会将其复制到命令

常用命令:

- ls 当前目录文件夹列表

- ll -a 列出当前目录所有文件及其属性,包括隐藏文件等

- vi FilenName:vi是文本编辑工具,对该文件进行文本编辑

INSERT(键盘上的插入键,我这是FN+INSERT)进入文本修改模式

ESC 退出编辑模式

:wq! 保存并退出文本编辑工具

- 文件权限修改 chmod命令 略

- cd 跳转当前目录

cd .. 返回上一级目录

cd 文件夹名 进入当前目录的下一级

cd 路径 进入某路径

cd ~和cd /,~相当于/home/用户名,/表示根目录

- mkdir FilenName 创建名为FilenName的文件夹

- rm -R FilenName 删除名为FilenName的文件夹

- source FilenName 在当前bash环境下读取并执行FilenName中的命令

- pwd 显示当前目录路径

模拟IC设计实践_课时2 P2 - 14:11

进入cadence

//前两行打开terminal 在~目录下运行RFIC.cshrc文件,该文件是cadence的配置文件,第三行启动cadence

cd ~

source RFIC.cshrc

icfb

//显示如下界面,是cadence最底层的操作界面

模拟IC设计实践_课时2 P2 - 15:26

介绍cadence菜单

后面使用时候再留意吧

2. 初识Composer和ADE

模拟IC设计实践_课时2 P2 - 28:12

创建电路图

- Tools→Library manager

- 左侧Library选择设计库(这里选了RFIC_sin)

- File→Cell View:Tool为Composer,Composer是Cadence的电路图编辑工具

绘制原理图

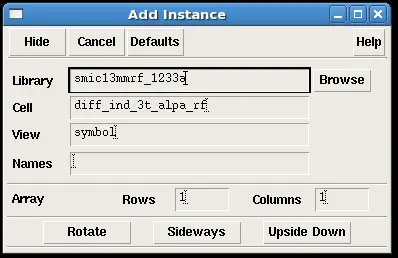

- 快捷键i,调用元器件。点Browse选择元器件,在原理图中,View只能选择symbol,选好后回车载入器件,ESC退出元器件载入

- 快捷键q,选中元器件后按Q可以显示参数值

- 快捷键f,图纸自适应缩放

- 快捷键[ ],放大和缩小

- 快捷键w,wire,左键放置节点

模拟IC设计实践_课时2 P2 - 34:46

仿真界面(ADE, Analog Design Environment)

- ADE是virtuoso对schematic的仿真工具,514版本里是analog environment,617版本里变成了ADE缩写

- 在原理图中打开,Tools→Analog environment

- Design:原理图信息;Analyses:选择仿真类型;Design Variables:选择仿真变量,如容值、信号幅度;Outputs:仿真结果

- Session→Save State存储仿真状态

//选择Directory则存储在当前目录(工作区);点击Apply进行存储,会显示在Existing States

//选择Cellview则可以在Library看到(选择Cell后显示在View列表中),在不同工程间转移设计时方便

- Session→Load State加载仿真状态

- Session→Options

//Waveform Tool波形查看的工具,WaveScan和AWD功能差不多,主要是界面差异

- Setup→Design对哪个电路进行仿真(对哪个Cell)

- Setup→Simulator/Direc...设置仿真环境

//simulator设置仿真器(aps并行计算,计算瞬态快;数模混合要用到spectreVerilog这些仿真器,默认采用spectre)

//Project Directory仿真存储位置

//Host Mode仿真模式,

- Setup→Turbo/Paras...用于加快仿真速度的选项

//复杂电路后仿真开启Turbo 后仿真是综合、布线布局后的仿真

//Parasitic Reduction去除细微的,几乎无影响的寄生参数

- Setup→Libraries模型库(? 不理解

- Setup→Temperature仿真温度设置

- Setup→environment后仿真可能会用到,仿真环境的设置

//Switch View List仿真顺序

- Outputs→To Be Saved→Select On Schematic选择需要保存数据的网络和节点,会显示在Outputs框图

- Outputs→To Be Plot同理

- Outpus→Save All保存设置,只有在这里把save设置成selected(默认 allpub),To Be Save的设置才有效

- Simulation→Options仿真设置(仿真精度、温度、收敛方法等)

- Simulation→Netlist→Creat只生成网表而不进行仿真

- SImulation→Convergence Aids收敛助手,设置节点电压,初始条件,通常在大型电路难收敛时进行设置

- Tools→Parametric Analysis设置参数扫描,类似COMSOL

- Tools→Corners工艺偏差设置

- Tools→Monte Carlo蒙特卡洛仿真,通过大量失配条件下的仿真,观察结果跟设计指标差多少,表现良率、鲁棒性

- Tools→Calculator计算器

通常直接在右侧的图标选择

- Choosing Design

- Choose Analysis选择仿真类型,通常默认设置中等精度(moderate),此处设置后会显示在Analyses框图内

- Edit Variables

- Setup Output设置输出,可以编辑公式,设置后显示在Outputs框图内

- Delete 删除框图内的内容

- Netlist and Run建立网表并运行

- Run用之前的网表运行

- Plot Output画图

3. 原理图设计和仿真(CMOS反相器)

模拟IC设计实践_课时3 P3 - 02:28

CMOS RF工艺库基本特性

- 工艺库SPICE模型说明文档目录:/home/EDA/kit/PDK13mmrf_1P6M_30k/docs

TD-MM13-SP-2001v8P.pdf:.13um工艺,混合信号,1V2/3V3 SPICE模型

- 主要看第七章,MOS、BJT、电阻电容等器件的模型参数

模拟IC设计实践_课时3 P3 - 08:05

删除已有Cell:右键长按选则delete,复杂的确认机制避免误删

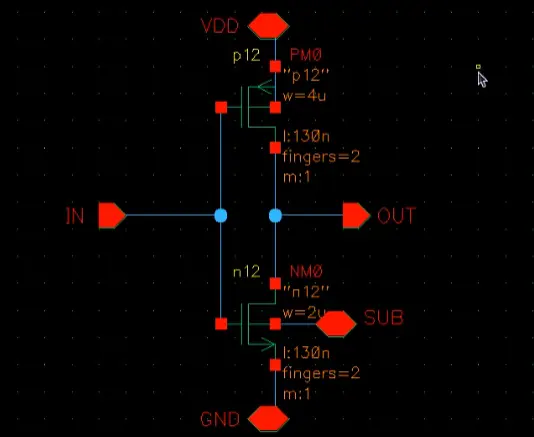

绘制CMOS反相器原理图

- 建立名为INV的原理图

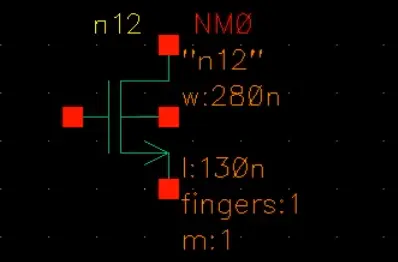

- 放置NMOS:在smic13mmrf_1233(.13um工艺库)中找到mosfets→n12(1V2的NMOS)→symbol(原理图只能选这个)

//快捷键i

//红字NM0是器件唯一的标识符

- 查看和修改晶体管参数:Length设置.13um,Finger数设置2,PMOS Finger Width设置2um,NMOS设置1um(迁移率比值通常设置2,以达到相同的导通电阻)

//快捷键q

//Multiplier设置并联个数,同一个器件可以设置为多个并联

//Length沟道长度

//Total Width晶体管整体宽度=Finger Width(栅宽)*Fingers(栅极数量)

//Gate Connection栅极连接方式,和版图相关的设置

//Switch S/D交换源漏极

//主要的修改就是沟道宽长

- 检查和保存:点击左侧图标Check and Save

//快捷键x

//有悬空电极,报warning

- 连线:Gate相连、Pdrain连Nsource,把Psource和nDrain引出来,Pbulk连到电源(Psource),Nbulk连sub(模拟电路)或Ndrain(数字电路),这里作模拟电路处理,先引出来

//快捷键w

//双击结束连线

- 添加端口:左侧图标pin,设置输入端IN,Direction为in;输出端OUT,Direction为out;添加电源VDD,地GND、衬底SUB,Direction设置inout

//快捷键F3:调出添加pin窗口

//把pin放在连线上,拉动pin会自动补充连线

//批量设置端口,多个Pin Name用空格隔开,点Hide后按顺序放置即可

//端口用大写:有的工艺在DRC等检查时默认不区分大小写,但有的工艺库会把所有小写认成大写,都用大写避免混淆

//快捷键shift+m:移动位置(和直接拖动相比,不改变连线)

//快捷键right click:旋转

- 再次保存,这时无warning

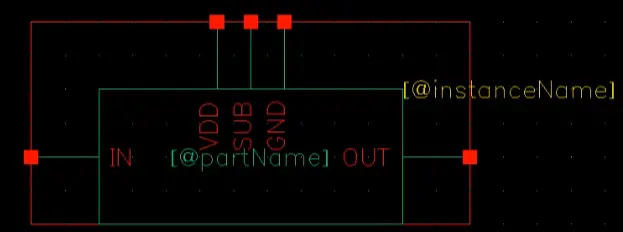

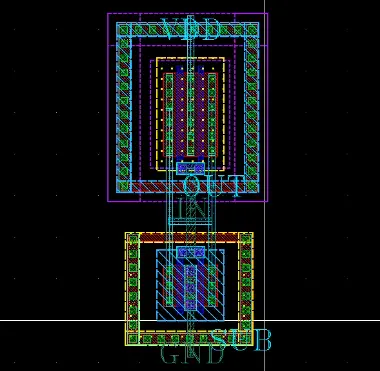

- 建立仿真用的symbol:Design→Create Cellview→From Cellview→弹出创建CellView的对话框→OK→弹出Symbol Generation Options窗口,可以设置Pins的布局等→OK,生成symbol如下图

- 保存symbol:左侧选项栏save

- 关闭原理图和symbol,观察Library Manager中INV这个Cell的内容,有schematic和symbol两个view

模拟IC设计实践_课时3 P3 - 26:48

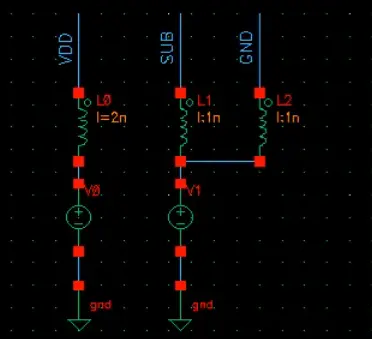

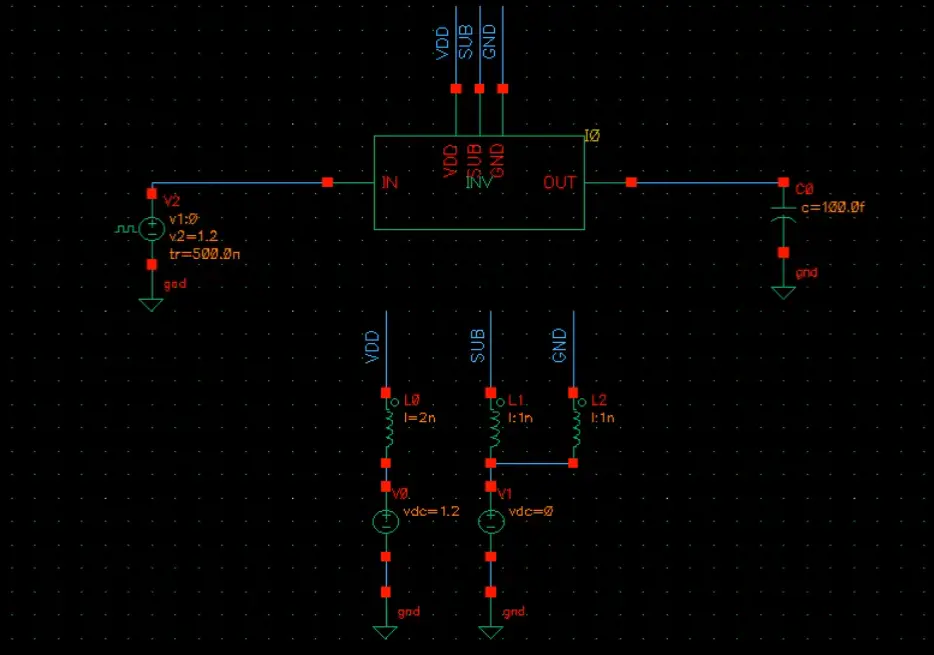

建立仿真用的testbench(测试平台)

- FIle→New→CellView→Name改成INV_testbentch

- 调入之前画好的symbol

- 添加仿真用的电压源和gnd:analogLib→Everything→vdc(gnd)→symbol

//Cell为gnd,注意GND≠gnd,gnd是绝对地电平,GND是芯片引脚,是相对地,GND和gnd之间也要放一个可控电压源

//直接在原来的Add Instance窗口把Cell改成gnd就可以放置了

- 复制操作:框选器件→按c

- 添加电源封装引线的电感:Cell为ind,连接在电源上,电感大小2nH,阻抗设置100mΩ

//常规QFN、QFP封装,1um引线电感为1nH左右,长度通常有2um

- 添加gnd封装引线的电感:连接在地线,电感大小1nH,阻抗50mΩ

//gnd通常bounding到芯片背面的大片金属地上,引线电感会小,引线长度在1mm以内(?)

- 添加引线,用网络命名来设置节点对应关系(让原理图更简洁):把线引出来→左侧选项Wire Name,给wire添加label→对话框中Name设置为VDD→选中VDD引出的线,完成命名→复制该引线,放置到其他节点上,这些连接到具有相同名称的wire的节点之间是互连的

//快捷键l:添加引线label(wire name)

- 对SUB的处理:也是连接到地,但和GND是并联的接地关系

- 设置VDD=1.2V,GND=gnd(设置地电源为0)

- 设置脉冲波形输入:analogLib→Everything→vpulse,设置DC=0V,V1=0V,V2=1.2V,Delay time=100ns,Rise time=Fall time=0.5us,Pulse Width不设置则默认为0.5*Period,Period=1/F(F是频率变量)

- 设置输出负载电容,cell为cap,容值设置0.1pF

模拟IC设计实践_课时3 P3 - 42:40

进行仿真操作

- 打开ADE,Tools→Analog Envir

- 调用变量,添加刚刚设置的变量频率F:右侧图标Edit Variables→Copy From(从原理图调入)→在Table中选中F→Value设置为100k

- 添加直流仿真类型:右侧图标Choosing Analysis,dc(直流仿真),Save DC Operating Point保存直流工作点

- Netlisit and Run建立网表和仿真

模拟IC设计实践_课时3 P3 - 46:24

//Result→Annotate→DC Node Voltage,所有节点的电压都会显示在原理图上

//Result→Annotate→DC Operating Points直流工作点,所有电流都会显示在原理图上

模拟IC设计实践_课时3 P3 - 49:31

- 查看symbol内部电路仿真结果:选中symbol,按快捷键e(进入下一层),选择schematic(原理图子电路)

//快捷键e:进入下一层原理图

- mosfet粗略工作状态:查看DC Operating Points时,会在原理图显示vgs、vds、跨导gm、过饱和电压vdsat(vgs-vth)

- 器件详细工作状态:Results→Print→DC Operating Points→鼠标选中器件→弹出结果Results Display Window

//region:0 cut-off;1 triode(线性区);2 saturation;3 subthreshold;4 breakdown

//ron:沟道电阻

- 返回上一层原理图:Composer中Design→Hierarchy→Return

//快捷键CTRL+e:返回上一层原理图

模拟IC设计实践_课时3 P3 - 57:20

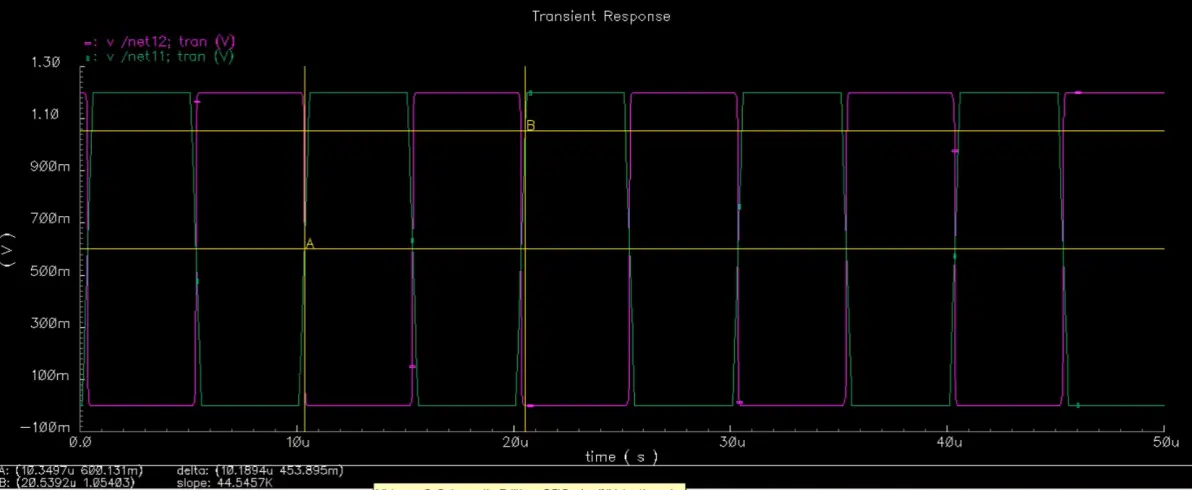

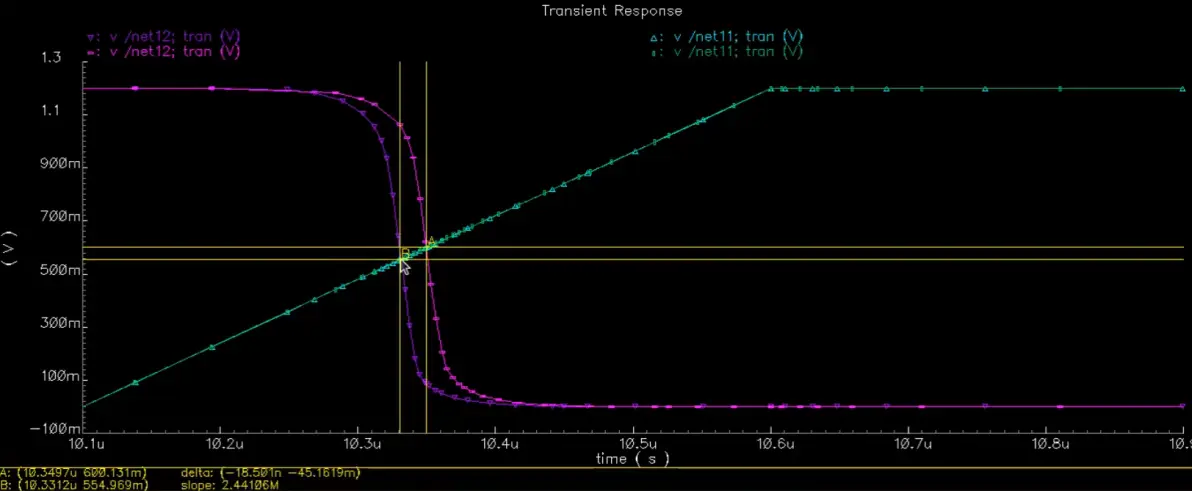

- 添加瞬态仿真类型:ADE的Choosing Analysis,选择tran,Stop Time选择50us,精度选中等

//之前设置周期为10us,因此可以查看五个周期的瞬态

- 直接Run,不用重新生成网表,产生的仿真信息框内包含直流仿真和瞬态仿真

- 用波形查看器查看瞬态仿真结果:Result→Direct Plot→Main Form,先查看电压→在原理图上click要查看的网表

//在ADE的Session→Options选择波形查看器为WaveScan或AWD,AWD可视化更好,可以按a和b添加游标,右键选中区域可以放大,shift+f复原

//快捷键a,b:在AWD波形查看器放置游标a和游标b

//快捷键shift+f:在AWD波形查看器复原视图

模拟IC设计实践_课时3 P3 - 01:06:21

NMOS和PMOS宽长比不同设置下的工作状态

- 进入symbol内部电路,此时电路是只读,Composer中Design→Make Editable恢复可编辑模式

- NMOS和PMOS宽长比比值=1:1(把PMOS Finger Width由2um改成1um),保存后在ADE中Netlisit and Run,

- 再次添加输出网表为观察对象,对比修改前后的输出波形的变化

//翻转电压变低了,要翻转电压在中间,通常要设置PMOS的NMOS宽长比比值为2:1

模拟IC设计实践_课时4 P4 - 00:20

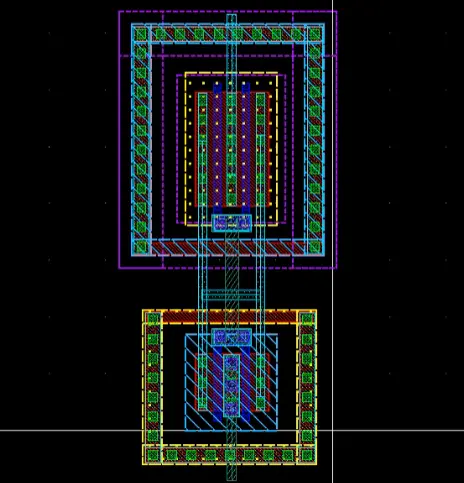

4. 版图设计

virtuoso版图界面

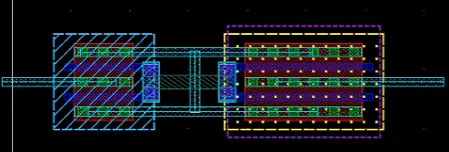

- 从原理图导出版图:Tools→Design Synthese→Layout XL,View Name是类型Layout,Tool用Virtuoso

//Virtuoso是cadence的版图设计工具

//drw是可以画的层

//AA层:有源层

//NW层:N阱

//DNW层:栅阱工艺,在Psub上制作一个深N阱,衬底隔离

//GT层:栅

//SN层:N型注入

//SP层:P型注入

//M1~M8层:金属层1~8,工艺安装时选择的是1层p-Si,6层金属互联层(1p6f),因此只用得到M1~M6,M6采用的是30ke-10的厚金属(RF领域需要)

//V1~V7层:过孔层,V1是M1~M2的过孔

//标识层(?):PSUB等

//text层

//TM层:顶层厚金属

模拟IC设计实践_课时4 P4 - 09:47

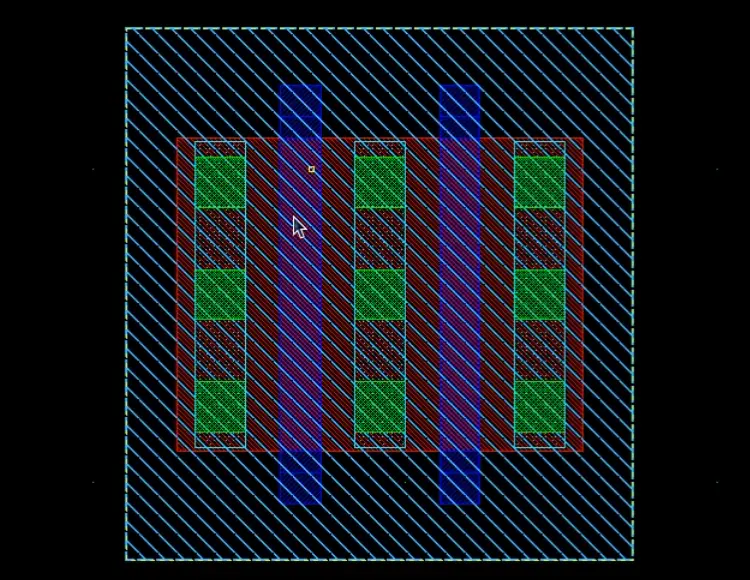

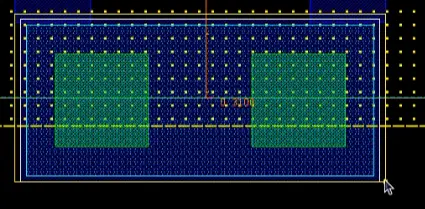

绘制版图

- 将用到的元器件从原理图导入到版图:在原理图选中器件,在版图Create→Pick From Sche,弹出对话框采用默认设置,在版图上点击可以放置器件版图

//按住shift可以选中多个器件

//快捷键shift+f:显示版图所有层次

//快捷键ctrl+f:只显示版图label外框

模拟IC设计实践_课时4 P4 - 12:27

- 版图层次打散:选中器件→Edit→Hierarchy→flatten,选中flatten Pcell→选中某一层,按Q查看

//Pcell是参数化单元,不用每次都重新画,参考:https://www.sohu.com/a/430596399_120873246

//蓝绿色:SN层,N型注入

//红色:AA层,有源层

//深蓝色:GT层,p-Si制作的两个栅极

//黑色:M1,金属1层

//绿色:CT,过孔层,连接AA和M1,GT和M1之间也用CT

//紫色:NW N阱

//黄色:SP P型注入

//其余和NMOS相同

- 网格精度设置:virtuoso的Options→Display,Snap Spacing改成0.005,单位是um

- 重新导入NMOS和PMOS版图,之前打散了不方便

- 移动晶体管:选中晶体管后按m

//快捷键m:版图中移动器件

- 版图中显示连线关系:virtuoso的Options→DIsplay,Display Controls中选中Nets

模拟IC设计实践_课时4 P4 - 19:58

- 源漏极金属连线:在LSW选择层M1→按p→点击CMOS的Drain(设置起始端),选择M1层→引线下拉到NMOS的Drain→回车,完成连线;选中引线按q修改宽度等设置,按m移动引线进行对齐;需要将PMOS和NMOS的Drain连到一起,Source分别引出(到GND和VDD)

//快捷键p:版图连线

//快捷键p→F3:按设置的尺寸进行连线

- 栅极金属连线:放置过孔将两个栅极一起连到M1,Create→Contact,M1_GT,1×2;再通过M2把NMOS和PMOS的Gate连到一起

//过孔和Source保持一定距离,按k调出尺子,预留0.3um的距离

//快捷键k:尺子

//快捷键shift+k:清除尺子

//过孔和栅对不齐,画一个矩形对齐它,在LSW选择GT层,按r画矩形

//快捷键r:画矩形

//快捷键shift+z:逐步缩小视图

//快捷键c:拷贝

//M2可以用金属线,也可以用矩形,要添加M1和M2之间的过孔

- 只显示某一层:在LSW选中层→上方NV按钮→选中virtuoso窗图按f;按AV按钮重新显示所有层

模拟IC设计实践_课时4 P4 - 35:19

- 绘制衬底接触环:防止闩锁效应;NMOS绘制M1-SUB的过孔,PMOS绘制M1-NW的过孔,围成一个环,其中内测边用AA层(有源层)连接,有源层要用掺杂层包围,否则DRC报错,注意PMOS中N阱要比保护环大

//同时修改两个图案的参数:选中一个后按shift选中另一个,按q,选中选项框右上角的Common

模拟IC设计实践_课时4 P4 - 42:06

- 图案拉伸:Select左边显示(F)标识器件完整选择,按下F4,会变成字母P,器件可以部分选中;框选要拉伸、移动的部分(只选中一端则拉伸,全选中则移动)→按s→点击刚刚框选的器件,可以移动

- NMOS的保护环和Source短路了,把Source连接的金属层改为M2

模拟IC设计实践_课时4 P4 - 48:27

- 添加PIN:Create→Label,名字为IN、OUT...,放置Label后将其所在层改为对应层,如IN在M2层,OUT在M1层,把Label图标最中间的十字标对准PIN要放置的位置,以此确定对应关系

模拟IC设计实践_课时5 P5 - 00:03