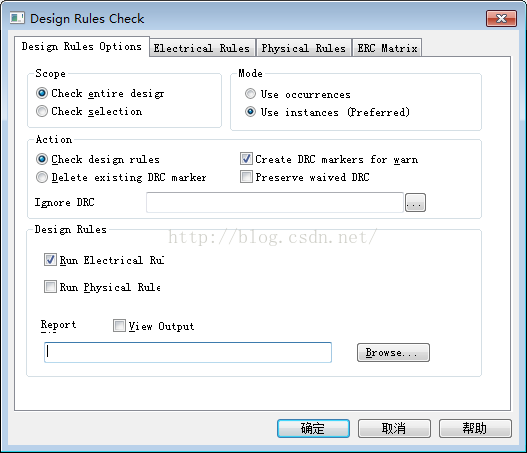

DRC 检查的菜单步骤:

1、打开 ORCAD 软件,先选中整个 dsn 文件;

2、在Tools中点击Design Rules Check;

Scope:范围,是检查整个设计,还是只检查选中的部分;

Mode:模式,是用事件(OCC)还是实例(INS),默认是实例(不明白啥意思),默认好了;

Action:操作,第一个是要不要检查整个设计;

第二个是在警告出做DRC标记;

第三个是删除存在的DRC标记;

第四个保留放弃的DRC

Design Rules:设计规则,第一个是运行电气规则;第二个是运行物理规则。

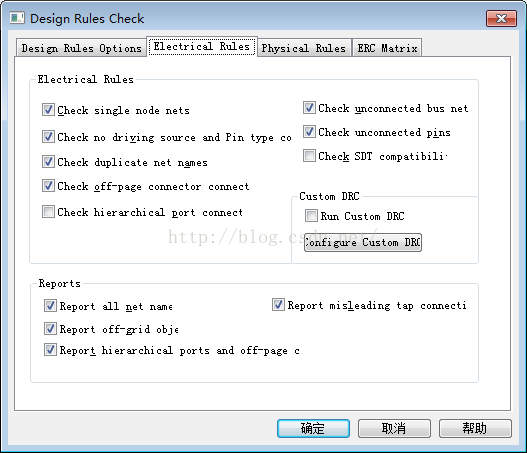

2.电气规则(Electrical Rules),关键部分已经加粗

check single node nets——检查单节点网络;

check unconnected bus net——检查未连接的总线网络;

check no driving source and Pin type connect——检查驱动接收等Pin Type的特性,这些在高速仿真时用到;

check unconnected pins——检查未连接的管脚;

check duplicate net names——检查重复的网络名称;

check SDT compatibility——检查SDT兼容性;

check off-page connector connect——检查跨页连接的正确性;

check hierarchical port connect——检查层次图的连接性;

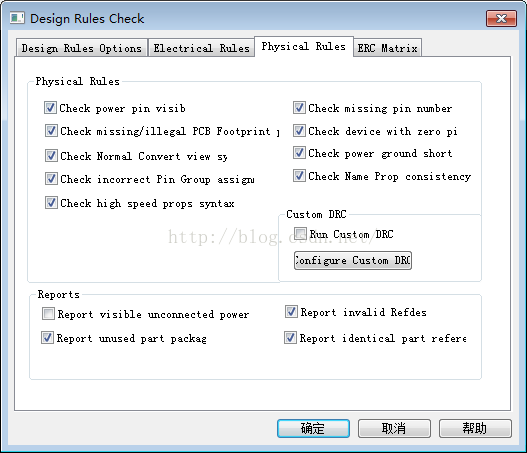

3.物理规则(Physical Rules)

check power pin visible——检查电源 引脚 可视性;

check missing pin number——检查是否有丢失的Pin numbers;

check missing/illegal PCB footprint property——检查缺失或者不符合规则的PCB 封装库 定义。没有此项规则导入原理图导入PCB时可能会出项许多问题。

Check Normal Convert view sync ——检查不同视图下的Pin numbers的一致性。

Check power ground short——检查电源、地短接。

Check incorrect Pin_Group assignment——检查Pin_Group属性的正确性;

Check Name Prop consisrency——检查名称属性的一致性;(猜的,Prop=Property)

Check high speed props syntax——检查高速props语法有无错误;

Custom DRC——自定义的DRC;

Reports:

Report visible unconnected power pin——导出可见的未连接电源引脚;

Report invalid Refdes——导出无效的参考编号;

Report unused part package ——导出未使用的部分封装;

Report indentical part reference——导出相同元件的编号;

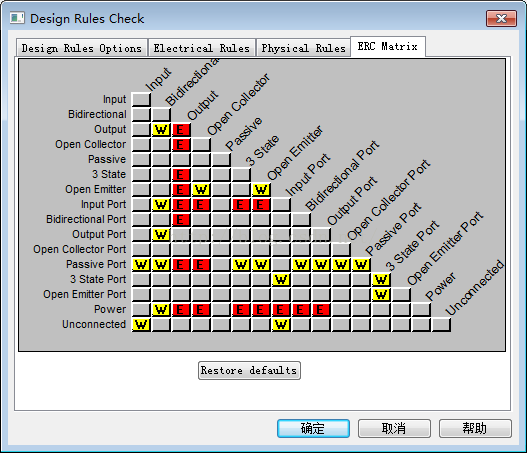

4.ERC Matrix

ERC:Electrical Rule Checker,电气规则检查 矩阵 。

不同属性的管脚相连是不报错,报警告还是报错误的矩阵设置,在进行电气仿真时可能会用到。

Input:输入引脚;

Bidirectional:双向引脚;

Ouput:输出引脚;

Open Collector:集电极开路引脚;

Passive:无源引脚;

3 State:三态引脚;

Open Emitter:射极开路引脚;

Input Port:输入端口;

Bidirectional Port:双向端口;

Ouput Port:输出端口;

Open Collector Port:集电极开路端口;

Passive Port:无源端口;

3 State Port:三态端口;

Open Emitter Port:射极开路端口;

Power:电源引脚;

Unconnected:未连接;

DRC筛查log日志中,可通过筛如下关键字逐一确认:

1.QUESTION;

2.Single node Nets;

3.ERROR;

4.Distiller

3.原理图ORCAD生成元器件封装库

在现成的原理图上生成元器件封装库:

4.原理图层次化设计

Hierarchical block设计:

OrCAD Capture创建层电路Hierarchical Block仿真_YuMonster的博客-CSDN博客

下载安装地址: