印刷电路板(PCB板) 是电子设备最基本的组成部分,它提供电子元器件之间的电气连接,是电子产品中电子元器件的载体,PCB板的性能直接关系到电子设备质量、性能的好坏。当前电子设备越来越趋向于多功能,小型化,这就使得PCB板上的集成度和布线密度越来越高。电磁干扰会干扰信号并降低信号完整性,如何在高集成度的PCB板上抑制电磁干扰就成为了一个关键问题。除了电子元器件的选择和电路设计之外,良好的PCB板设计也是一个非常重要的因素。

PCB上的电磁干扰主要分为两种。一种来自PCB内部,它主要是因为受邻近电路之间的寄生耦合及内部组件的场耦合影响,信号沿着传输路径有串扰,例如电容器,尤其是高频电容。我们可以把它看作一个LCR电路,因为电容在实际工作时,一般都会产生等效电感和阻抗,电容都有自谐振频率,在自谐振频率下,电容器呈现容性。在高于自谐振频率时,电容呈现感性,阻抗随着频率的增高而增大。

另一种电磁干扰来自PCB的外部,分为辐射干扰和敏感元器件两种问题。辐射主要来于时钟和其他周期信号的谐波源,还有一些电子设备或者仪器中由于有电压和电源的跳变,产生二次谐波。

本文整理了一些PCB设计中常用的能够有效减少电磁干扰的方法,帮助工程师更好进行PCB设计。

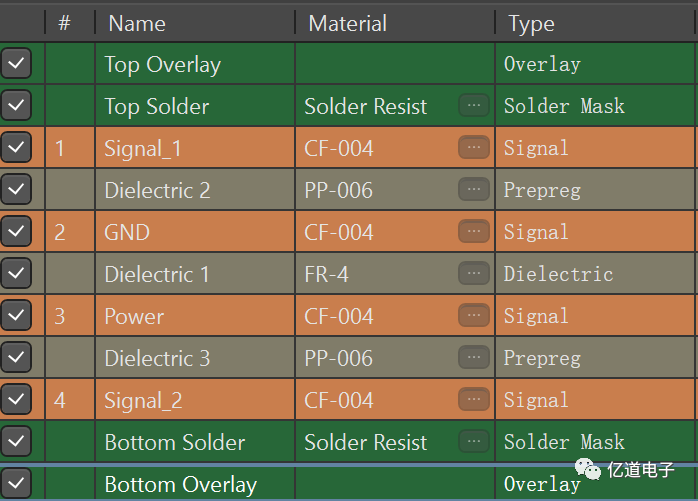

当PCB板使用同种材料时,增加叠层可以有效的降低电磁干扰。但是层数越多,制造工艺就越复杂,成本也越高。合理的选择PCB叠层数就变得非常重要。层数越多,信号层、电源层、接地层的排列组合种类也就越多,总的来说,叠层设计可以遵循以下原则:

1)由于电子元器件都布置在Top层和Bottom层,信号层可以以这两层为主。

2)信号层与一个内电层(电源层或者接地层)相邻,利用内电层的大面积铜皮提供信号屏蔽。

3)高速信号布线放在信号中间层,并且夹在两个内电层之间,利用内电层的铜皮为高速信号传输提供电磁屏蔽。

4层板常用叠层方案

6层板常用叠层方案

上图两个方案仅供参考,在实际设计过程中,某一个方案并不能满足所有要求,这时候就需要根据设计的侧重点来进行考量,在满足叠层设计基本原则的前提下进行调整。

由于电子设备中不同电路(高频、低频电路/数字电路、模拟电路以及电源电路)的元器件布局和布线规则各不相同,它们产生干扰以及抑制干扰的方法也不同。所以在元器件布局时,应该将不同的电路分别放置,尽可能的降低不同电路之间的干扰。

同一电路的元器件尽可能的放在一起,这样可以防止电路之间的干扰,也可以缩短元器件连接的导线长度以获得更好的抗噪效果。同时,要把模拟电路,高速数字电路,电源合理地分开,使相互间的信号干扰降到最小。

时钟发生器(Clock)、晶振和CPU的时钟输入端(Clock Input)很容易产生噪声,要相互靠近,以免对其他电路产生影响。容易产生噪声的元器件、电源电路等应尽量远离逻辑电路。

对于刚接触PCB设计的工程师来说,在做PCB布局时可以参考以下几点:

1)低电平信号电路不要靠近高电平信号电路和电源电路。

2)将模拟电路和数字电路分开,避免模拟电路、数字电路和电源公共回路产生阻抗耦合。

3)电磁干扰滤波器尽量靠近电磁干扰源,并且和这些器件放在同一层。

4)开关元件和整流器靠近变压器。

5)容易产生噪声的放在一起,同时远离敏感电路。

6)大功率元器件不能集中放置,影响散热。

7)先确定特殊元器件(如大规模IC、大功率管 、信号源等)的位置,然后再安排其他元器件,尽量避免可能产生干扰的因素。

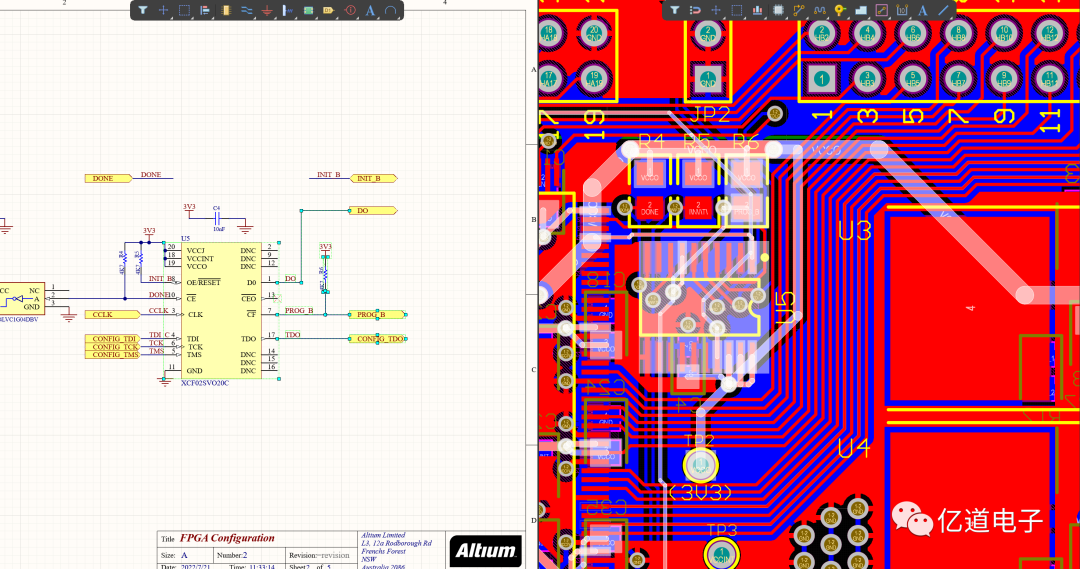

合理的布线是一块PCB板性能好坏的关键因素。PCB布线一般会按照电路功能来进行,布线同时参考电路原理图,可以更好的帮助布线工作的进行。

Altium Designer交互式布线,在原理图中选中的元器件和导线,在PCB上同时会高亮显示。

布线可以遵循以下规则以减少干扰:

1)相邻两层的布线应尽量相互垂直或用斜线、曲线,不能用平行线,以减少层间耦合和干扰。

2)布线尽量布短线,特别是对小信号电路,布线越短,干扰越小。

3)布线改变方向时,避免锐角,直角。

4)相同电路的导线宽度尽量保持一致,有利于阻抗匹配。

5)电路的输入及输出的导线应尽量避免相邻平行,在这些导线之间可以加接地线。

6)高频线布在远离高噪声电源线的地方以减少相互之间的耦合。

7)电源线和地线加宽以减少阻抗。

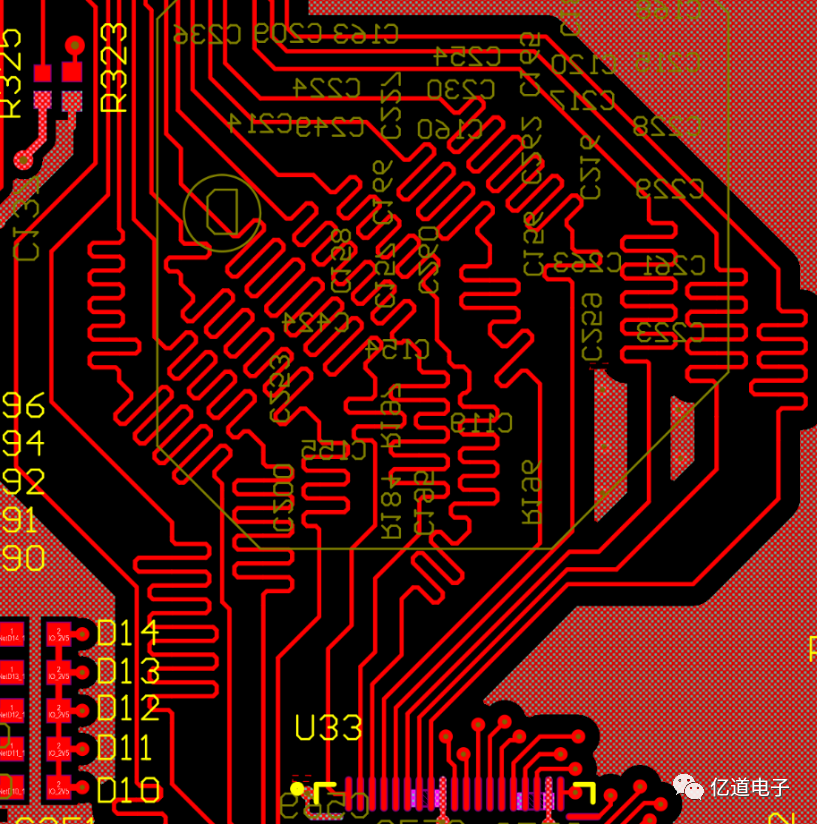

8)地址线和数据线布线长度尽量保持等长,对短线需要使用等长线功能进行拉伸。

Altium Designer 等长线

9)大电流信号与小信号之间应该注意隔离,如果有高压信号,可以在PCB板上的高低压之间开槽,避免爬电现象产生。

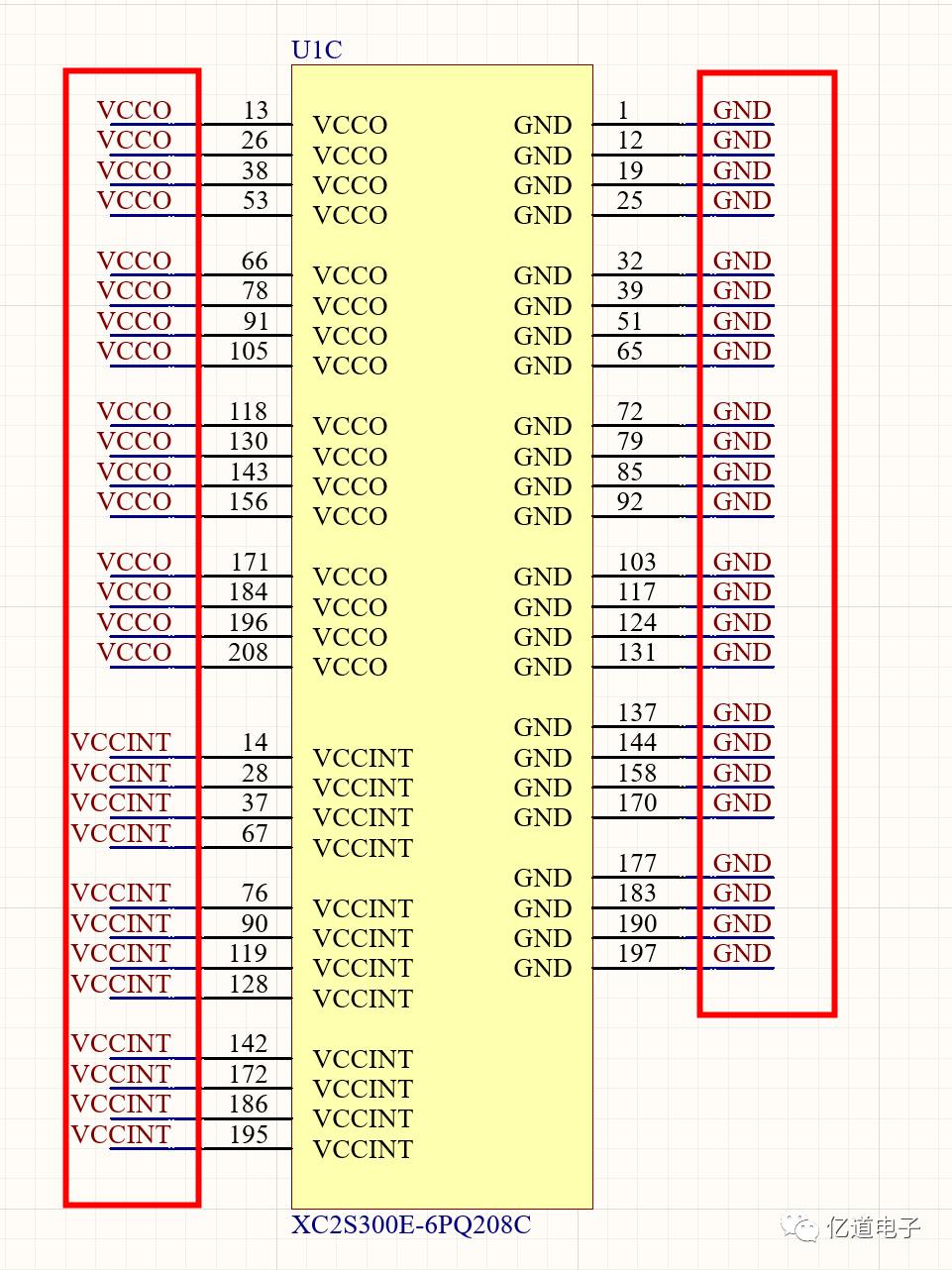

10)元器件的电源和接地PIN都要接上,不要悬空

11)增加去耦电容

12)用钽电容或聚酯电容而不用电解电容作为PCB板上的充放电储能电容。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...