Verilog行为级描述用关键词initial或always,但initial是面向仿真,不能用于逻辑综合。always是无限循环语句,其用法为:

always@(事件控制表达式(或敏感事件表)) begin 块内局部变量的定义; 过程赋值语句;end1.2.3.4.5.在always语句内部的过程赋值语句有两种类型:

赋值运算符(=) :阻塞型过程赋值算符

赋值运算符(<=) :非阻塞型过程赋值算符

阻塞型用“=”表示,多条语句顺序执行。

begin B = A; C = B+1; end1.2.3.4.非阻塞型用“<=”表示,语句块内部的语句并行执行。

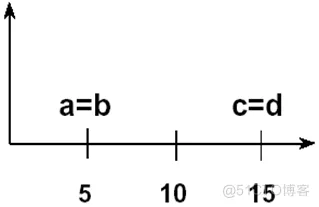

begin B <= A; C <= B+1; end1.2.3.4.//Blocking (=) initial begin #5 a = b; #10 c = d; end1.2.3.4.5.6.

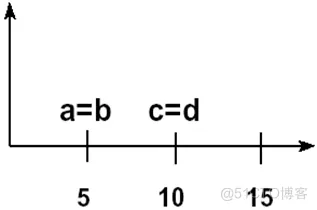

//Nonblocking (<=)initial begin #5 a <= b; #10 c <= d; end1.2.3.4.5.6.

注意:

用always语句描述硬件电路的逻辑功能时,在always语句中@符号之后紧跟着“事件控制表达式”。

逻辑电路中的敏感事件通常有两种类型:电平敏感事件和边沿触发事件。

在组合逻辑电路和锁存器中,输入信号电平的变化通常会导致输出信号变化,在Verilog HDL中,将这种输入信号的电平变化称为电平敏感事件。

在同步时序逻辑电路中,触发器状态的变化仅仅发生在时钟脉冲的上升沿或下降沿,Verilog HDL中用关键词posedge(上升沿)和 negedge(下降沿)进行说明,这就是边沿触发事件。

敏感事件分为电平敏感事件和边沿触发事件

always@(sel or a or b) always@(sel,a,b)1.2.sel、a、b中任意一个电平发生变化,后面的过程赋值语句将执行一次。

always@(posedge CP or negedge CR)1.CP的上升沿或CR的下降沿来到,后面的过程语句就会执行。

在always后面的边沿触发事件中,有一个事件必须是时钟事件,还可以有多个异步触发事件,多个触发事件之间用关键词 or 进行连接,例如,语句

always @ (posedge CP or negedge Rd_ or negedge Sd_)1.在Verilog 2001标准中,可以使用逗号来代替or。例如,

always @ (posedge CP, negedge Rd_, negedge Sd_)1.posedge CP 是时钟事件, negedge Rd_和negedge Sd_是异步触发事件。如果没有时钟事件,只有异步事件,就会出现语法错误。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...