m 序列又叫做伪随机序列、伪噪声(pseudo noise,PN)码或伪随机码,是一种可以预先确定并可以重复地产生和复制、又具有随机统计特性的二进制码序列。

伪随机序列一般用二进制表示,每个码元(即构成m序列的元素)只有“0”或“1”两种取值,分别与数字电路中的低电平或高电平相对应。

m 序列是对最长线性反馈移位寄存器序列的简称,它是一种由带线性反馈的移位寄存器所产生的序列,并且具有最长周期。

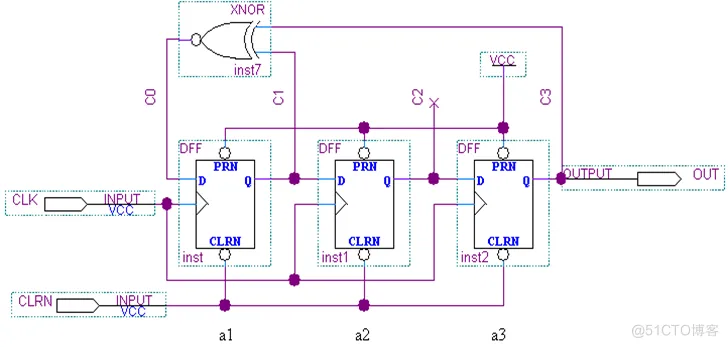

图所示是一种3位m序列产生器,它将1,3两级触发器的输出通过同或门反馈到第一级的输入端。

其工作原理是:在清零后,3个触发器的输出均为0,于是同或门的输出为1,在时钟触发下,每次移位后各级寄存器状态都会发生变化。

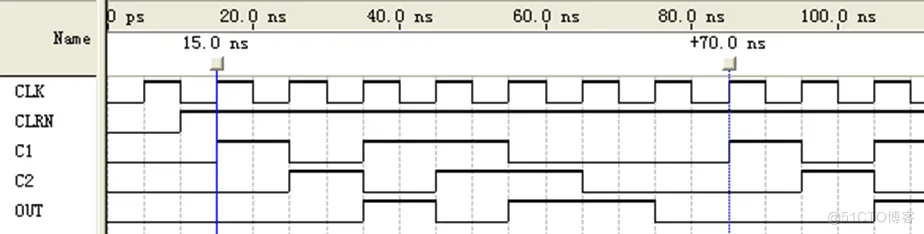

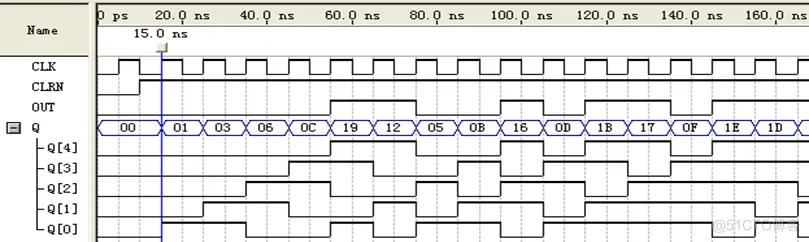

分析该电路得到如图所示的仿真波形图,其中任何一级触发器(通常为末级)的输出都是一个周期序列(或者称为m序列),但各个输出端的m序列的初始相位不同。m序列的周期不仅与移位寄存器的级数有关,而且与线性反馈逻辑和初始状态有关。

此外,在相同级数的情况下,采用不同的线性反馈逻辑所得到的周期长度是不同的。

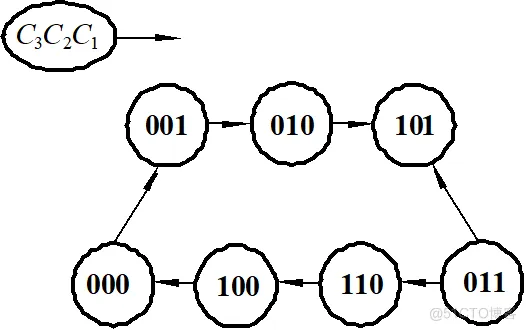

该电路的状态转换图如图所示。

共有个状态

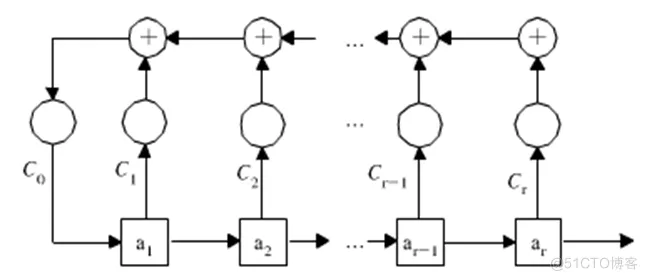

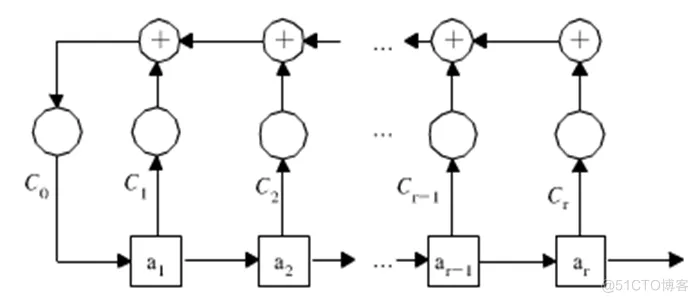

通常,将类似于图所示结构的m序列产生器称为简单型码序列发生器(Simple Shift Register Generator,SSRG),它的一般结构如下图所示。

图中,各个触发器ai(i=1,2,…r)构成移位寄存器,代表异或运算,C0、C1、C2、……、Cr是反馈系数,也是特征多项式的系数。系数取值为1表示反馈支路连通,0表示反馈支路断开。

对于SSRG结构的m序列发生器,其特征多项式的一般表达式为

特征多项式系数决定了一个m序列的特征多项式,同时也就决定了一个m序列。

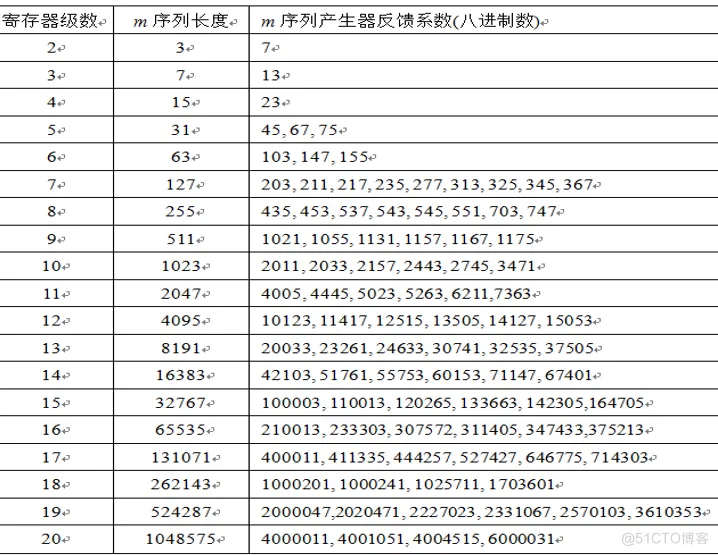

下表给出了部分m序列的反馈系数,系数的值是用八进制数表示的。

根据多项式的系数可以产生m序列。

例如,想要产生一个码长为31的m序列,寄存器的级数r = 5,从表中查到反馈系数有三个,分别为45、67、75,可以从中选择反馈系数45来构成m序列产生器,因为使用45时,反馈线最少,构成的电路最简单。

45为八进制数,写成二进制数为100101,这就是特征多项式的系数,即 C5 C4 C3 C2 C1 C0=100101

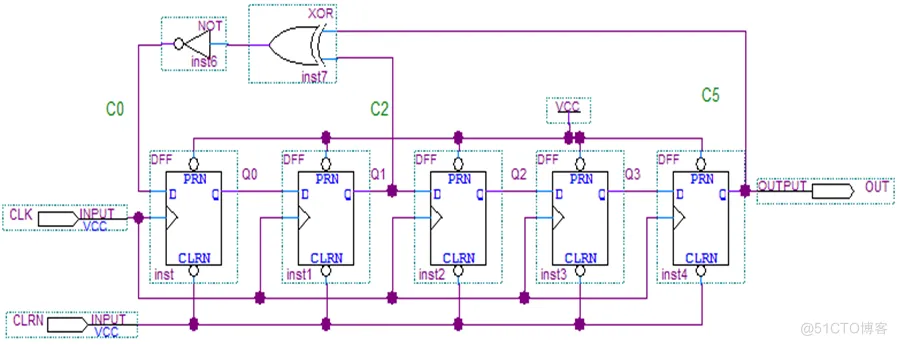

表明C5、C2、C0三条反馈支路是连通的,另外三条反馈支路C4、C3、C1是断开的,其电路如图所示。

Verilog HDL程序如下:

module m5(CLK, CLRN, OUT); input CLK, CLRN; //输入端口 output OUT; //输出端口 reg[4:0] Q; //中间节点 wire C0;assign C0 = ~(Q[4] ^ Q[1]); //反馈assign OUT = Q[4]; //输出信号always@(posedge CLK or negedge CLRN)begin if(!CLRN ) Q[4:0] <= 5'b00000; //异步清零 else Q[4:0] <= {Q[3:0],C0}; //移位endendmodule1.2.3.4.5.6.7.8.9.10.11.12.13.14.15.仿真波形(m序列长度为31):

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...