赛题:三维集成电路的多层模块划分最优化算法

背景

三维集成电路与模块划分

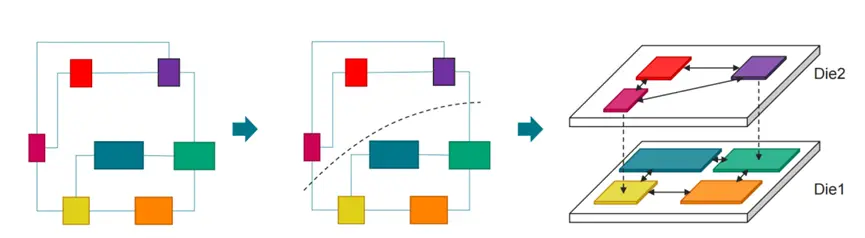

用三维集成电路来实现一个芯片,会遇到的一个常见问题是:如何对整个芯片的电路模块进行划分,使这些模块被分配到多个裸片(Die)上。

下图是一个把电路划分成两部分,并分配到上下两个同样面积的裸片上的例子。划分之后,两部分电路之间的连接,通过裸片之间的堆叠工艺实现,比如常见的有Bump以及TSV(ThroughSiliconVia)。

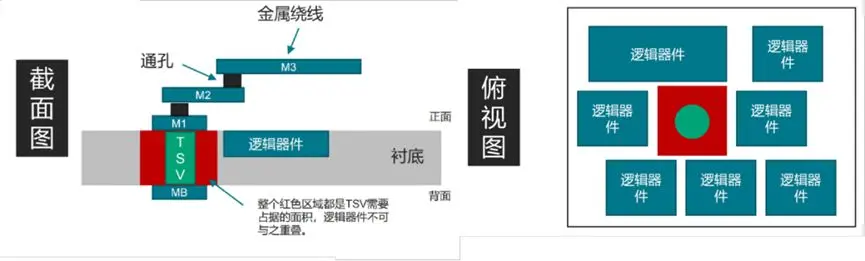

关于TSV

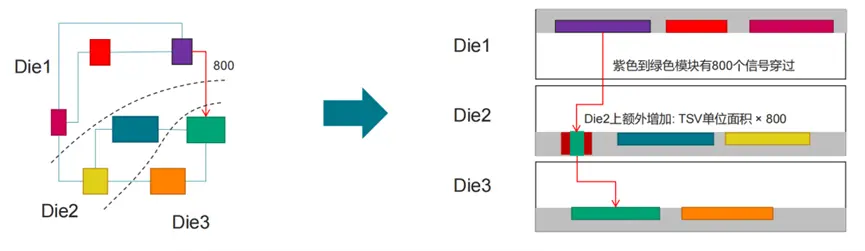

TSV提供了信号穿越裸片衬底的通路。但是它自身也需要占据一部分面积,因此也必须考虑到TSV带来的额外的面积需求。

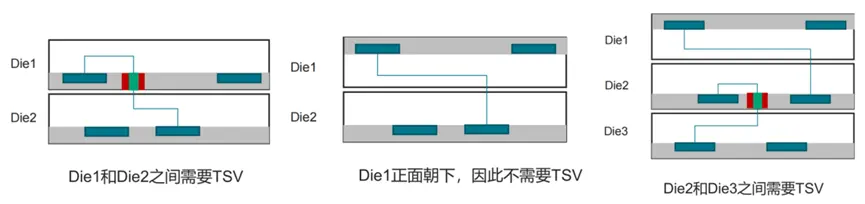

当多层裸片堆叠时,凡裸片和裸片界面处穿过衬底的地方需要TSV。

关于Feedthrough

当多层裸片堆叠时,比方说3层:从第一层到第三层的信号连接,即使在逻辑上并没有和第二层的模块有任何关系,物理上也必须穿过第二层,即Feedthrough。从而有可能会产生额外的TSV。

约束条件

三维划分需要考虑的硬性约束条件有:

1.一个裸片上所有模块的总面积,加上这个裸片上所需的TSV的总面积,不能超过裸片的面积,即面积利用率不能超过100%。

2.相邻两个裸片的界面上,可容纳的Bump/TSV的数量是有上限的。

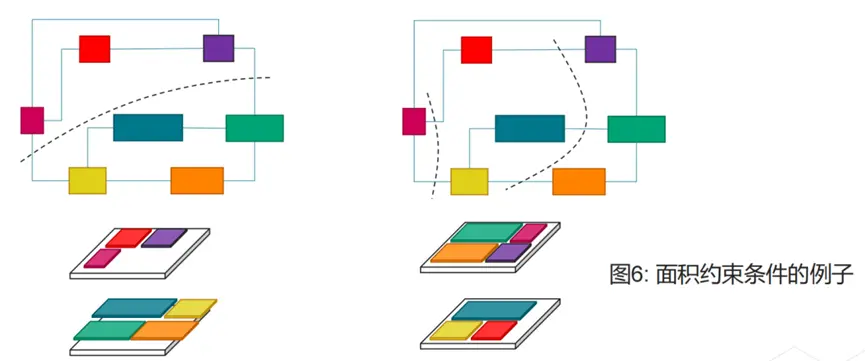

约束条件的例子

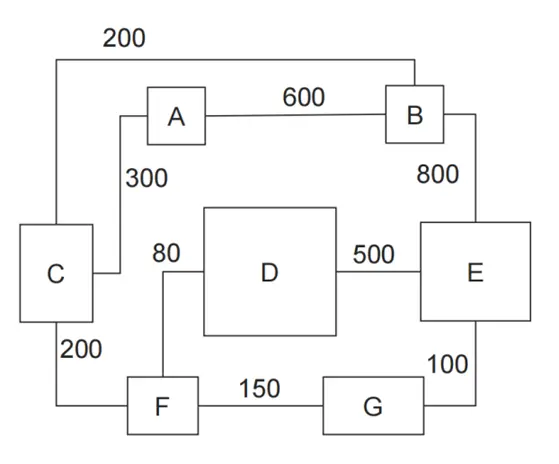

下图是面积约束条件的一个例子(假设每根线代表100个信号):

如果不考虑面积,左边的划分是最好的,因为只需要200个bump。但是第一层的模块总面积已经超过了裸片面积。

此时采用右边的方案,bump数量增加到了500个,但只要仍然小于两个die之间所能容纳bump数量的上限,同时模块总面积也并没有超过裸片面积,则仍然是可行的。

题目要求

对于主办方给定的:

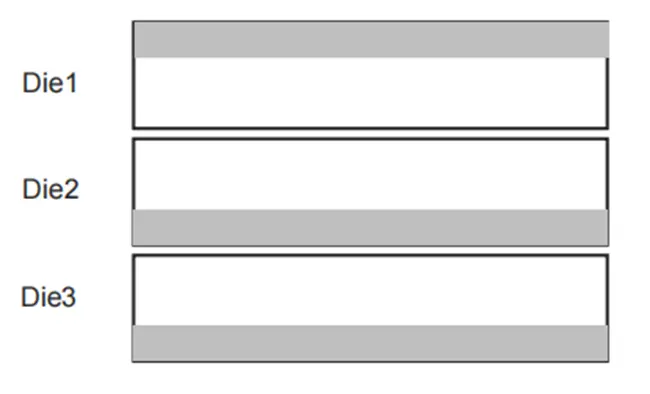

要求把所有模块划分到3个裸片上。不考虑整个芯片对外的I/O。堆叠方向如图所示,灰色表示衬底:

在满足硬性约束条件下,最优化以下两个目标:

1.3个裸片上模块的面积利用率尽可能相同。避免出现有些裸片过于拥挤而有些裸片大片空白的情况。利用率=(模块总面积+TSV总面积)÷裸片面积

2.裸片间bump/TSV数量尽可能少。

附加题——考虑模块布局与总线长

基本题并不考虑模块在版图上的具体位置,只计算其面积和连接数。附加题要求提出一种算法并尝试实现:在考虑模块布局(无缝铺满整个裸片区域,形状可以是矩形或直角多边形,如图8所示)的前提下,使总线长最短。

注1:由于利用率总是小于100%,因此铺满后每个模块的占地面积将大于它的初始面积。但不可小于初始面积。

注2:总线长的计算用模块几何中心之间的水平距离来简化。

注3:TSV假设均布在裸片上,可先不考虑其具体位置,但面积需算入。

Cadence简介

Cadence是电子设计领域的关键领导者,拥有超过30年的计算软件专业积累。公司基于智能系统设计策略,交付软件、硬件和IP,助力客户将设计概念转化为现实。Cadence拥有世界上最具创新精神的企业客户群,他们向消费电子、超大型计算机、5G通讯、汽车、航空、工业和医疗等极具活力的应用市场交付从芯片、电路板到系统的卓越电子产品。Cadence 已连续六年名列美国《财富》杂志评选的 100 家最适合工作的公司。

中国研究生创“芯”大赛简介

中国研究生创“芯”大赛(简称“大赛”)由教育部学位管理与研究生教育司指导,中国学位与研究生教育学会(国家一级学会)、中国科协青少年科技中心主办,清华海峡研究院作为秘书处。作为中国研究生创新实践系列赛事之一,大赛聚焦国家战略需求,助力国家急需、重点发展领域高层次创新人才培养。针对“卡脖子”领域,由院士领衔专家委员会、知名学者、企业高管担任评委,是面向全国高等院校及科研院所在读研究生的一项团体性集成电路设计创意实践活动。鼓励办好研究生创新实践大赛”被写入教育部、国家发展改革委、财政部《关于加快新时代研究生教育改革发展的意见》,研究生获奖情况被研究生教育重要评估评审认可。

赛事宗旨为:创芯、选星、育芯。

大赛面向中国大陆、港澳台地区在读研究生(硕士生和博士生,含留学生)和已获得研究生入学资格的大四本科生(需提供学校保研、录取证明)及国外高校在读研究生。参赛队伍可提交集成电路芯片设计相关创意、创新或创业作品。大赛分为两级赛程:初赛和决赛。初赛分为自主命题和企业命题,评审采用网络或会议评审的方式进行,决赛为现场赛,采用答题、答辩及竞演相结合的方式进行。

2022年第五届大赛将在杭州萧山区举办,承办方为浙江大学杭州国际科创中心。决赛同期还将举办集成电路产业招聘会,集成电路学术论坛等活动,邀请来自学界及业界嘉宾分享经验,促进集成电路产学研融合及科技成果转化,促进产业创新创业生态、加强人才供需对接。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。