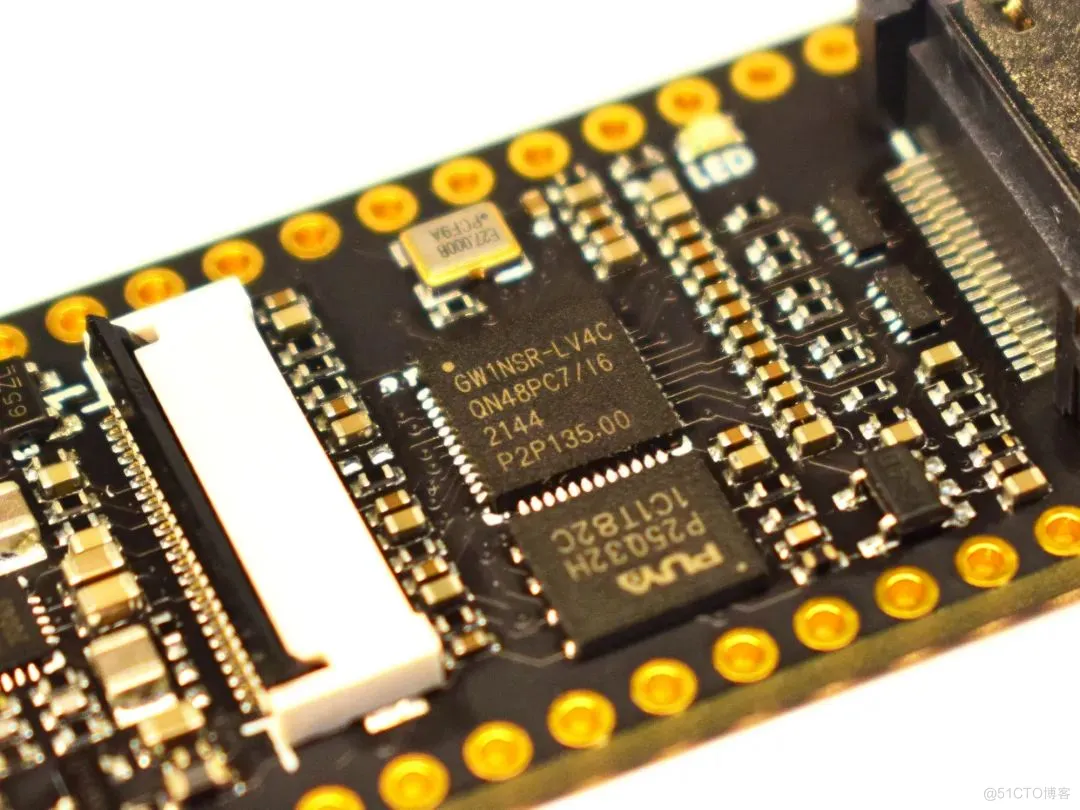

本篇文章介绍高云GW1NSR-4C FPGA基本原语和IP配置、使用和修改,以及如何在ModelSim环境下仿真这些IP和原语,基于TangNano 4K开发板。

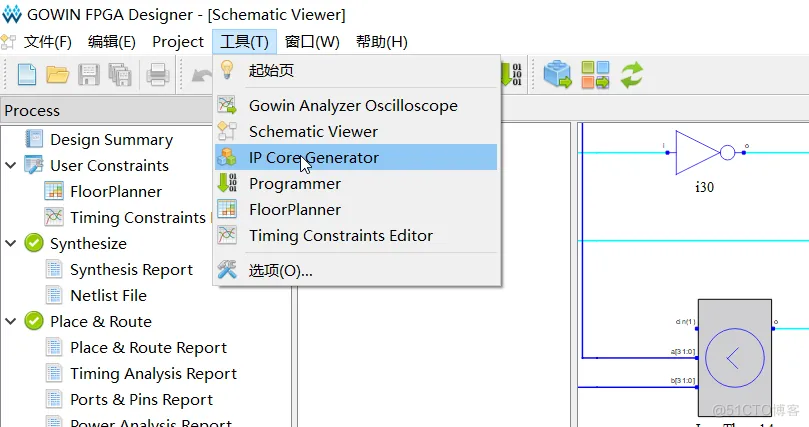

打开高云云源软件,点击工具->IP Core Generator可以调出高云IP核生成工具。

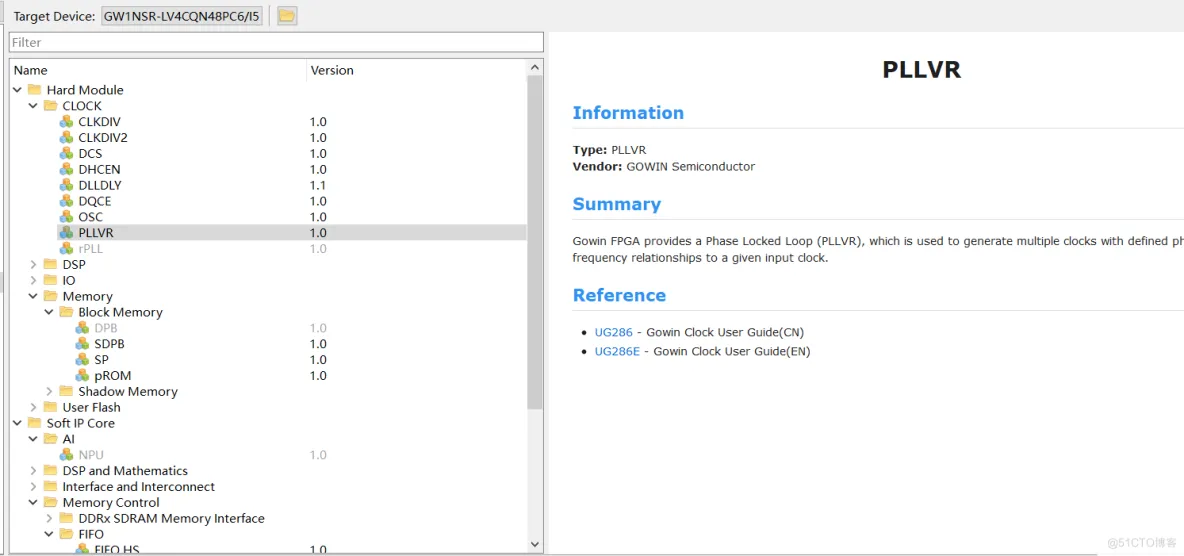

可以看到当前使用的器件支持的各类型IP核,如果不支持,IP核为灰色不可选,右侧有当前IP使用的中英文说明文档,点击可以直接下载。

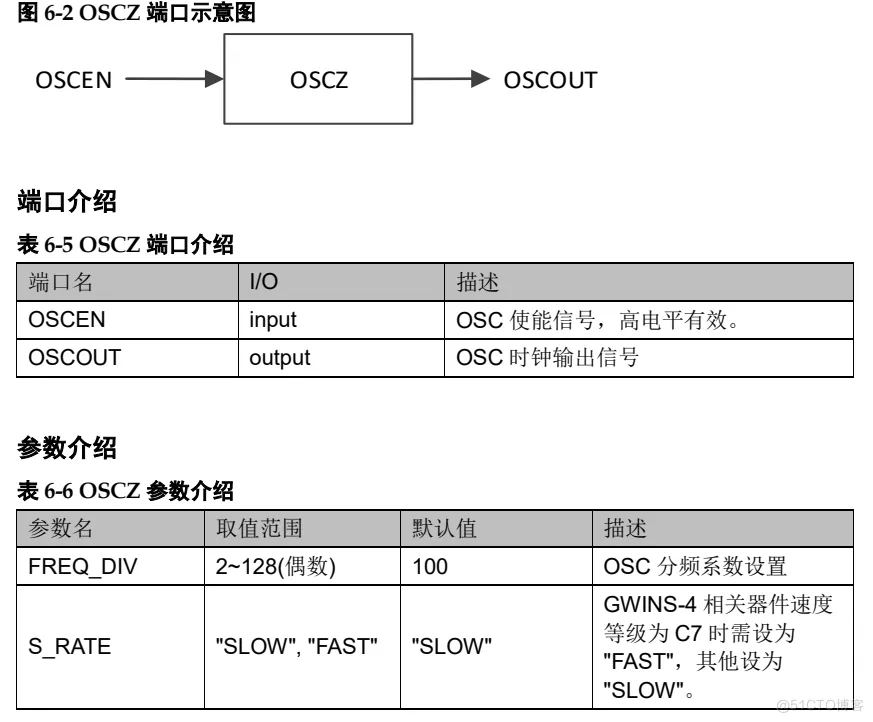

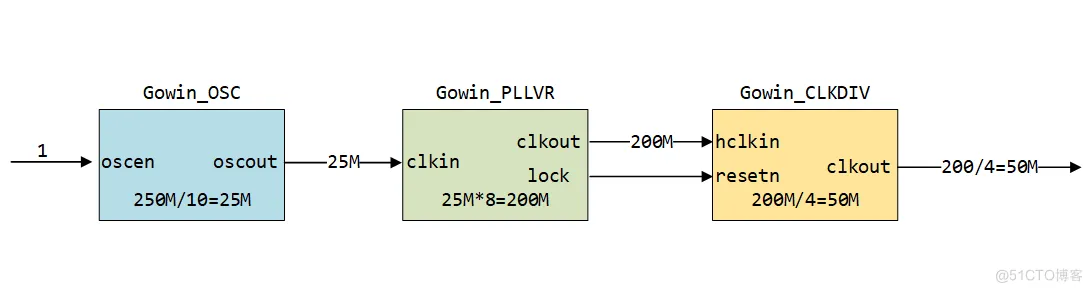

GW1NSR-4C芯片内部集成了一颗250MHz的时钟晶体,可以配置2-128偶数分配系数,带使能端。本次示例我们配置成输出25MHz输出,即10分频。

模块名称,保存路径可自定义,这里保持默认设置。

最终生成的文件:

module Gowin_OSC (oscout, oscen);output oscout;input oscen;OSCZ osc_inst ( .OSCOUT(oscout), .OSCEN(oscen));defparam osc_inst.FREQ_DIV = 10;defparam osc_inst.S_RATE = "SLOW";endmodule //Gowin_OSC1.2.3.4.5.6.7.8.9.10.11.12.13.14.

我们也可以在自己的设计中直接例化OSCZ原语来使用。

关于高云FPGA时钟资源的介绍,可以查看云源软件安装目录下的UG286文档:

\Gowin\Gowin_V1.9.8.07_Education\IDE\doc\CN\UG286-1.9.4_Gowin时钟资源(Clock)用户指南.pdf1.

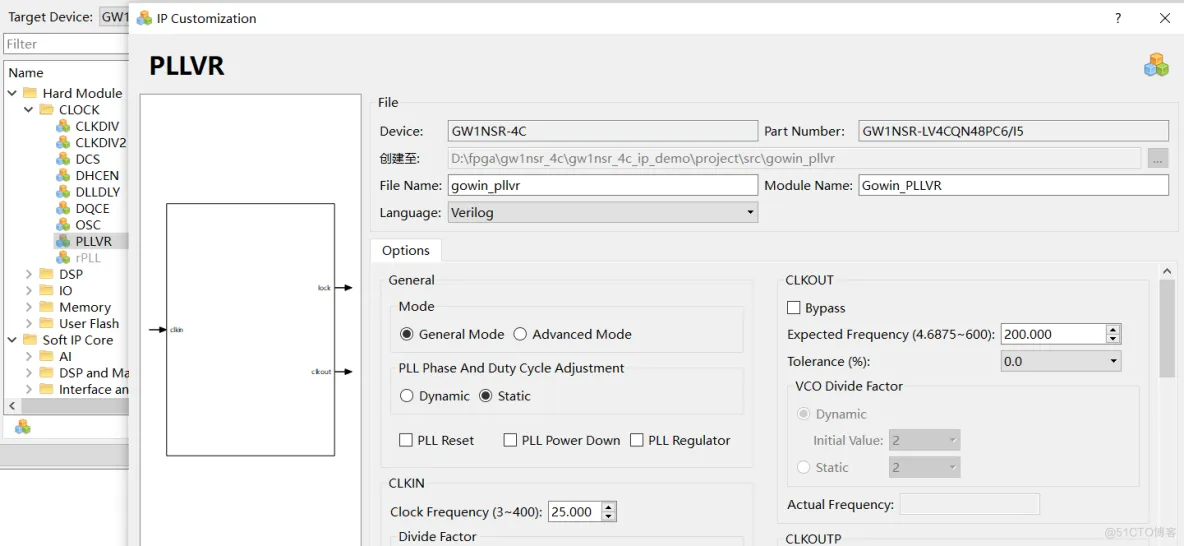

和OSCZ一样,选择PLLVR进行配置,指定PLL输入频率为25MHz,输出频率为200MHz。

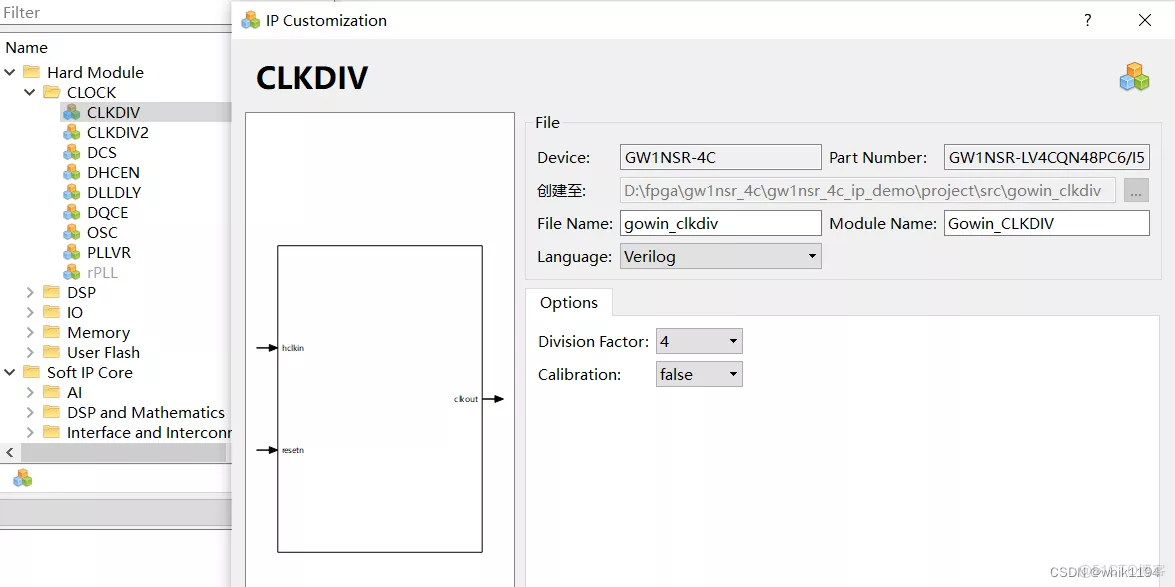

选择CLKDIV配置分频器系数为4

为了同时调用这几个IP,我们按照如下图进行连接。

顶层文件:

/*************************************************************** * Copyright(C), 2010-2022, WeChat:MCU149. * ModuleName : top_hdl.v * Date : 2022年10月02日 * Time : 20:19:39 * Author : WeChat:MCU149 * Function : gw1nsr-4c led driver demo * Version : v1.0 * Version | Modify * ---------------------------------- * v1.0 ..... ***************************************************************/module top_hdl( //Inputs input gclk, // 27MHz input gresetn, input key, //Outputs output reg led);//1.parameter//2.localparamlocalparam KEY_PRESS = 1'b0; localparam KEY_RELEASE = !KEY_PRESS;localparam LED_ON = 1'b1;localparam LED_OFF = !LED_ON;localparam LED_PERIOD1 = 50_000_000 / 2 ; //500ms=27_000_000/2localparam LED_PERIOD2 = 50_000_000 / 10; //100ms=27_000_000/10//localparam LED_PERIOD1 = 100; //simulation//localparam LED_PERIOD2 = 200; //simulation//3.regreg [31:0] cnt;//4.wire wire [31:0] CNT_MAX = (key == KEY_PRESS) ? LED_PERIOD2 : LED_PERIOD1;wire clk_osc; //250/10=25MHzwire clk_pll; //25*8=200MHzwire clk_div; //200/4=50MHzwire pll_locked;//5.assign//6.alwaysalways @ (posedge clk_div) begin if(!gresetn) begin cnt <= 'd0; end else begin if(cnt >= CNT_MAX) cnt <= 'd0; else cnt <= cnt + 'd1; endendalways @ (posedge clk_div) begin if(!gresetn) led <= LED_OFF; else if(cnt == CNT_MAX) led <= !led; // led <= (led == LED_OFF) ? LED_ON : LED_OFF;end//7.instance//osc onchip, 250MHzGowin_OSC osc_250m( //Inputs .oscen(1'b1), //Outputs .oscout(clk_osc) //250/10=25MHz);//25*8=200MHzGowin_PLLVR gwin_pll( //Inputs .clkin(clk_osc), //25MHz //Outputs .clkout(clk_pll), //200MHz .lock(pll_locked));//200MHz/4=50MHzGowin_CLKDIV gwin_div( //Inputs .hclkin(clk_pll), //200MHz .resetn(pll_locked), //Outputs .clkout(clk_div) //50MHz);endmodule //top_hdl end1.2.3.4.5.6.7.8.9.10.11.12.13.14.15.16.17.18.19.20.21.22.23.24.25.26.27.28.29.30.31.32.33.34.35.36.37.38.39.40.41.42.43.44.45.46.47.48.49.50.51.52.53.54.55.56.57.58.59.60.61.62.63.64.65.66.67.68.69.70.71.72.73.74.75.76.77.78.79.80.81.82.83.84.85.86.87.88.89.90.91.92.93.94.95.96.97.98.99.100.101.102.103.

和上一篇笔记实现的效果是一样的,按键按下LED快闪,按键释放LED慢闪,只不过本工程没使用到外部的晶体。

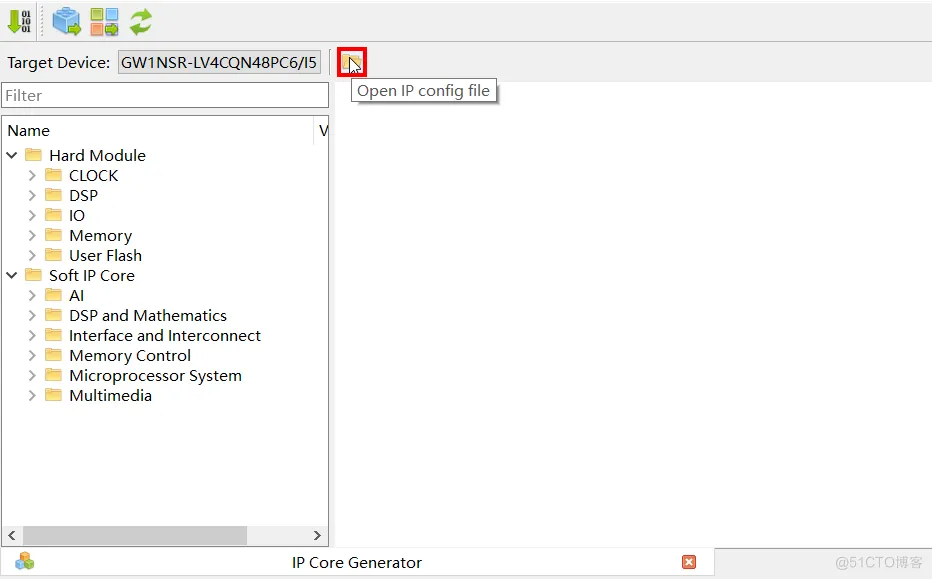

云源软件支持对已经配置的IP核进行修改,说实话我一开始并没有找到这个功能,还以为无法修改呢,后来看了官方的视频教程才发现支持修改已经配置的IP。

首先打开IP核生成界面,点击打开图标。

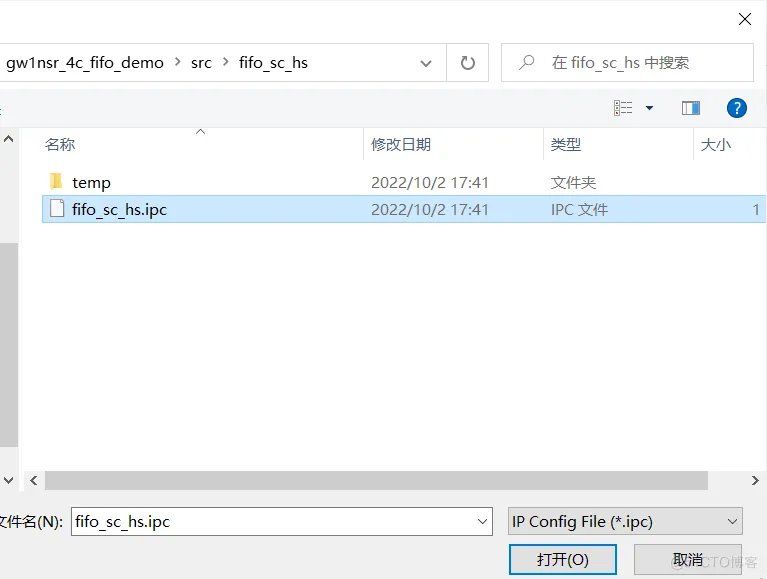

找到要修改的IP核文件夹下的ipc文件打开。

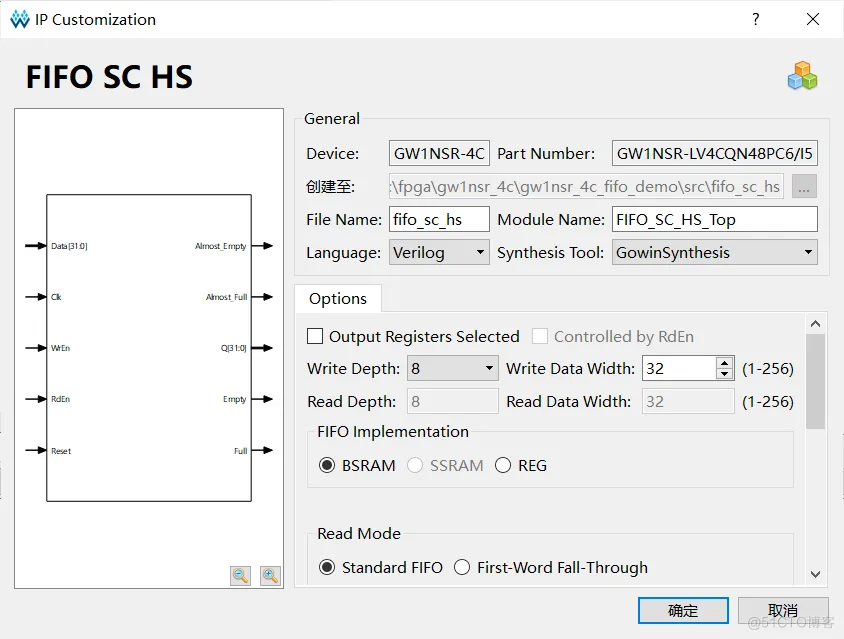

这样就可以进行修改了

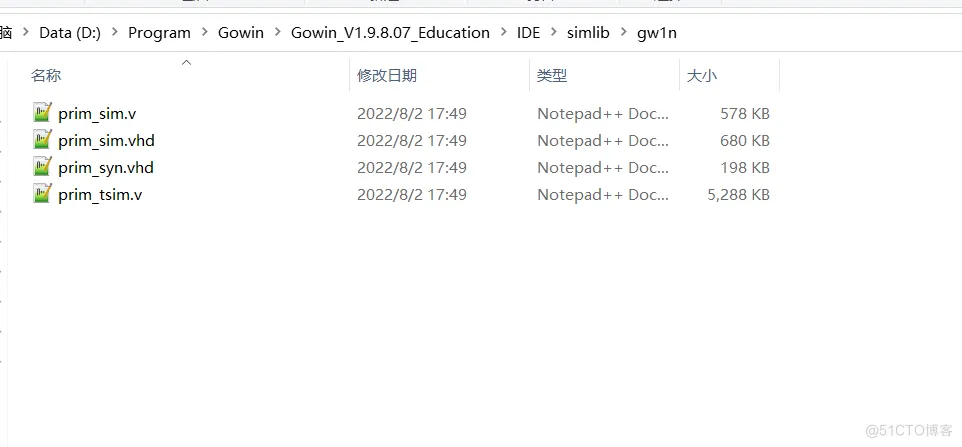

高云云源软件不包含仿真工具,需要借助第三方工具来完成功能仿真,如果涉及到官方的IP调用,比如PLL,OSC,FIFO等IP的仿真,需要进行添加一个官方的IP仿真库文件,文件路径为:

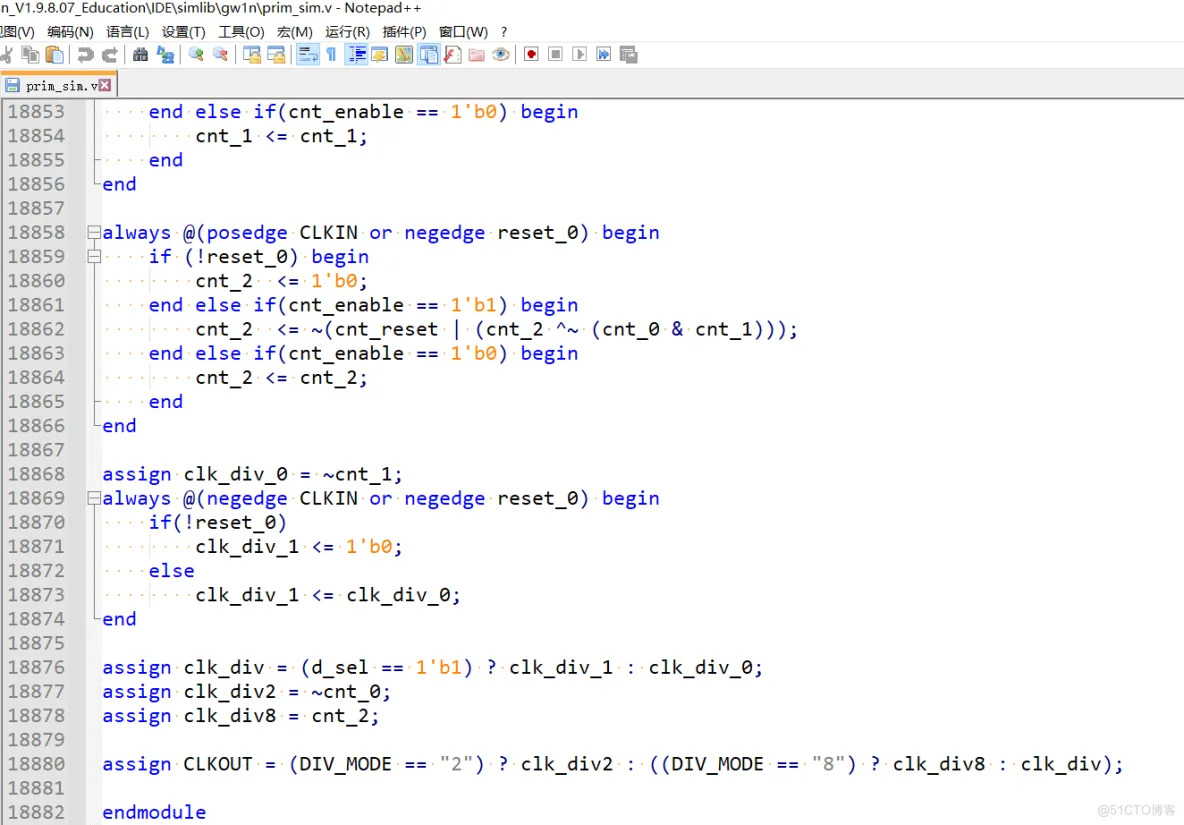

D:\Program\Gowin\Gowin_V1.9.8.07_Education\IDE\simlib\gw1n\prim_sim.v1.这个文件大小约600KB,近两万行代码,包括高云所有IP核的仿真模型,可以在Modelsim或其他第三方仿真工具中添加调用。

高云IP核仿真库文件内容完全开放,没有进行加密处理。

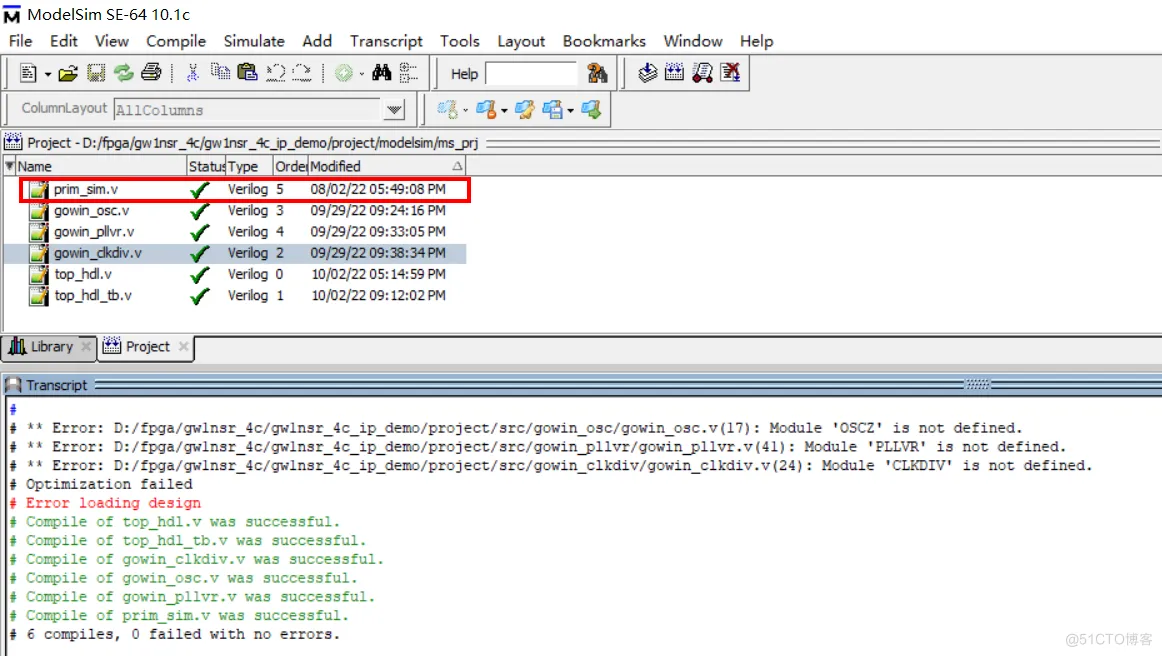

编译通过,仿真时会提示调用的模块未定义

把prim_sim.v添加到Modelsim工程,再次编译,执行仿真。

提示如下:

# ** Note: (vsim-3812) Design is being optimized...# # ** Error: (vopt-7052) D:/Program/Gowin/Gowin_V1.9.8.07_Education/IDE/simlib/gw1n/prim_sim.v(13111): Failed to find 'GSR' in hierarchical name '/GSR/GSRO'.# # Optimization failed1.2.3.4.5.

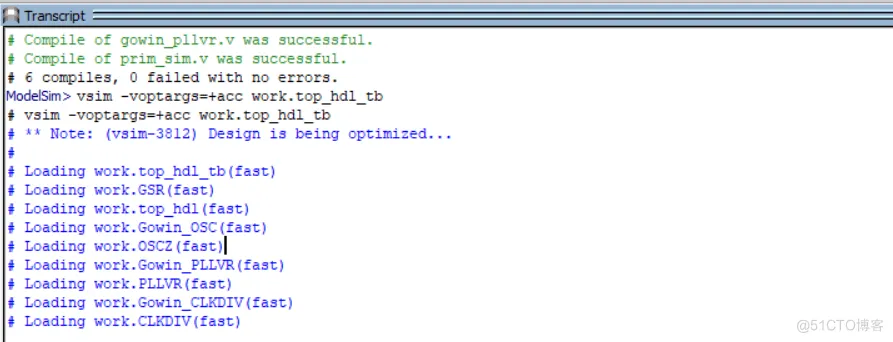

在Testbench中例化如下全局复位模块,因为仿真库中调用了此模块:

GSR GSR( .GSRI(1'b1));1.2.3.重新编译,成功执行仿真。

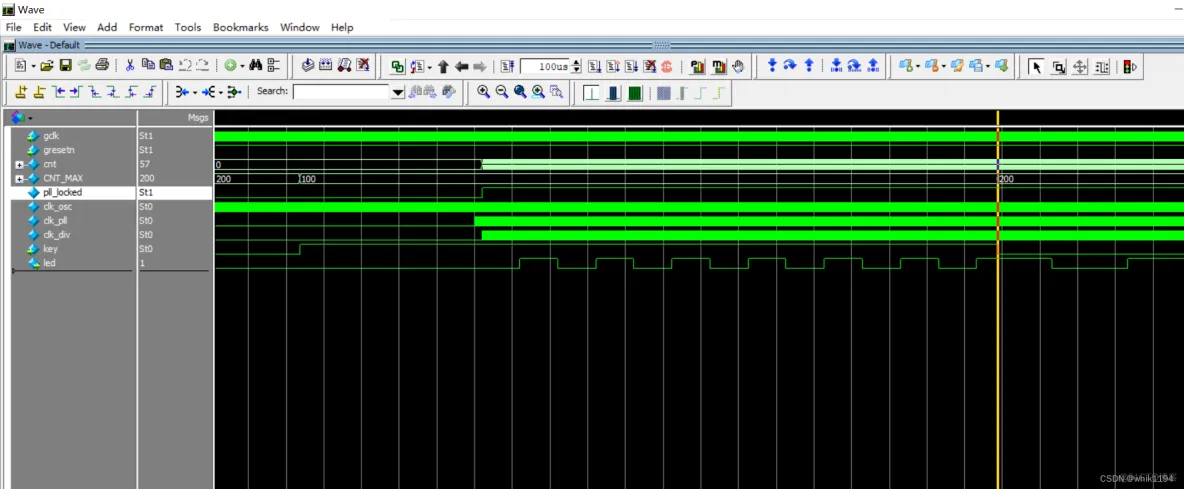

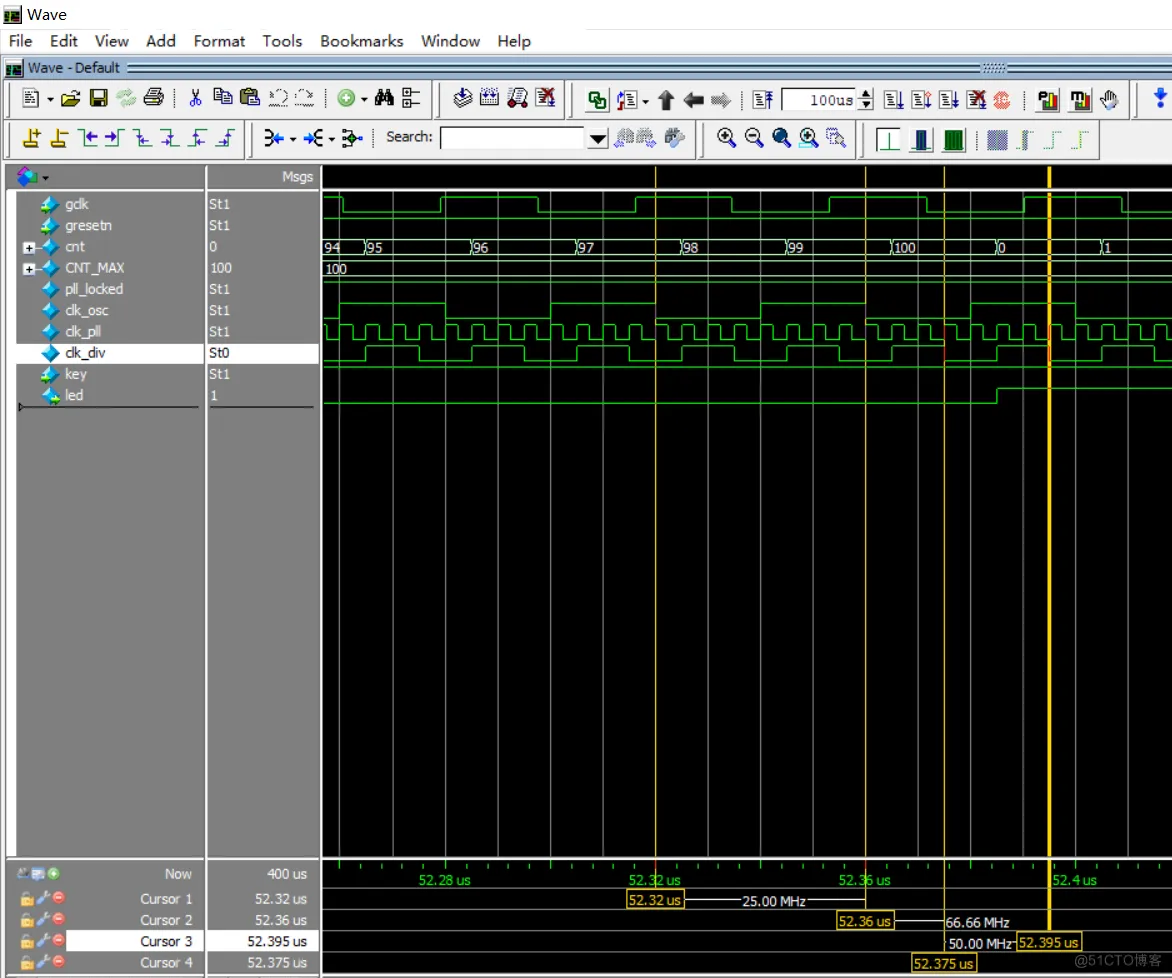

仿真波形:

OSC、PLL、DIV输出时钟频率和配置是一致的。

总的来说,GW1NSR-4C这颗FPGA可以使用的IP核不算太多,但基本的PLL,FIFO,RAM,DSP都有,还有一些非常实用的协议IP,如I2C,SPI,UART主机从机,以及之间的相互转换都有相应的IP,还有一些多媒体相关的IP,可以满足大多数的需求。

联合ModelSim仿真也比较简单,只需要添加一个仿真库文件即可完成所有IP的仿真,还是非常方便的。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...