define指令有四种语法:

语法一:`define <name> <string>

它可以用来定义参数,功能和parameter类似,例如:

`define WIDTH 8

reg [`WIDTH-1:0] data;

语法二:`define <name>

它只是表示定义了一个名为的变量,具体用法参看语法四。

语法三:

`ifndef <define_name>

<statements>;

`endif

该语法表示,如果名为<define_name>的变量被定义了,那么就将在编译的时候将的内容包含进来,否则不编译这部分内容。我们可以看出条件编译指令的作用跟条件生成语句比较类似,具体用法参看语法四。

语法四:

`ifdef <define_name0>

<statements>;

`elsif <define_name1>

<statements>;

<other branchs>

`else

<statements>;

`endif

该语法是条件编译语法的完全形式,用法举例如下:

`define AND

`ifdef AND

assign c = a & b;

`elsif OR

assign c = a | b;

`else

assign c = a;

`endif

由于AND已经被定义,那么c将被综合为a和b的按位与。如果以后设计需要该为用或门,则将第一行的编译指令改为如下即可:

`define OR

与条件生成语句一样,每次修改后必须重新编译才能生效。

时标指令是用来定义时间单位和时间精度的,它一般用于仿真和时序分析中,语法如下:

`timescale <number0> <unit0> / <number1> <unit1>

其中 表示在后续程序中,数值每增加1所对应的时间增加量; 表示了小数部分所能描述的精度。为了防止不必要的混淆,Verilog规定的值只能是1、10或者100。举例如下:

`timescale 10ns / 1ns

a = 1'b0;

#1;

a = 1'b1;

#0.5;

a = 1'b0;

#0.3;

a = 1'b1;

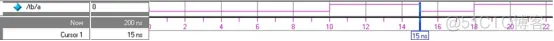

那么上述程序的执行结果如下:

包含指令对于复杂工程设计来说很有用,有了这个指令,我们就可以在一个文件中定义好工程系统中需要用到的参数、函数、任务等等,然后在需要使用这些资源的的文件中通过include命令将它们包含进来。这种做法非常像C语言中的头文件,因此我们一般都将被include的文件以“*.vh”命名,即verilog header。包含指令的语法如下:

`include "<file_name>"

举例如下:

`include "para.vh"

`include "../data/para.vh"

`include "c:/data/para.vh"

上述三条语句分别对应同一目录下的引用,相对路径引用和绝对路径引用。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...