准备好待验证电路的schematic和layout,并确保已经完成了DRC和LVS操作,这些内容已经在模拟IC版图绘制及DRC和LVS检查全流程演示进行了介绍。

同时准备好test bench的schematic以提供仿真验证环境,如下图所示

随后在该仿真cell下新建一个config文件

在弹出的窗口中,view选择schematic,use template,选择spectre并点击OK

至此便做好了前期准备工作,可以开始寄生参数提取。

在Layout界面打开PEX界面

选择工艺对应的PEX文件

如下图设置合适的PEX执行路径,方便后期文件管理

如下图勾选上自动生成PEX所需的电路网表

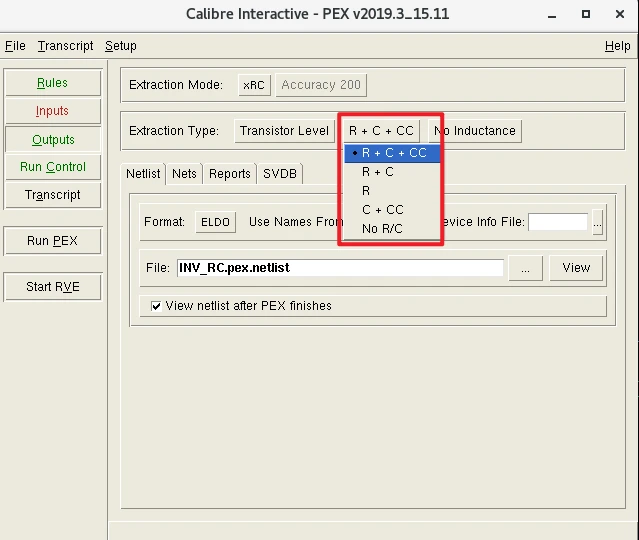

根据电路需要,可以在Extraction Type中选择合适的寄生参数提取方式和提取类型。

设计中常用的两种提取方式是Transistor Level和gate level提取,两者的区别如下:

TransistorLevel提取又称为flatten提取,它是把版图TOP全部打散后的寄生参数提取,精度最高,提取速度慢;

GateLevel提取会把版图Top到Xcells边界处的寄生进行提取,而不打散Xcells。该方式会忽略Xcell内部的寄生,提取速度较快。该提取方式一个典型的用途是防止MOM电容的重复提取发生,但是需要在Xcells中定义MOM电容。

Xcells可在下图中的菜单栏中进行指定,一般厂商会提供对应的文件。

根据电路的需求,可以选择对应的寄生提取类型

R代表寄生电阻,C代表节点对地的寄生电容,CC表示节点与节点之间的寄生电容。由于提R时会增加电路的节点个数,而仿真器的运算速度与电路节点数量正相关,故电路规模较大时一般选择C+CC的方式以加快验证。

NO R/C虽然不提取版图上的寄生电阻电容,但会引入MOS管的高阶效应(如WPE、STI等)以及相关的寄生二极管。

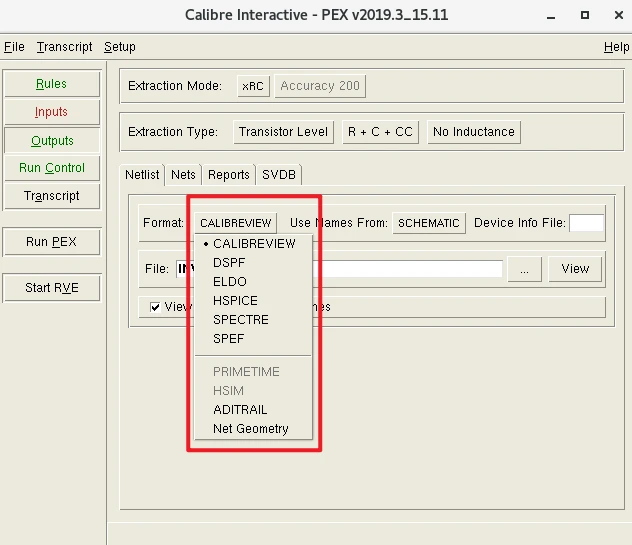

此处只对Calibreview和Spectre格式的后仿真作简单介绍:

Spectre是仿真器仿真时读取的网表格式。

Calibreview会将产生的网表封装在一个schematic文件中,同时其后续选项中也可以选择生成对应的spectre网表。

在File一栏中可以修改输出网表的名字和位置

随后点击左侧菜单栏中的Run PEX即可

如下图所示,类似DRC和LVS,可以将如上操作过的PEX设置保存为runset,方便后续导入使用

在有些工艺下跑LVS或PEX会报下述与subckt相关的错误

手动在网表后添加厂家的empty文件,每次提取时都要操作。

该文件一般和LVS,PEX文件在类似的位置

修改calibre setup,局部一次性操作,每次启动virtuoso时需要再操作。

1)从schematic或者layout的菜单栏中点击Calibre->Setup->Netlist Export Setup;

2)在弹出的窗口中Include File一栏,填入empty.subckt.sp的正确地址;

3)点击OK。

在工作目录下新建.cdsinit文件,如有则直接在文件内添加如下语句

cdlOutKeys=list(nil

'incFILE "路径/empty_subckt.sp";

)

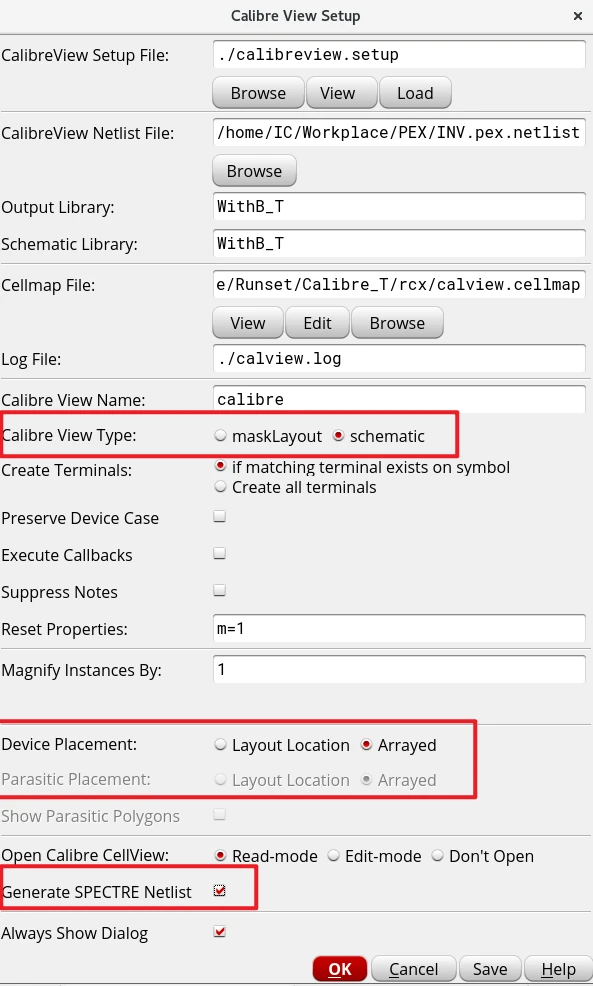

提参format选择Calibreview时,点击Run PEX后需要设置Calibre viewsetup,如下图需要在cellmap file处导入厂商提供的cellmap文件

另外可以根据需要产生所需的calibreview类型,器件和寄生在VIEW上的摆放规则,以及是否产生Spectre格式的网表

配置完成后点击ok,即会在当前cell下多出一个calibre的view(其名字可以通过修改上面配置中的calibreviewname进行修改,默认为calibre)。打开仿真环境cell的config,右键待仿真cell,如下图选择calibre,每次配置完成最好点击更新和保存。

随后点击ADE L或Explorer,按一般仿真操作进行仿真即可

提参format选择spectre时,点击Run PEX后无需像上述那样设置Calibre viewsetup。提参完成后直接打开仿真环境cell的config,右键待仿真cell,如下图SpecifySPICEmodel选择刚才产生的网表即可(选择.netlist结尾的文件),同样的每次配置完config后最好点击更新和保存。

后续类似上面基于Calibreview的后仿真,点击config界面中的ADE L或Explorer,按一般仿真操作进行仿真即可。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。