up人生第一个模拟IC项目马上要测试了(非常忐忑,发个文章积累下功德,开玩笑的)。主要是想记录一下完成项目的流程。比较粗糙,有什么建议意见欢迎评论区讨论~

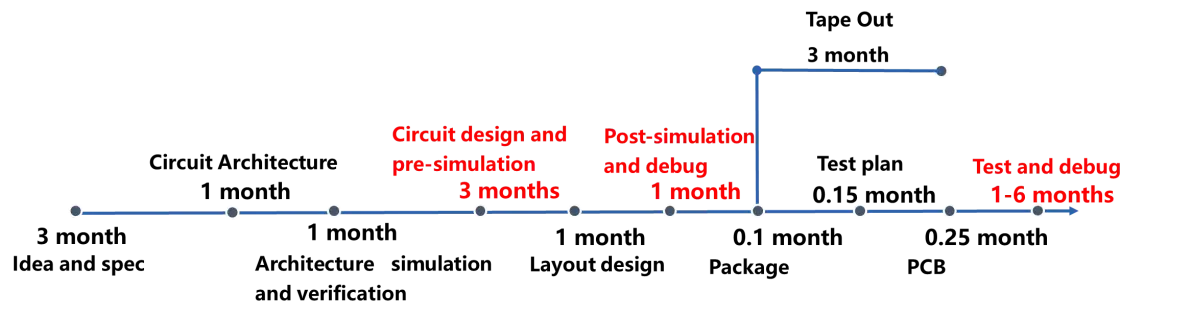

IC项目流程(画的比较简陋,见谅)

- idea阶段(3 month)

- 这一步需要看一个方向中很多论文(前5年),找到目前这个方向电路设计上的痛点和难点,产生自己的想法*多和同学老师讨论,多推导论文中的关键公式,确定关键指标及其意义*注意文献管理,善用系统文件管理/endnote/onenote/edge/adobe acrobat/word

- 电路架构设计(1 month)

- 确定自身电路的架构,在matlab等工具中搭建理想电路*注意关键电路的原理推导,性能指标的推导,善用matlab/mathtype/word/visio

- 架构逻辑验证(1 month)

- 在matlab等工具中仿真验证电路架构,分析可行性*善用simulink/TI-TiNA/Multisim搭理想电路,确定每个小模块的指标

- 电路设计与前仿(3 month)

- 前面是top-down的思路确定架构,具体电路以down-top的思路进行设计,在cadence等工具中先搭建小的模块,每个模块进行仿真,一步步形成顶层电路。*确定流片工艺库/cadence schematic绘制电路,生成symbol/schematic绘制仿真testbench/ADE L模块仿真

- 版图设计(1 month)

- 设计版图,从小模块到顶层电路*连线每层线尽量一个方向,相邻层线垂直/每个模块尽量方方正正的,端口放在四周/电路匹配/在原理图设计的时候,把握器件尺寸,可以设计的时候关注下版图布局布线/最后填dummy,可以用decap先大致填填,最后总体dummy用脚本填

- 后仿与debug(1 month)

- 根据LVS等工具提取带寄生参数的版图网表,进行后仿,与前仿结果对比

- 性能仿真可以只仿core,但功能仿真一定要包含pad,避免顶层与pad之间的连接出现问题*corner/temp/var,很多testcase的仿真,利用ADE XL进行后仿,选择config view,电路用calibre/assura等提取的包含寄生的网表*在电路前仿完成后,对电路的任何结构/器件参数上的改动都要非常小心,很容易出问题*每次版图DRC/LVS的问题,记录下来,积累为check list,以后画版图要注意这些问题,比如ESD保护/Latch Up效应

- 流片(3 month)

- 到厂子流片,大概3个月*把版图生成的GDSII给foundry,然后就是漫长的等待

- 封装方案(0.1 month)

- 确定封装采用的方案,是QFN/QFP/COB...,每个引脚连接什么PAD,地线怎么处理*每种封装的尺寸,对应的PCB model...

- 测试方案(0.15 month)

- 结合仿真的内容,确定测试项目,测试用到的仪器,每个测试项目的操作步骤和方法*在等待流片回来的日子里也不要闲着呀*找到每个测试仪器的document,浏览一下*确定PCB需要的物料和PCB model,该买的买,该画的画

- PCB设计(0.25 month)

- 根据封装方案、测试方案,确定PCB设计,利用Altium Designer/PADS等工具设计测试板PCB

- 这一步一定要注意走线,与预期的测试电路符不符合,能不能完成测试项目*飞线尽量少,主信号线尽量清晰,粗短,与其他信号隔开*高速信号隔开,大电流小电流走线隔开*画好生成PCB了,可以打印出来,在测试间模拟操作一下

- 测试(1 month-6month)

- PCB、芯片、物料焊接之后,进行测试*这一步注意实验室资源协调,记录的数据用excel记录,matlab处理,绘图*就算功能测试不出来,也有很多能测试的以及debug,一定要重视,珍惜自己测试遇到的坑

- 归档

- 整理全过程文档,归档,方便之后回看

- 每一步都建议做好文档管理和文档撰写,比较重要文档:

- 调研文档:每篇文献的总结与留档

- 设计文档:电路设计原理,设计过程,形成一个整体的文档,边做边写,前仿的时候大体已经完成了,后面就是不断更新迭代

- 项目PPT:一个随时可以用来讲解项目的PPT

- 仿真路径和state:注意保存仿真电路的路径和对应仿真环境设置的state路径

- 测试方案:测试仪器的学习,测试项目的意义和计算,处理数据和绘图用到的matlab代码,PCB设计文档等

- 过程中遇到的坑和解决办法的记录

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。