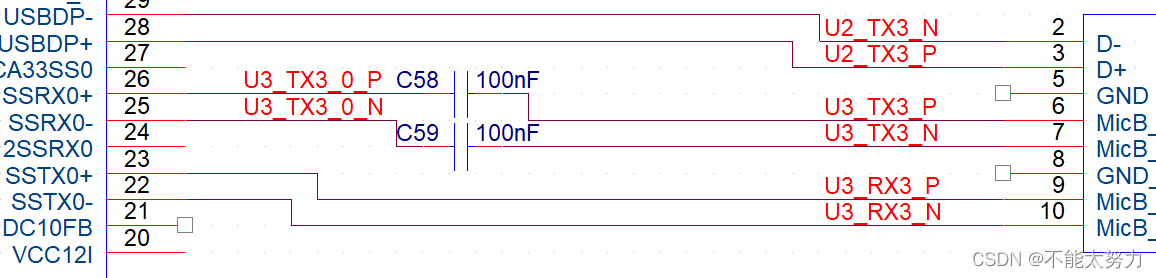

1.如下图所示,原理图在设计时会有过电容的差分线,我以 USB3.0 的TX引脚为例,其线上有100nF的耦合电容,另外两组线是U3的RX引脚和U2的数据引脚。

2.以上三对线呢假设需要组内差分布线,并且组间等长(实际不需要组间等长设计,只需每对差分信号组内等长即可,注意阻抗要求)。

3.生成好netlist后导入到allegro中开始布线设计(保证原理无误,并且PCB封装正确)。

4.原理图注意net信号名称要用_P/_N或者-/+结尾。

1.在allegro放置好相关元件后,并且 show rats后,如下图所示。

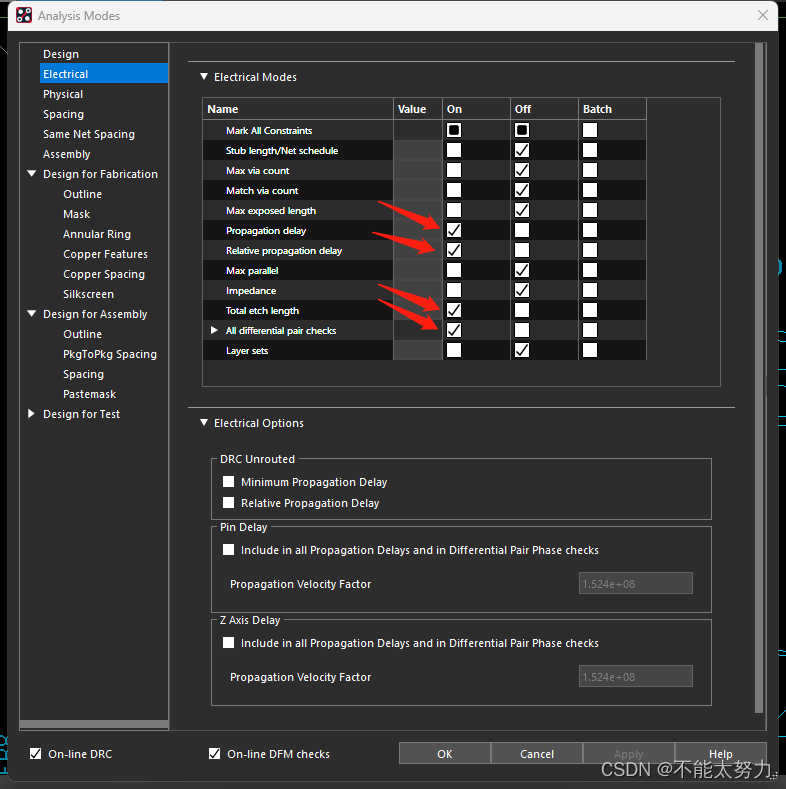

2.打开stepup->constraints->modes->electrical面板,勾选相关的选项如下图所示(否则布线时不显示进度条)。

打开propagation delay信号传播延时(差分对约束)

打开ralative propagation delay相对信号传播延时(其他走线长度和基准的差别必须在一个范围内)

打开total etch length总的走线长度(用来约束一根或者一组的线的总长度最大和最小)

打开all differential pair checks(所有的差分对检查)

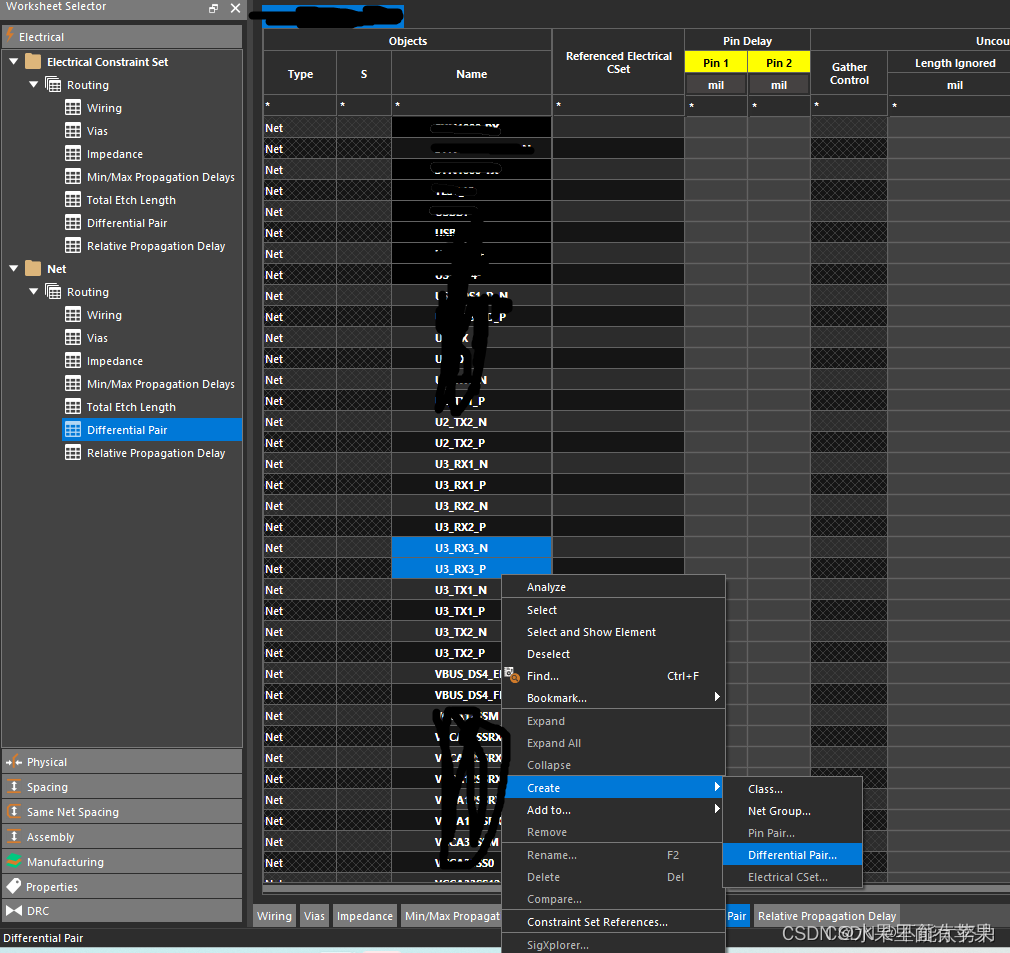

3.打开stepup->constraints->constrainst manager面板(设置相关的约束)

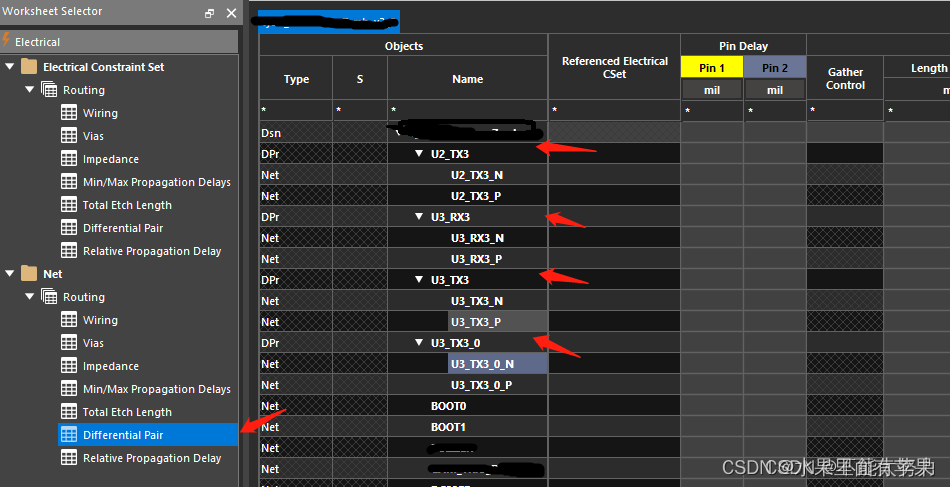

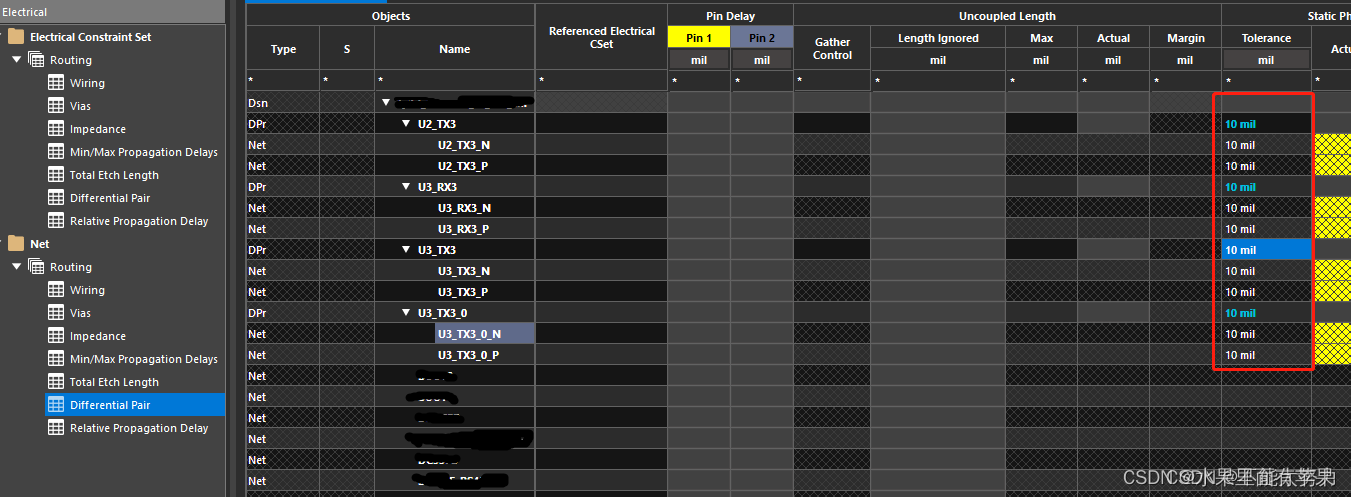

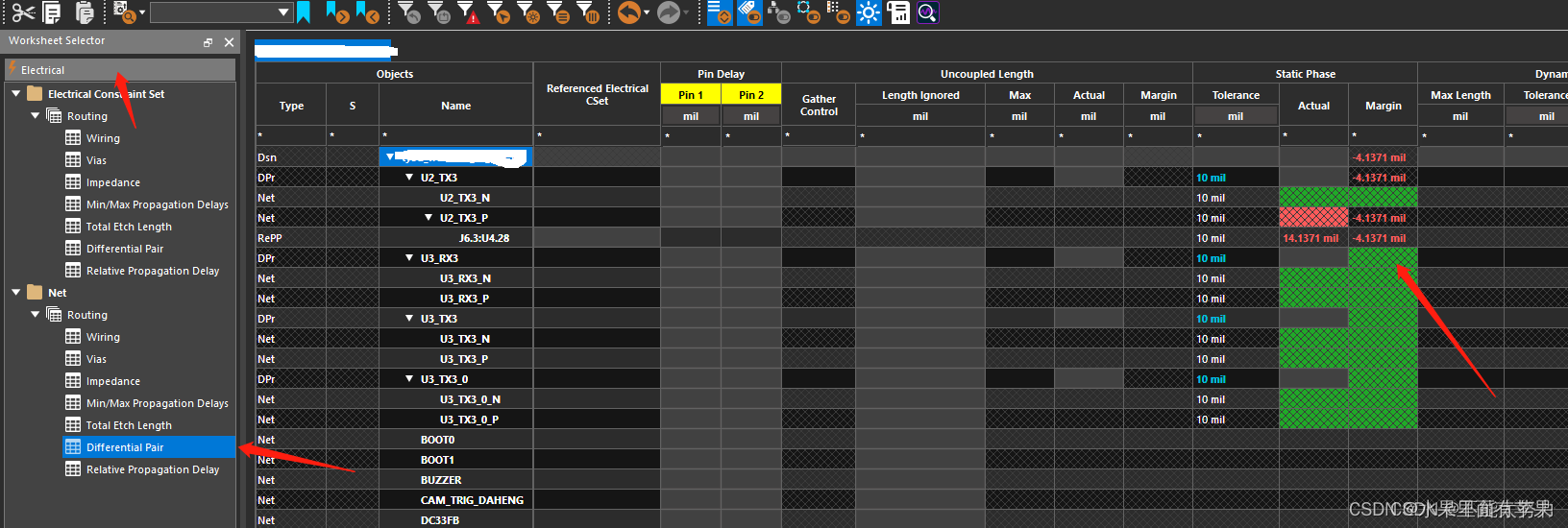

选择electrica->differential pair(电气设置)分别找到需要等长的差分对,如下图,并create->Differential Pair(建立差分对组),并且输入好名称(后续可修改,自己清楚即可)建立好的如下图。

上面设置好后,在static phase->tolerance选项内输出差分对组内等长的容忍范围,这里输入10MIL只是一个示意,实际情况根据对应的信号类型来定。

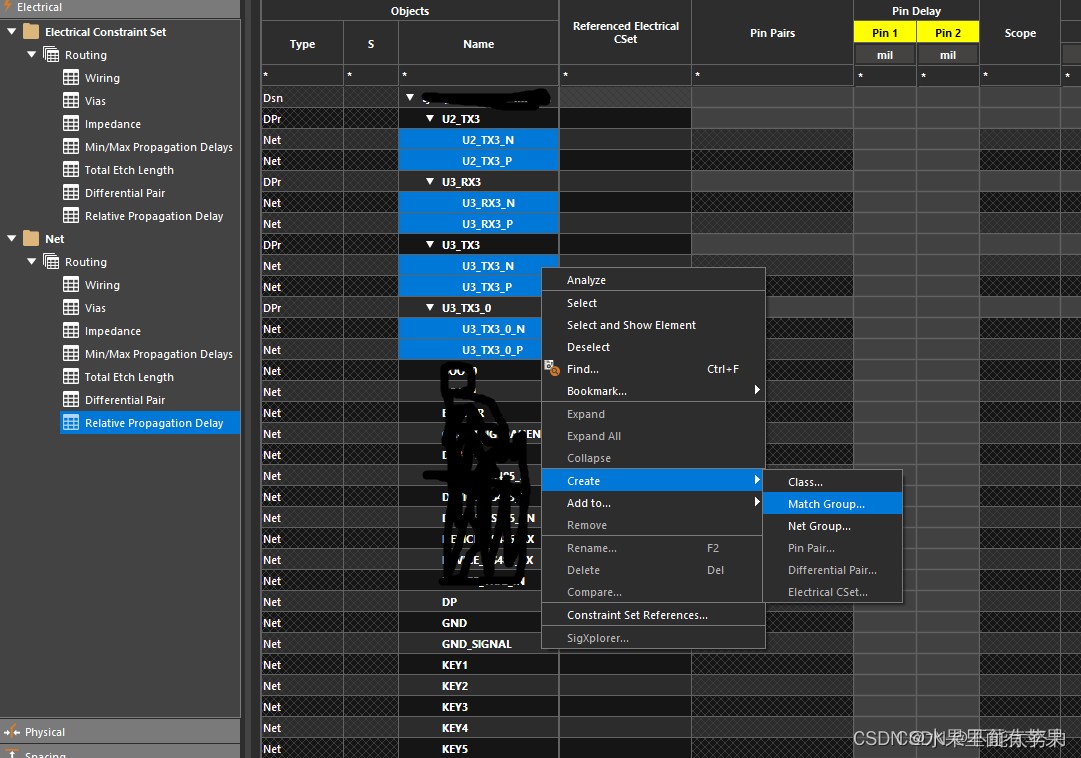

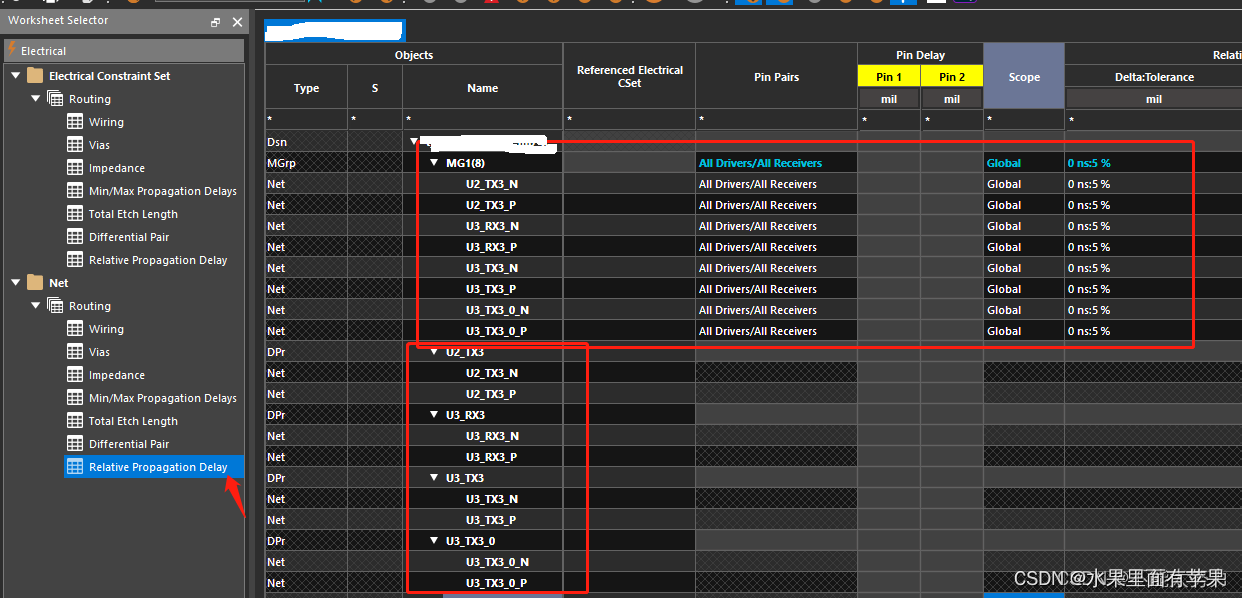

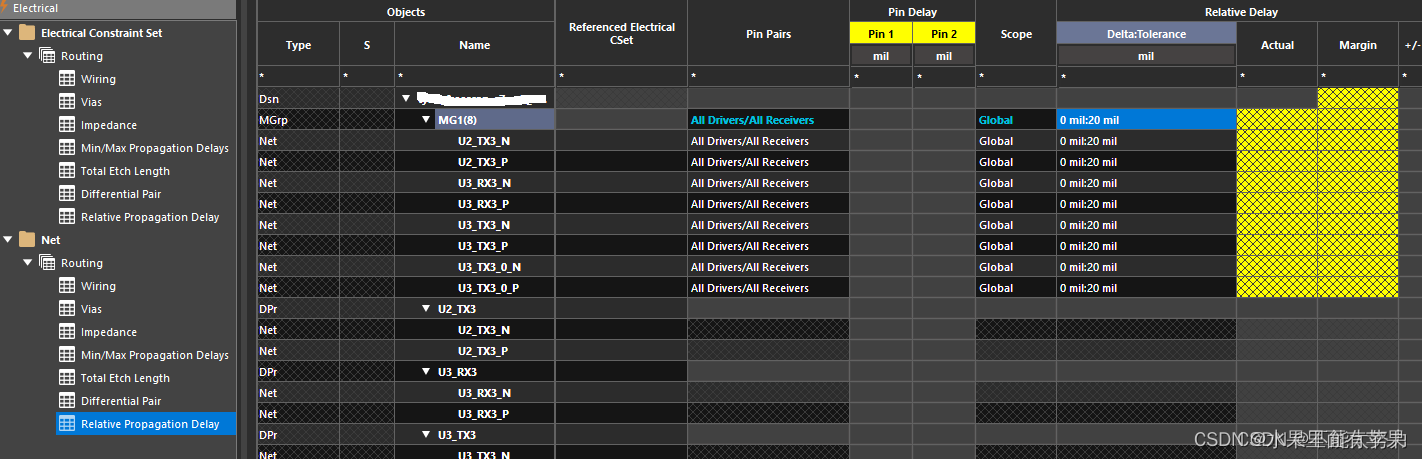

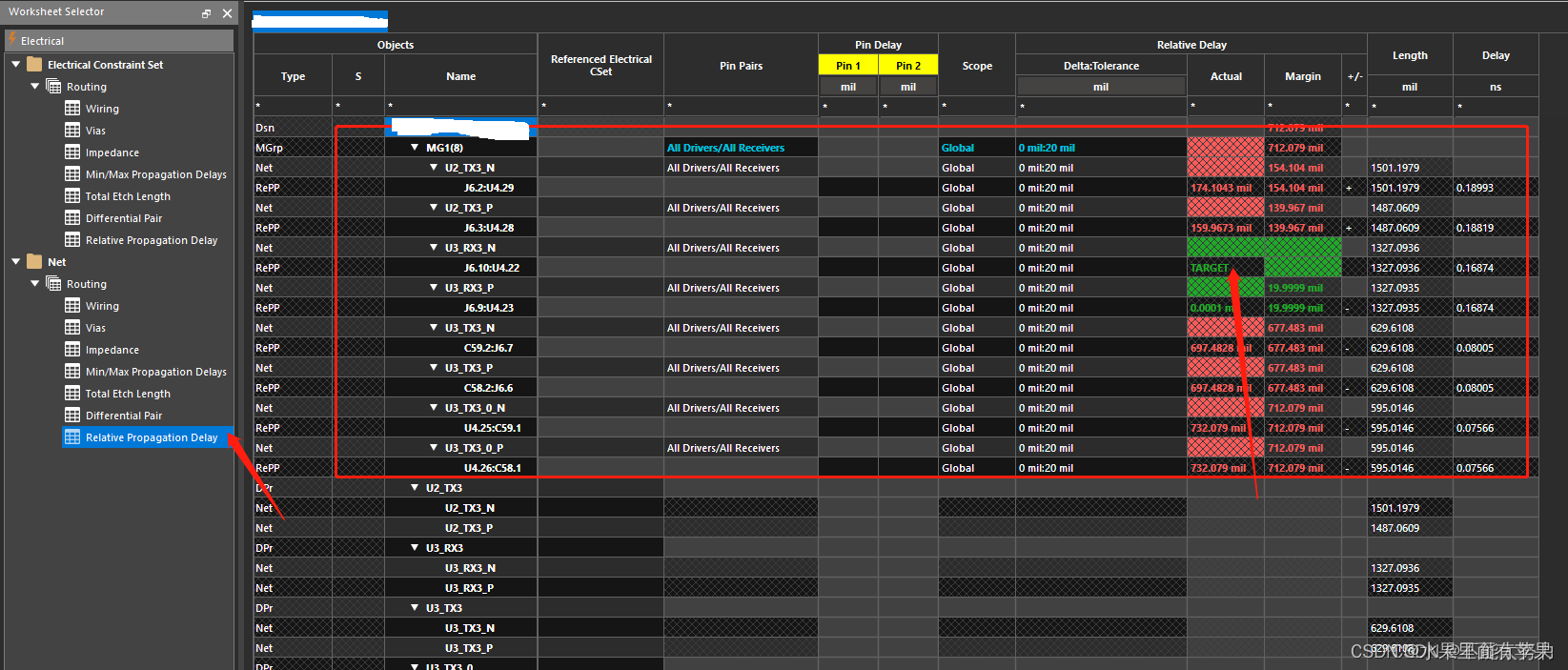

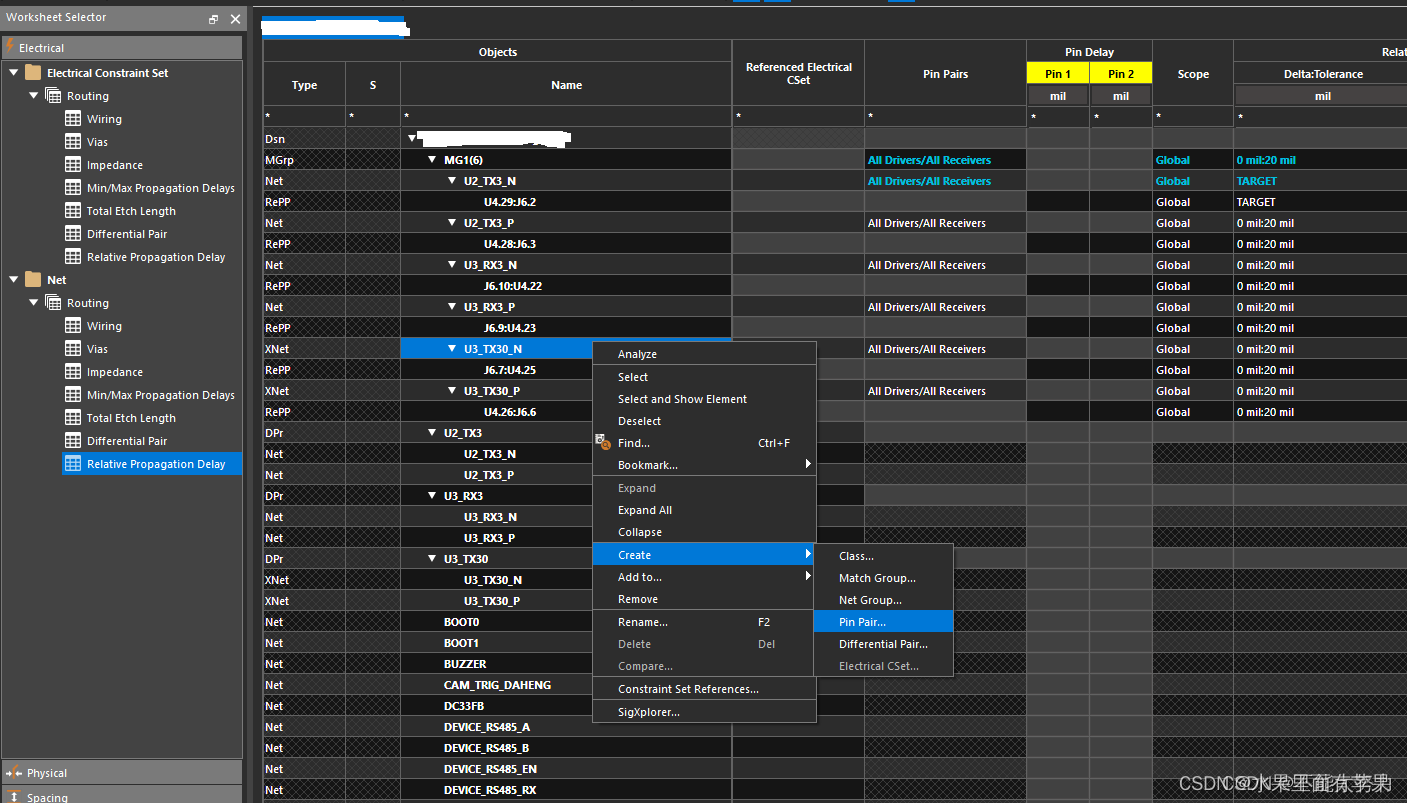

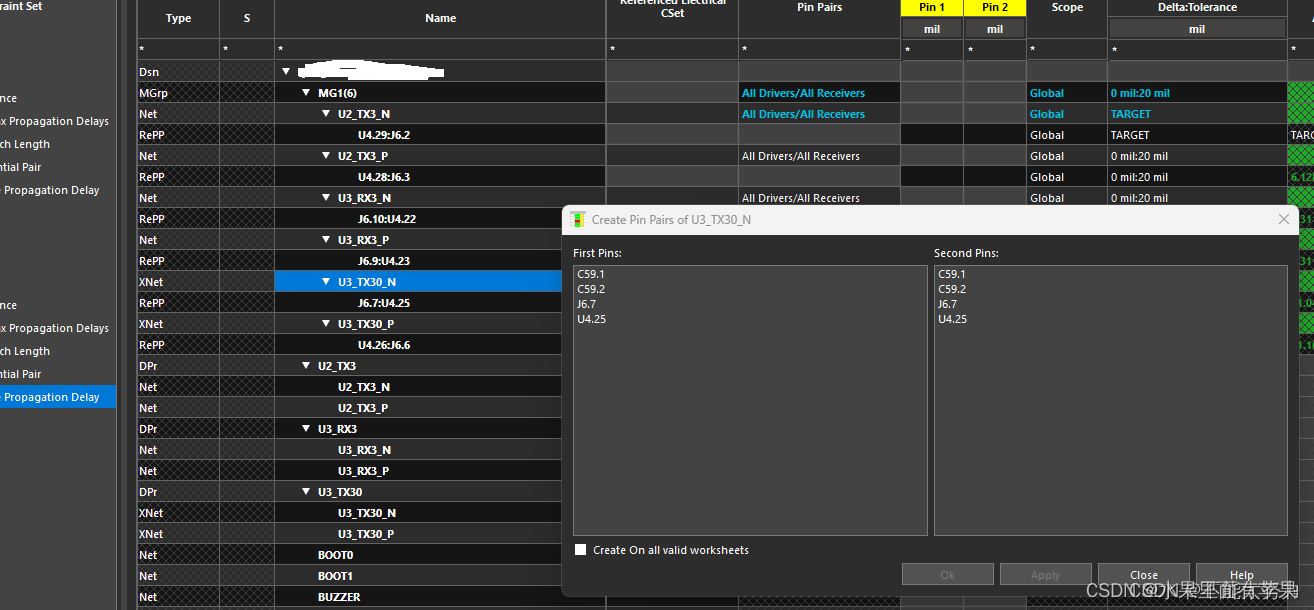

4.选择electrica->relative propagation delay(建立信号组),选择对应的需要组内等长的信号线。建立match group

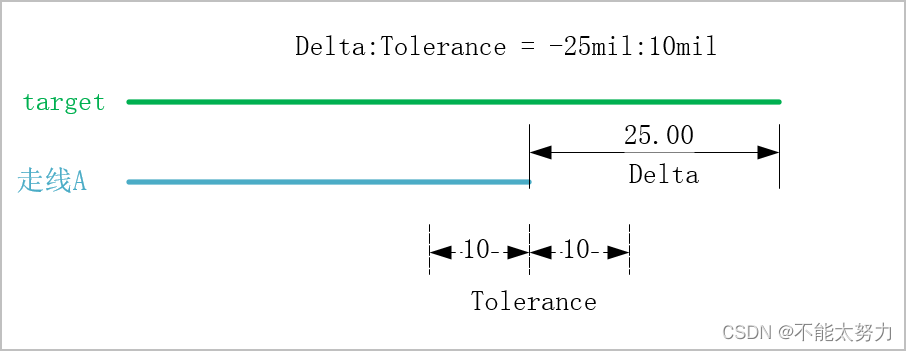

在relative delay->delta:tolerance下输入组间等长的范围值。如下,这里解释一下delta:tolerance是在以target length + Delta为原点,以Tolerance为半径的区间内取值。

设计好的如下图,这里设置0 mil:20 mil。

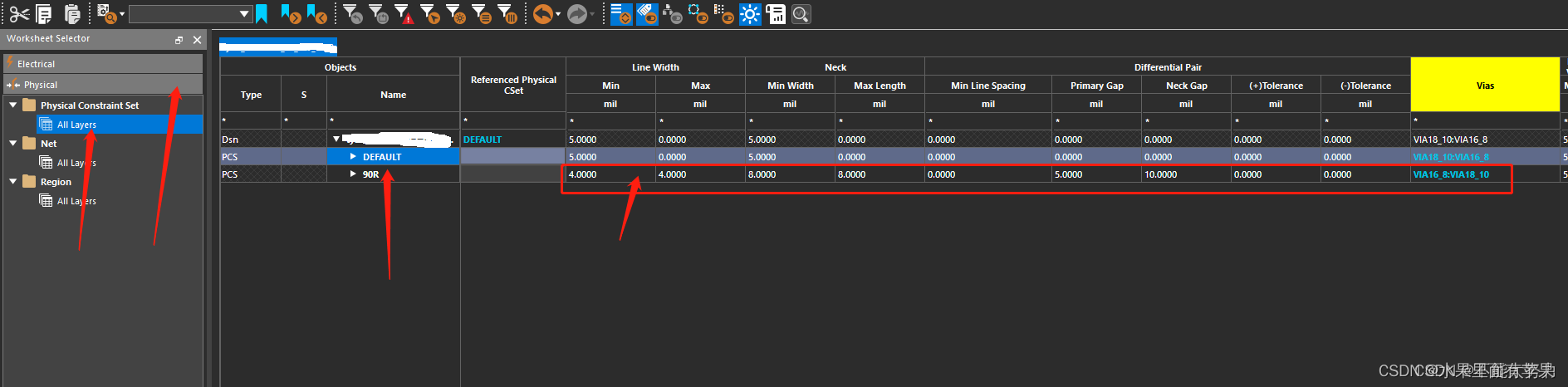

5.以上设置好后,再到physical(物理规则)设置窗口。选择physicla constraint set->all layers,新建一个physical CSet,我这里名字取90R。并设置好线宽,第二线宽,间距,第二间距值,并选择好对应的via。

6.还在当前窗口选择Net->all layers(分配上一步设置的属性值给到对应的差分线)

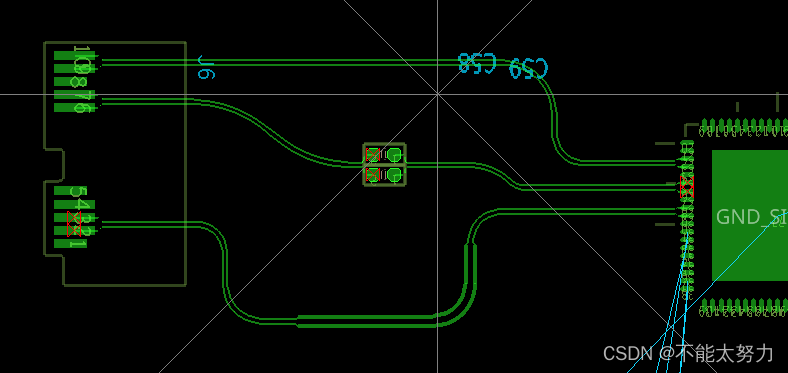

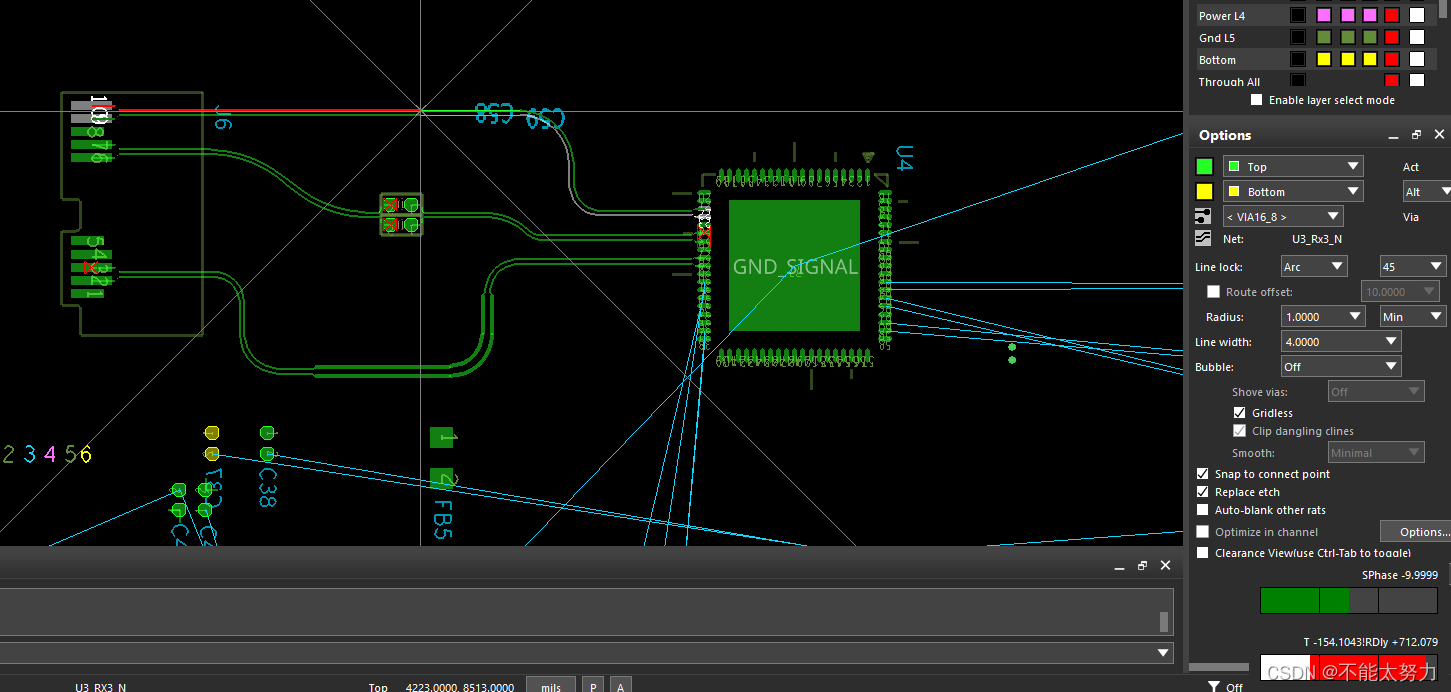

7.以上设置好后就可以在PCB中去画对应的差分线了,我们先检验一下之前设置的是否生效。回到 layout 主界面。如下如图。差分线是可以布线了,并且第二线宽也生效了。报错先忽略。

我们在布线时右下角也会显示当前的等长匹配情况。

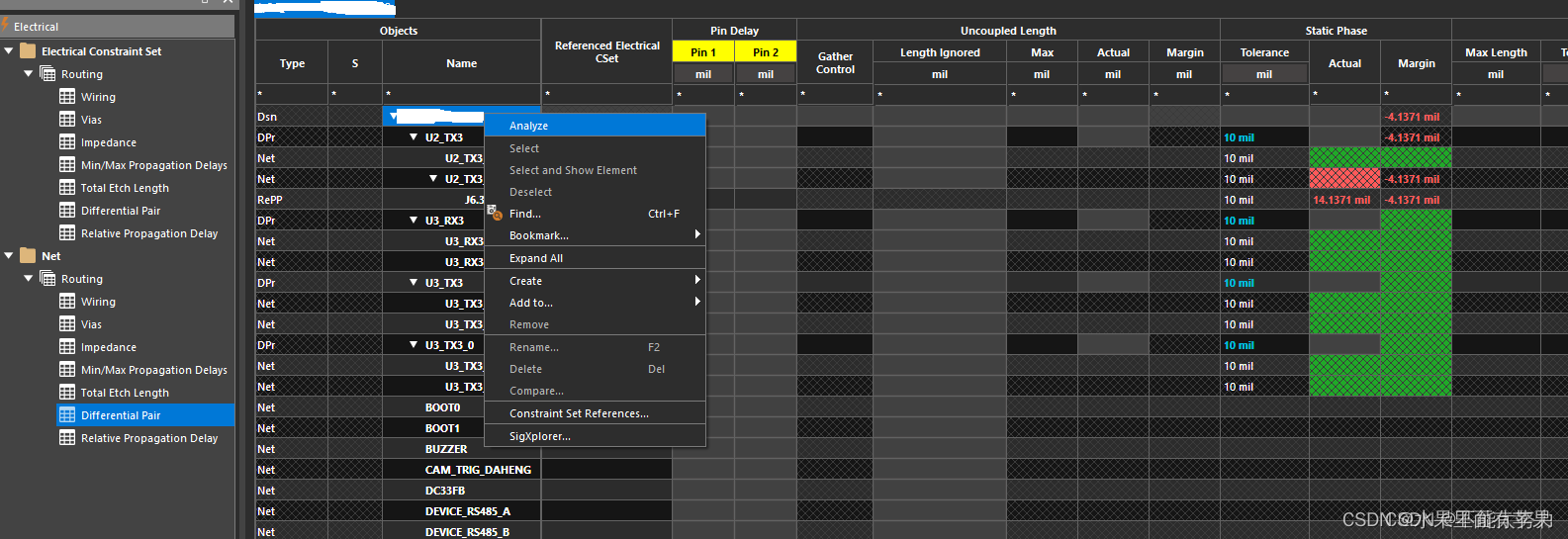

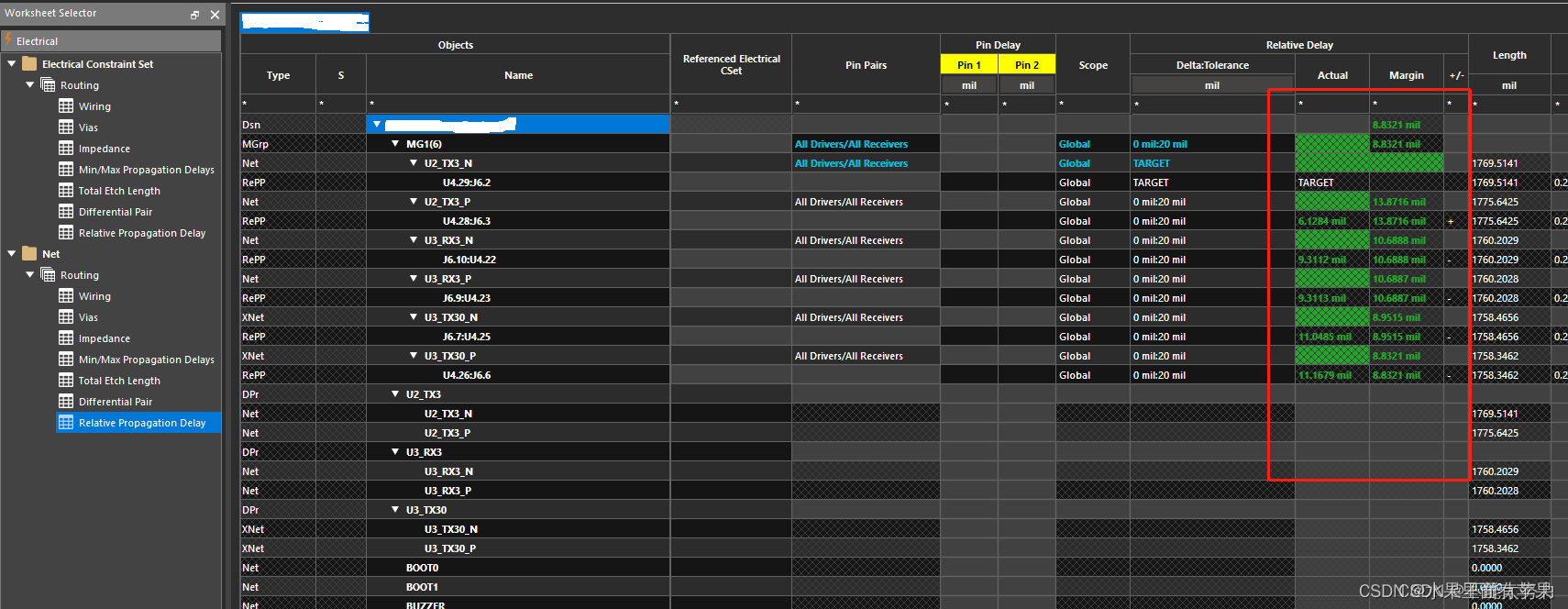

8.我们再回到constraint manager管理窗口,选择electrica->net->differential pair选项,并选择DSN后的工程文件,右击选择analyze选项,就可以在static phase下方看到当前的线长,以及匹配情况,如下图。绿色表示匹配OK 。

另外说明一下,static phase下方的actual为实际的长度差,margin是tolerance减去actual得到的剩余长度值。

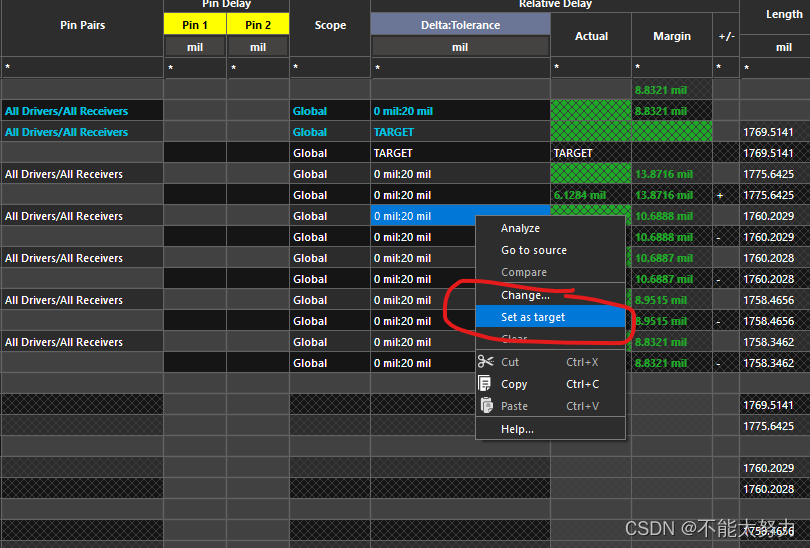

9.我们再回到electrica->relative propagation delay选项卡,按照同样的方式点击,也可以显示组间等长的匹配情况,另外在这里也可以设置某一个信号为TARFET,使得其他信号的长度都按照此信号的长度来进行匹配。

10.这里还差最后一步就是设置X-net属性。已经成功大半了,如果实际不需要X-NET设置的话,到此就可以愉快的布线了,不得不说allegro还是很强大很严谨的。废话不多少来完成最后一步的工作。

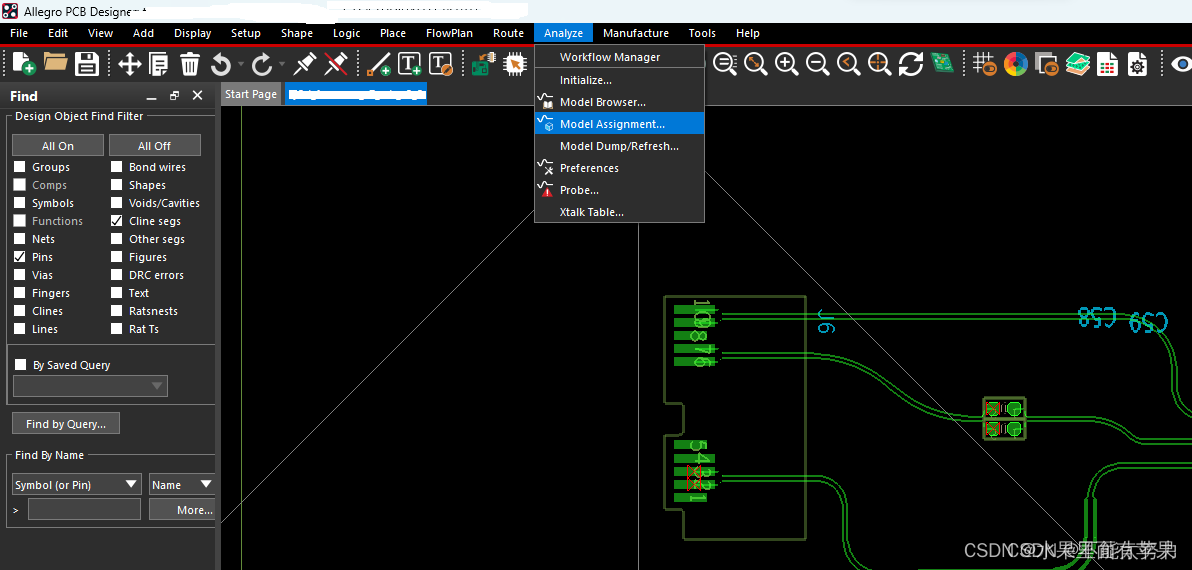

首先,高速信号的网络建立Xnet属性。点击analyze->model assignment,

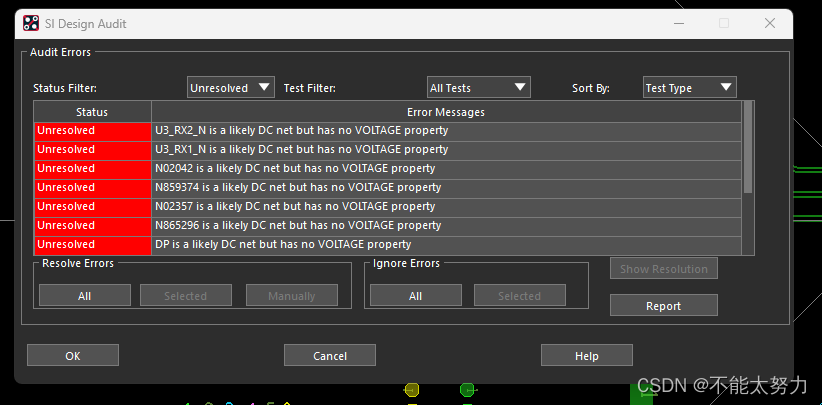

出现 si design audit,直接点击OK。这里会提示以下错误,有些没有电压值等,不用理会。

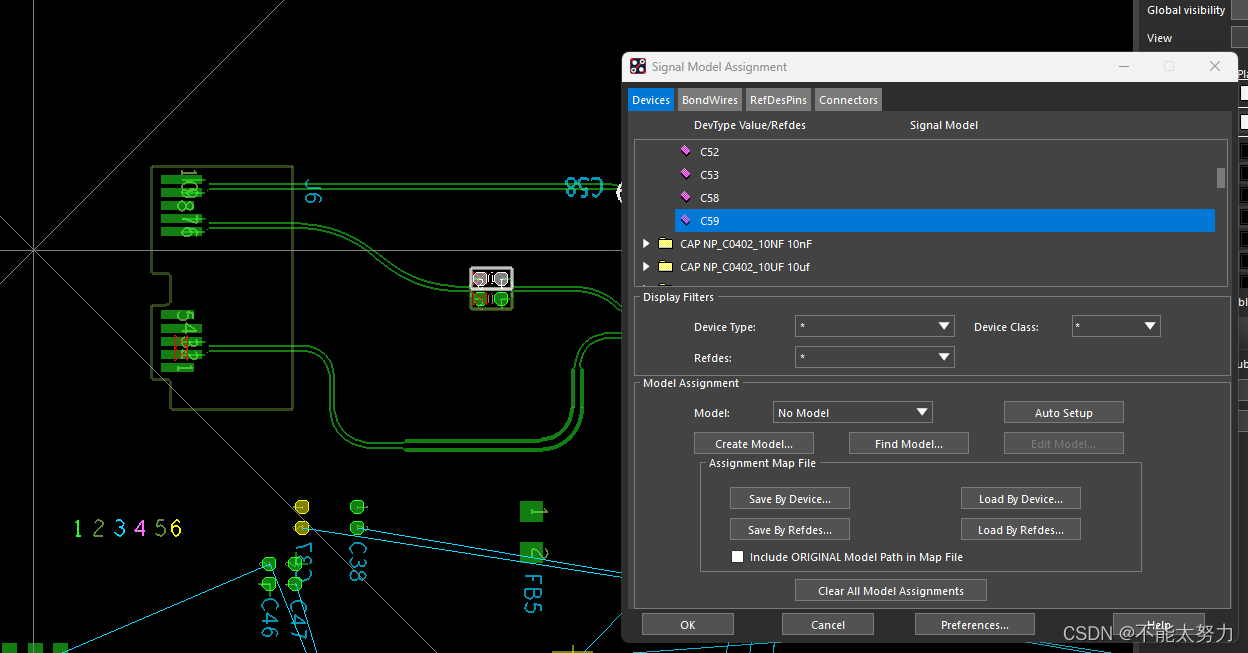

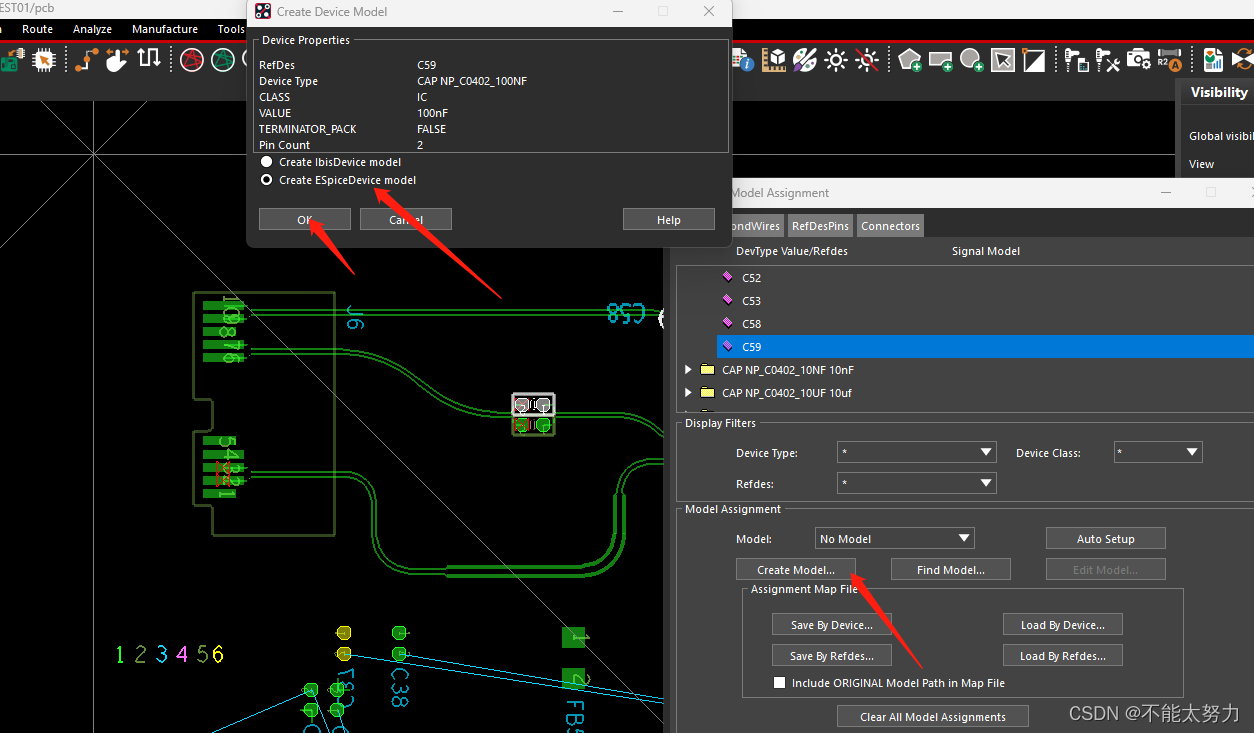

弹出signal model assignment窗口。在pcb中选中高速信号网络所经过的电阻,定位到此电阻。并点击create model。

回到规则管理器中,找到要分配的网络,右击选择pin pair,逐一选择好信号流向。

软件自动选择最长的线作为目标(target),一组中的其他线都以这个最长线的长度为标准,选中MGrp这一行,右键analysis,即可看到右侧其余线与最长线的差距。你也可以自行选择target。

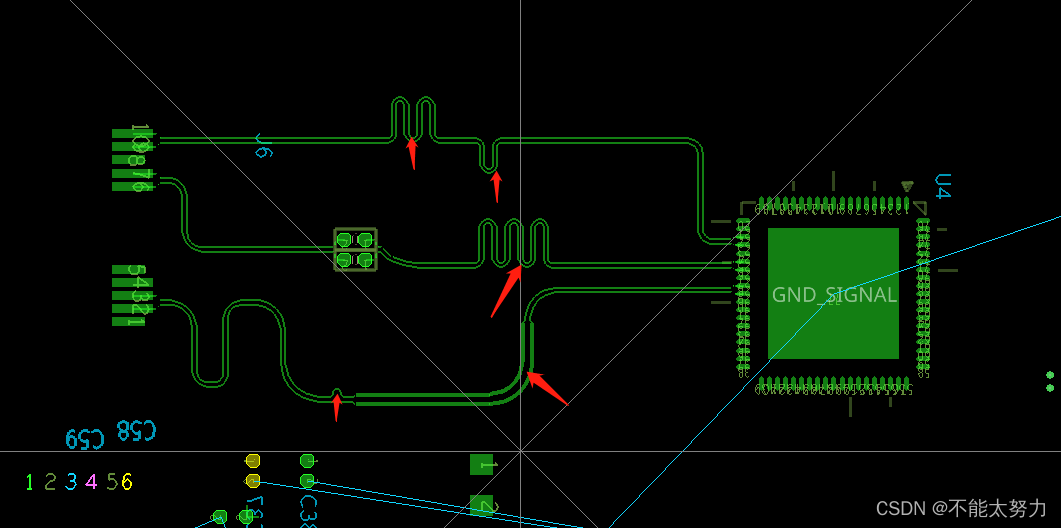

11.接下来回到layout窗口,去布线啦。如下图。

12.回到规则管理器中可以查看各个走线的长度值。

13.以上只是个人的理解,不代表官方说明,仅用于个人学习,不能用于商业用途。转载请附上原文出处链接及本声明。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删